#### **Bangor University**

#### **DOCTOR OF PHILOSOPHY**

Optical receiver design and optimisation for multi-gigahertz applications

Moreira, Paulo Manuel Rodrigues Simoes

Award date: 1993

Awarding institution: Bangor **University**

Link to publication

**General rights**Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal?

Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

Download date: 02. Apr. 2025

# Optical Receiver Design and Optimisation for Multi-Gigahertz Applications

Thesis Submitted in Candidature for the Degree of Doctor of Philosophy

November 1993

Paulo Manuel Rodrigues Simões Moreira

School of Electronic Engineering and Computer Systems

University of Wales

Bangor

United Kingdom

### Acknowledgments

I am very grateful to Professor John J. O'Reilly for taking me as his student and for his advice and motivation throughout the course of this study. I would also like to thank him for his support and guidance during the final preparation of this thesis.

I am very thankful to my friends Izzat Z. Darwazeh and Phil M. Lane for their help, encouragement, 'heated' discussions and continuous support and Henrique M. C. F. Salgado for useful discussions and his expert assistance with  $\LaTeX$ .

Thanks are also due to Paul Birdsall, Dr. Ian D. Henning and Dr. Dave J. Newson at BT-Laboratories for the collaboration and access to the InP-process. Also to Dr. Takis J. Hadjifotiou and Mark Kimber at BNR-Europe for helping with the packaging and test of the common-gate receiver.

Special thanks go to Dr. António P. Leite from the Universidade do Porto for his encouragement and belief and to Dr. José R. F. da Rocha for the help he gave me during a difficult period.

To Jú, my parents and Tomás I owe a great debt of gratitude for their support, understanding and belief.

I want also to express my gratitude to all my friends that contributed to make my stay in Bangor so enjoyable.

I am indebted to Instituto de Engenharia de Sistemas e Computadores (INESC-Norte) - Portugal for the financial support given during the initial phase of my work and to Junta Nacional de Investigação Científica e Tecnológica (JNICT) - Portugal for my scholarship.

## Summary

This thesis is concerned with structures and design techniques appropriate for the realisation of integrated optical receivers operating at multi-gigahertz frequencies. The development and practical proving of novel signal designs tailored specifically to very high bit-rate optical communication systems is reported. Timing imperfections and signal dependent noise - a result of the optical amplification deployed in all high-performance systems - are two major impairments that must be accommodated if optimum system performance is to be achieved. Here, a signal design that accommodates these impairments is developed and compared to established designs. The new signal designs are shown to provide improved performance, in particular, they exhibit tolerance to uncertainty in the exact level of the impairment.

Following the derivation of the signal designs a range of practical realisations are described. A receiver amplifier GaAs MMIC for 4.8 Gbit/s operation with embedded signal shaping is described followed by the design and test of integrated post-detection filters for 10 and 15 Gbit/s systems. The susceptibility of the embedded signal shaping receiver to variations in photodiode capacitance leads to the development and test of a low input-impedance common-gate 5 Gbit/s GaAs MMIC receiver. To effect signal shaping at very high data-rates a modified distributed amplifier structure is proposed which better utilises the capabilities of the available foundry processes. Two distributed amplifier based optical receivers with embedded signal shaping are devised and simulation results for 10 Gbit/s show the efficacy of this design approach. The implications of noise matching are investigated and a 2 GHz SCM receiver is used as a vehicle to illustrate the methods developed.

The long term goal of receiver design is to fully integrate both optical and electrical components onto a single chip. A preliminary investigation of the feasibility of this goal is carried out on an experimental InP-based process. Two receiver designs for 10 Gbit/s were prepared as a precursor to a detailed design of an OEIC with embedded signal shaping that incorporates the novel topologies developed during this work.

# Contents

| 1 | Intro | oduction 1                                                                 |    |  |

|---|-------|----------------------------------------------------------------------------|----|--|

|   | 1.1   | Receivers and signal processing for direct detection optical communication |    |  |

|   |       | systems                                                                    | 2  |  |

|   | 1.2   | Thesis organisation                                                        | 3  |  |

|   | 1.3   | Summary of main contributions                                              | 5  |  |

| 2 | Sign  | al shaping and noise filtering for optical communications                  | 9  |  |

|   | 2.1   | Signal shaping for PIN-receivers                                           | 9  |  |

|   |       | 2.1.1 Timing performance                                                   | 12 |  |

|   | 2.2   | Signal shaping for receivers dominated by signal dependent noise           | 12 |  |

|   |       | 2.2.1 Depressed threshold designs                                          | 16 |  |

|   | 2.3   | Depressed threshold designs with improved jitter tolerance                 | 19 |  |

|   |       | 2.3.1 Timing and signaling jitter                                          | 22 |  |

|   |       | 2.3.2 Receiver noise and sensitivity                                       | 23 |  |

|   | 2.4   | The MCB-based approach to signal design                                    | 32 |  |

|   | 2.5   | Time domain optimisation of post-detection realisable filters              | 35 |  |

|   |       | 2.5.1 Time domain response and cost function                               | 36 |  |

|   |       | 2.5.2 Optimisation process and results                                     | 38 |  |

|   | 2.6   | Summary                                                                    | 43 |  |

| 3 | GaA   | s technology and noise modelling                                           | 45 |  |

|   | 3.1   | The GaAs foundry process                                                   | 46 |  |

|   | 3.2   | Device modelling                                                           | 47 |  |

|   |       | 3.2.1 Passive devices                                                      | 47 |  |

|   |       | 3.2.2 Active devices                                                       | 52 |  |

|   | 3.3   | Noise modelling                                                            | 54 |  |

|   |       | 3.3.1 The MESFET noise model                                               | 55 |  |

| CONTENTS | <br> | <u></u> | <u>i</u> |

|----------|------|---------|----------|

|          |      |         |          |

|   |      | 3.3.2   | Noise analysis                                      | 59  |

|---|------|---------|-----------------------------------------------------|-----|

|   |      | 3.3.3   | Noise de-embedding                                  | 61  |

|   |      | 3.3.4   | Results and method validation                       | 63  |

|   | 3.4  | MATL    | AB Toolbox: Circuit Analysis                        | 65  |

|   | 3.5  | Summ    | ary                                                 | 67  |

| 4 | Pseu | ıdo-lur | nped-element GaAs receivers for binary signalling   | 68  |

|   | 4.1  | GaAs    | receiver with embedded signal shaping               | 69  |

|   |      | 4.1.1   | Receiver target response                            | 70  |

|   |      | 4.1.2   | Receiver design                                     | 71  |

|   |      | 4.1.3   | Optimisation and simulation results                 | 72  |

|   | 4.2  | Comm    | non-gate optical receivers                          | 75  |

|   |      | 4.2.1   | Low input impedance receivers                       | 76  |

|   |      | 4.2.2   | Receiver design                                     | 78  |

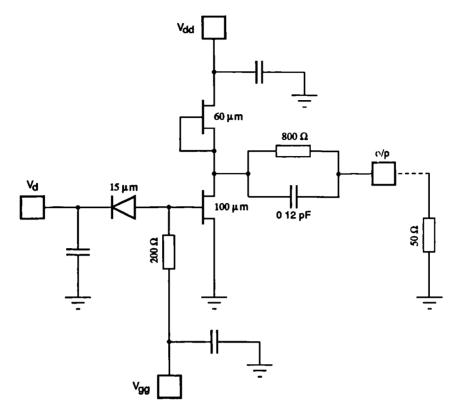

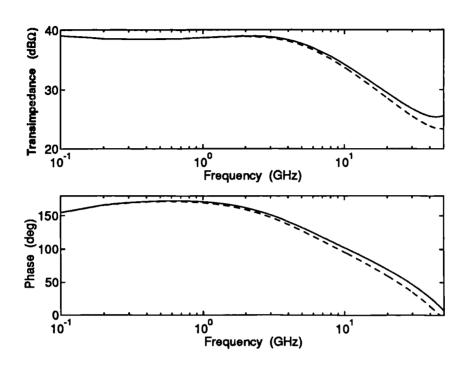

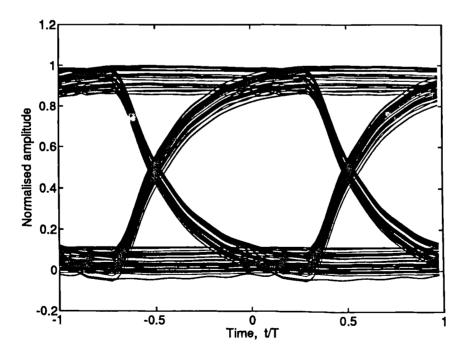

|   |      | 4.2.3   | Simulation and experimental results                 | 80  |

|   | 4.3  | Separa  | ate pseudo-lumped signal shaping networks           | 84  |

|   |      | 4.3.1   | The direct time domain optimisation method          | 85  |

|   |      | 4.3.2   | 10 and 15 Gbit/s post-detection filters             | 90  |

|   | 4.4  | Summ    | nary                                                | 96  |

| 5 | Dist | ribute  | d amplifier signal shaping strategy                 | 98  |

|   | 5.1  | Additi  | ive amplification                                   | 99  |

|   |      | 5.1.1   | The distributed amplifier                           | 99  |

|   |      | 5.1.2   | Distributed optical receivers                       | 102 |

|   |      | 5.1.3   | 16.4 GHz GaAs MMIC distributed optical receiver     | 103 |

|   | 5.2  | The d   | istributed amplifier as a transversal filter        | 107 |

|   |      | 5.2.1   | Alternative structures                              | 110 |

|   |      | 5.2.2   | Design examples                                     | 113 |

|   | 5.3  | Summ    | nary                                                | 118 |

| 6 | Elec | tronic  | noise minimisation for optical receivers            | 119 |

|   | 6.1  | Noise   | matched receivers                                   | 119 |

|   |      | 6.1.1   | Front end selection                                 | 122 |

|   |      | 6.1.2   | Optimum noise matching                              | 122 |

|   |      | 6.1.3   | Active device selection and optimum bias conditions | 126 |

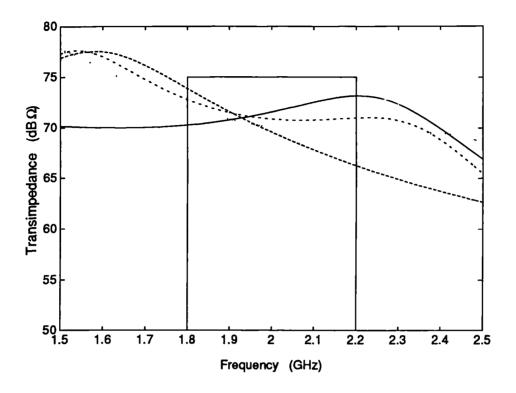

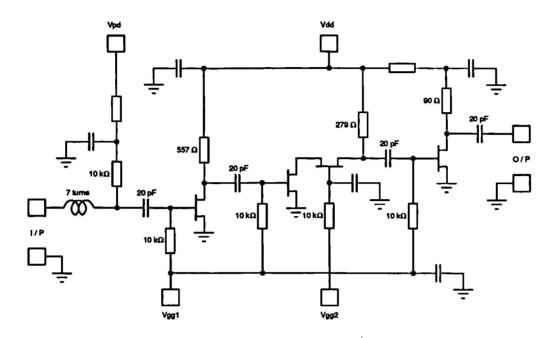

|              | 6.2                                | SCM (   | GaAs receiver with integrated tuning network               | 127 |  |

|--------------|------------------------------------|---------|------------------------------------------------------------|-----|--|

|              |                                    | 6.2.1   | Noise tuning networks                                      | 127 |  |

|              |                                    | 6.2.2   | Receiver optimisation                                      | 130 |  |

|              |                                    | 6.2.3   | Simulation results                                         | 132 |  |

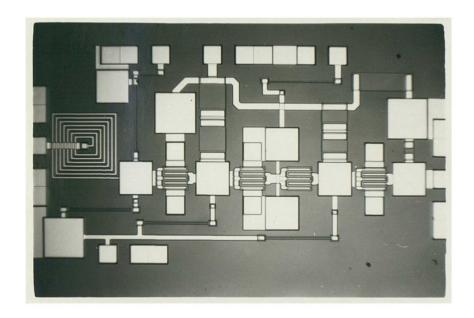

|              |                                    | 6.2.4   | Practical implementation                                   | 133 |  |

|              | 6.3                                | Summ    | ary                                                        | 136 |  |

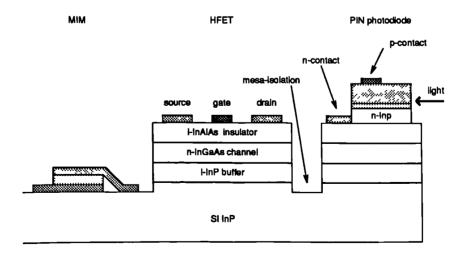

| 7            | Preli                              | iminar  | y considerations for the realisation of InP OEIC receivers | 137 |  |

|              | 7.1                                | The B   | TL-InP process                                             | 138 |  |

|              |                                    | 7.1.1   | InGaAs doped channel HFETs                                 | 139 |  |

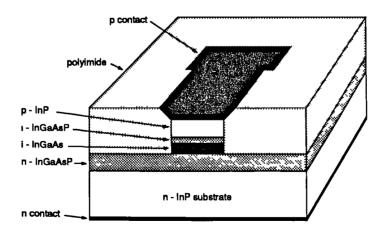

|              |                                    | 7.1.2   | InGaAs edge-coupled PINs                                   | 140 |  |

|              | 7.2                                | 10 Gbi  | t/s evaluation designs                                     | 141 |  |

|              |                                    | 7.2.1   | Single stage high impedance OEIC receiver                  | 142 |  |

|              |                                    | 7.2.2   | Two stage high impedance OEIC receiver                     | 145 |  |

|              |                                    | 7.2.3   | Test structures                                            | 145 |  |

|              | 7.3                                | Summ    | ary                                                        | 147 |  |

| 8            | Con                                | cluding | g remarks                                                  | 148 |  |

| $\mathbf{A}$ | ppen                               | dices   |                                                            | 153 |  |

| A            | New                                | class   | of waveforms for binary optical transmission               | 153 |  |

| В            | Deri                               | vation  | of equations (2.76), (2.77) and (2.78)                     | 156 |  |

| $\mathbf{C}$ | C MATLAB Toolbox: Circuit Analysis |         |                                                            |     |  |

| $\mathbf{R}$ | efere                              | nces    |                                                            | 165 |  |

# List of Figures

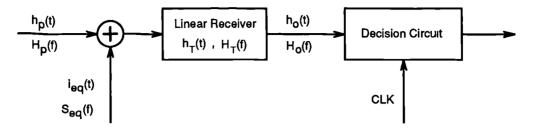

| 2.1  | Optical receiver system model                                                               | 10 |

|------|---------------------------------------------------------------------------------------------|----|

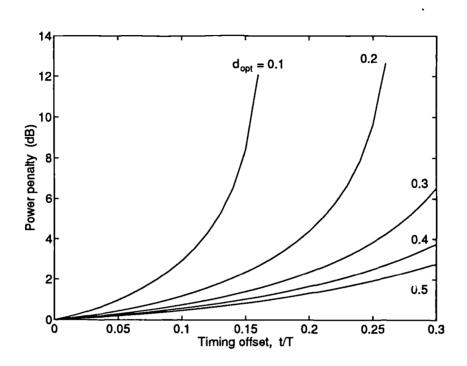

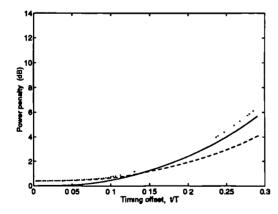

| 2.2  | RC power penalty versus timing offset for different values of $d_{opt}$                     | 15 |

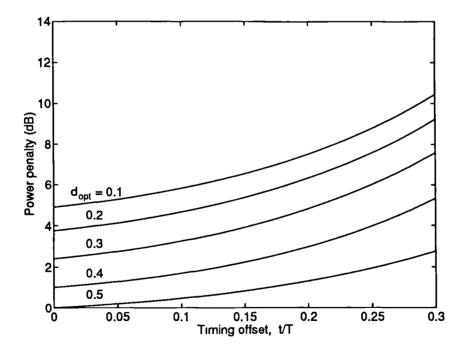

| 2.3  | RC power penalty versus timing offset for different values of $d_{opt}$ when the            |    |

|      | decision level is set at 50%                                                                | 15 |

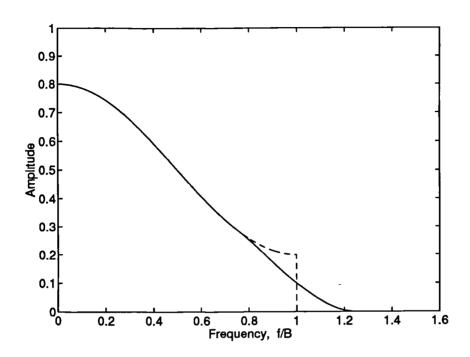

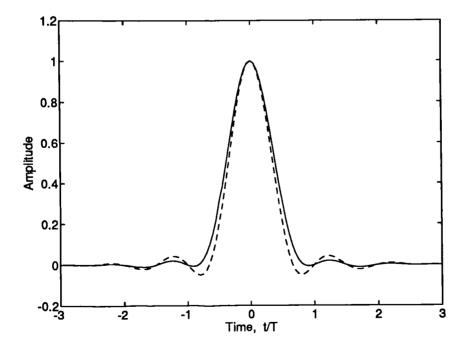

| 2.4  | Pulse spectrum for $d=0.3$ : '' $\alpha=0$ , '' $\alpha=0.25$                               | 18 |

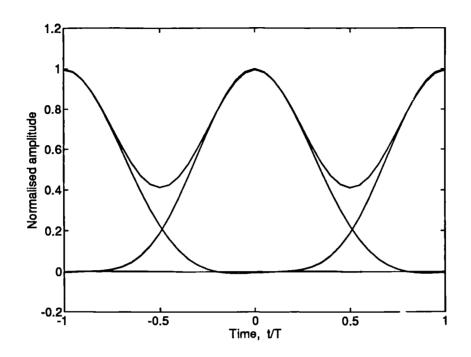

| 2.5  | Pulse shapes: '' $d=0.3$ and $\alpha=0.25,$ '' $d=0.2$ and $\alpha=0.3$ .                   | 18 |

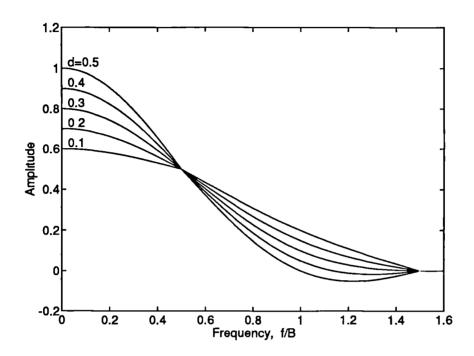

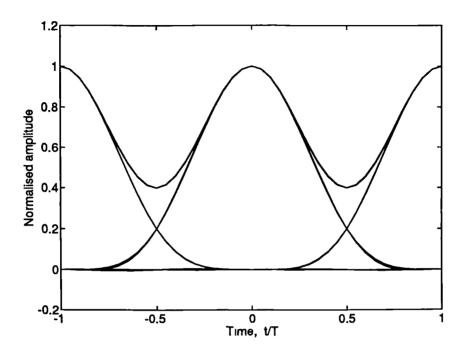

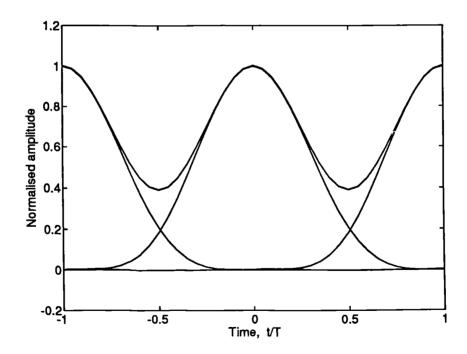

| 2.6  | Pulse spectrum for different values of $d$                                                  | 21 |

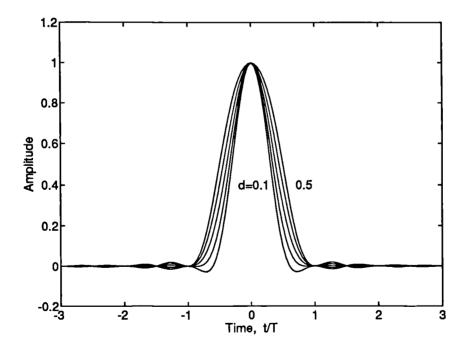

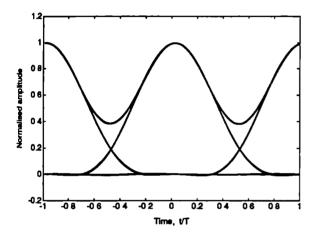

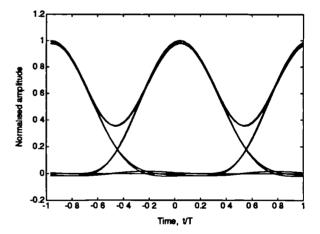

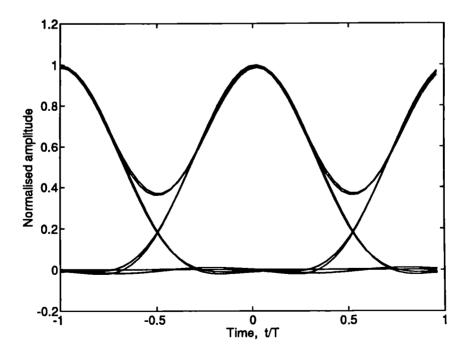

| 2.7  | Pulse shape for different values of $d$                                                     | 21 |

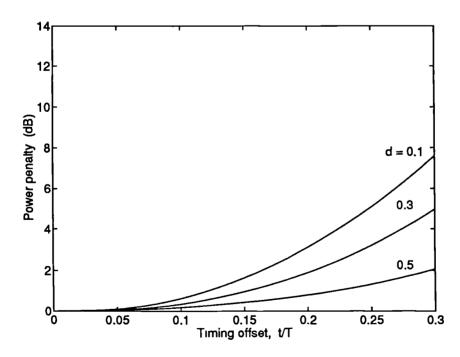

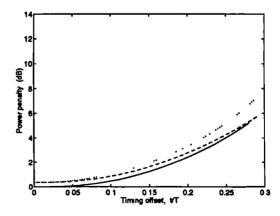

| 2.8  | NSD power penalty versus timing offset for different values of $d$                          | 22 |

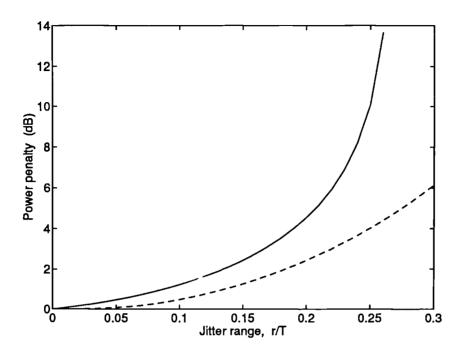

| 2.9  | Power penalty versus $r$ for $d_{opt} = 0.2$ : '' RC; '' NSD                                | 23 |

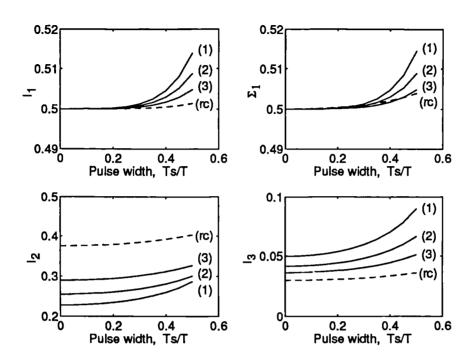

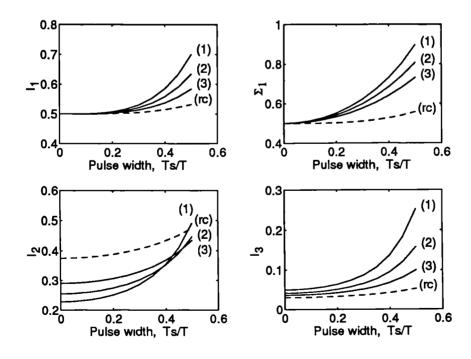

| 2.10 | Personick noise integrals versus pulse width for rectangular input pulse: (1)               |    |

|      | d = 0.1; (2) $d = 0.2$ ; (3) $d = 0.3$                                                      | 25 |

| 2.11 | Personick noise integrals versus pulse width for soliton input pulse: (1)                   |    |

|      | d = 0.1; (2) $d = 0.2$ ; (3) $d = 0.3$                                                      | 25 |

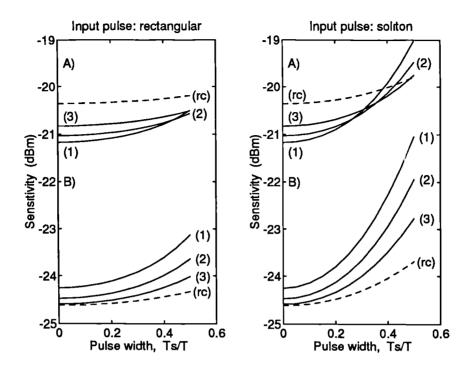

| 2.12 | Electronic receiver sensitivity versus pulse width for A) $R_{in} = 50 \Omega$ and B)       |    |

|      | $R_{in} = 470 \Omega$ : (1) NSD $d = 0.1$ ; (2) NSD $d = 0.2$ ; (3) NSD $d = 0.3$ ; (rc) RC | 27 |

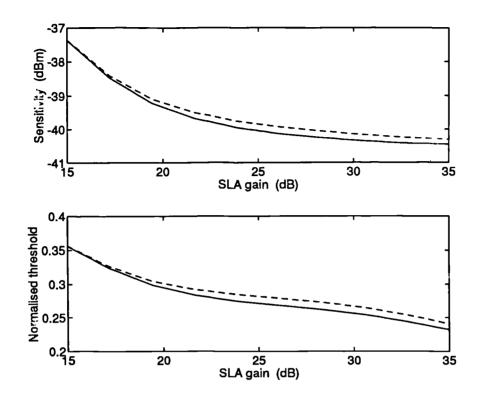

| 2.13 | Sensitivity and optimum decision level versus optical gain: '' NSD; ''                      |    |

|      | RC                                                                                          | 30 |

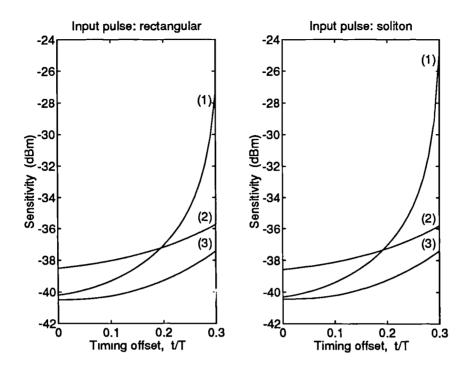

| 2.14 | Sensitivity versus timing offset: (1) optimised RC; (2) RC with 50% decision                |    |

|      | level; (3) NSD                                                                              | 31 |

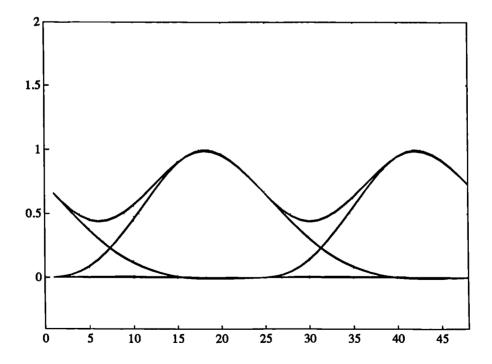

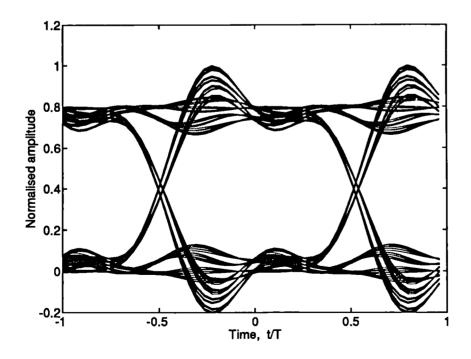

| 2.15 | Eye-diagram for an MCB optimised APD receiver ([50], chapter 6)                             | 34 |

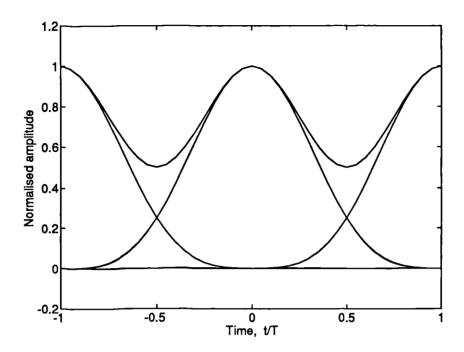

| 2.16 | NSD eye-diagram $d=0.25$                                                                    | 35 |

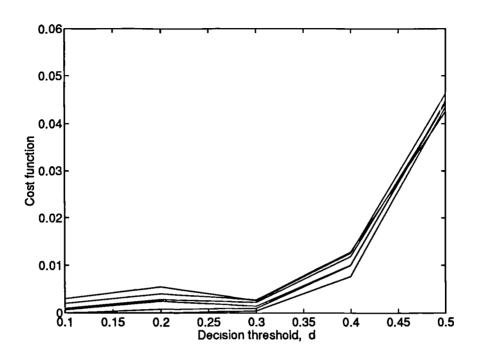

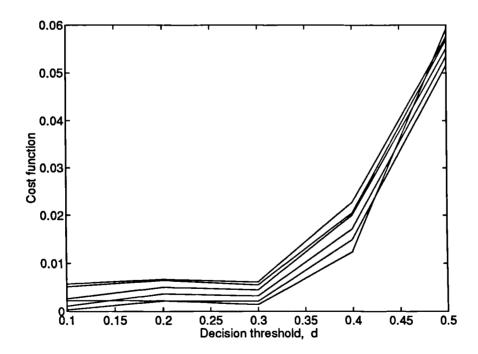

| 2.17 | Optimum filter cost function vs. $l$ for different values of $T_s$ and $N=7$                | 40 |

| 2.18 | Optimised bandwidth Thomson filter cost function vs $d$ for different values                |    |

|      | of $T_s$ and $N=7$                                                                          | 40 |

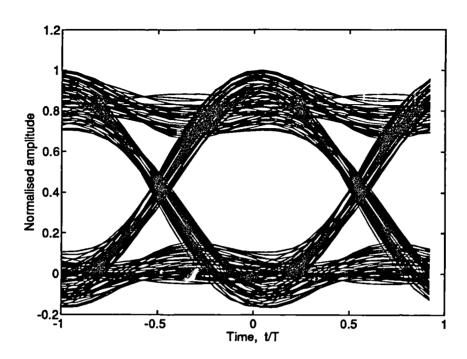

| 2.19 | NSD eye-diagram for $d=0.2\ldots\ldots$                                                     | 41 |

| 2.20 | Optimum filter eye-diagram for $d = 0.2$ and $T_s = 0.5$                           | 41        |

|------|------------------------------------------------------------------------------------|-----------|

| 2.21 | Thomson optimised filter eye-diagram for $d=0.2$ and $T_s=0.5$                     | 42        |

| 2.22 | Filter transfer function for $d=0.2$ and $T_s=0.5$ , NSD: ''; optimum:             |           |

|      | ''; Thomson ''                                                                     | 42        |

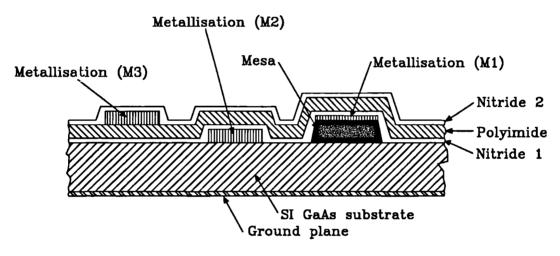

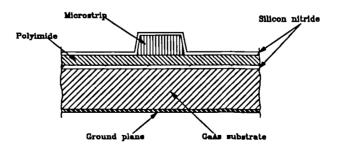

| 3.1  | GaAs MMIC cross-sectional view                                                     | 46        |

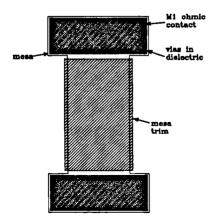

| 3.2  | Mesa resistor layout                                                               | 47        |

| 3.3  | Mesa resistor model                                                                | 47        |

| 3.4  | MIM capacitor layout                                                               | 48        |

| 3.5  | MIM capacitor model                                                                | 48        |

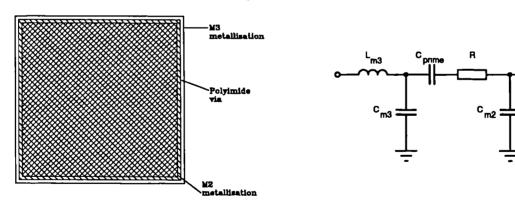

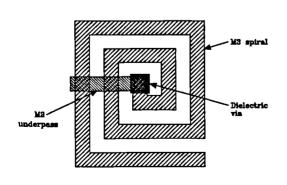

| 3.6  | Spiral inductor layout                                                             | 49        |

| 3.7  | Spiral inductor model                                                              | 49        |

| 3.8  | Cross-section of a M3 microstrip transmission line                                 | 50        |

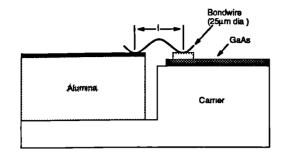

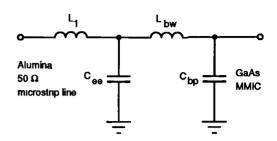

| 3.9  | MMIC/Alumina transition                                                            | <b>52</b> |

| 3.10 | MMIC/Alumina transition model                                                      | <b>52</b> |

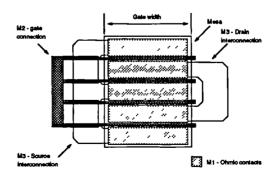

| 3.11 | Four finger MESFET layout                                                          | <b>52</b> |

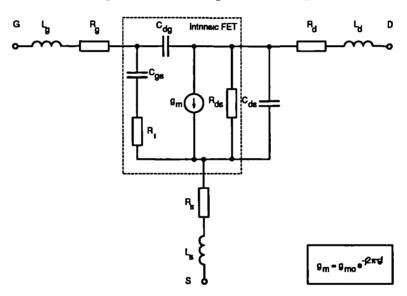

| 3.12 | MESFET equivalent circuit                                                          | 53        |

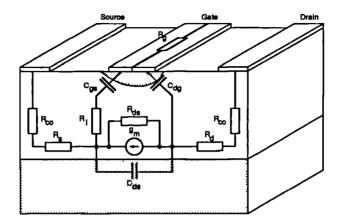

| 3.13 | Physical origin of the MESFET equivalent circuit                                   | 54        |

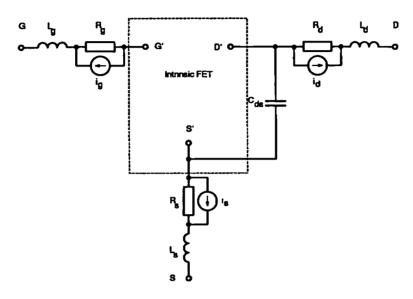

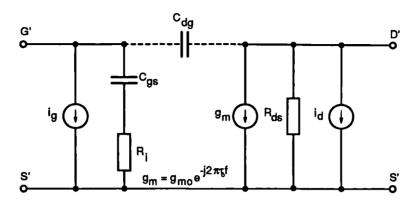

| 3.14 | Extrinsic FET noise model                                                          | 56        |

| 3.15 | Intrinsic FET noise model                                                          | 57        |

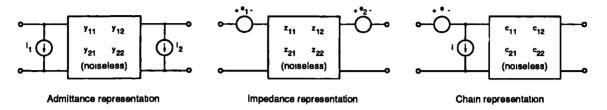

| 3.16 | Two-port noise models                                                              | 60        |

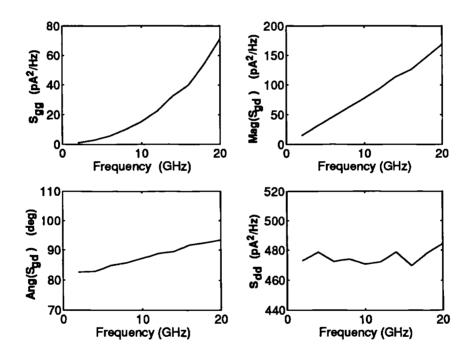

| 3.17 | Frequency behaviour of the $C_Y$ -matrix elements for the $4 \times 150$ intrinsic |           |

|      | MESFET                                                                             | 64        |

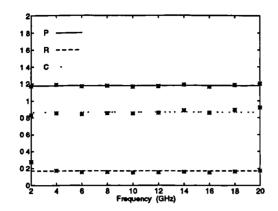

| 3.18 | De-embedded $P$ , $R$ , and $C$ values for the $4 \times 150$ MESFET               | 65        |

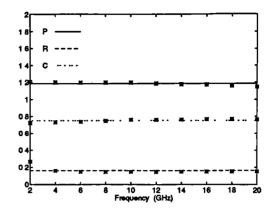

| 3.19 | De-embedded $P$ , $R$ , and $C$ values for the $2 \times 100$ MESFET               | 65        |

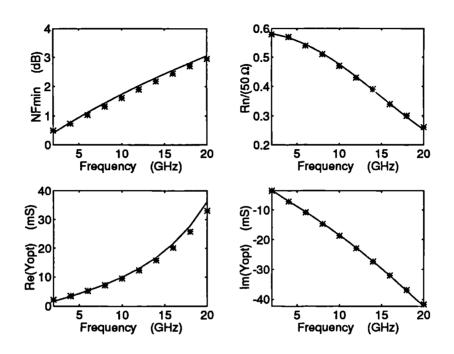

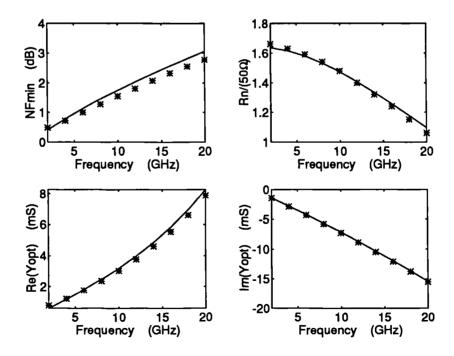

| 3.20 | Measured ('*') and predicted ('-') noise parameters for the $4 \times 150$ MESFET  | 66        |

| 3.21 | Measured ('*') and predicted ('-') noise parameters for the 2 × 100 MESFET         | 66        |

|      |                                                                                    |           |

| 4.1  | MCB optimised filter, ref. [50]                                                    | 71        |

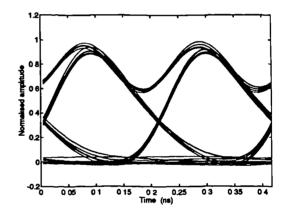

| 4.2  | Receiver target eye-diagram                                                        | 71        |

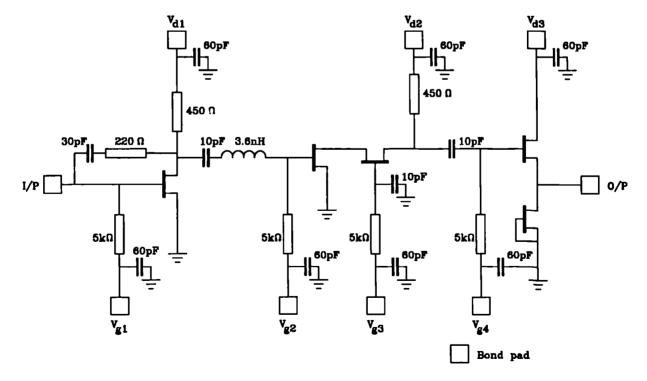

| 4.3  | Optical receiver schematic diagram                                                 | 71        |

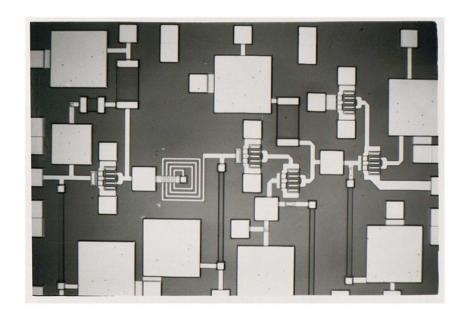

| 4.4  | Receiver photomicrograph                                                           | 72        |

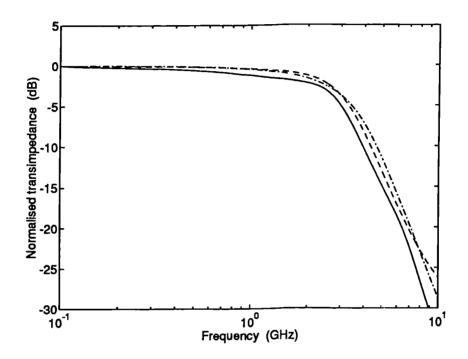

| 4.5  | Receiver frequency response: '' final MMIC; '- · -' with ideal pas-                |           |

|      | sives; '' target                                                                   | 74        |

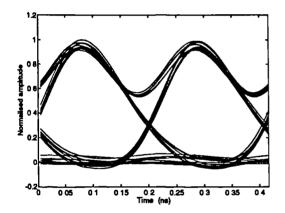

| 4.6  | Eye-diagram $C_d=0.3\mathrm{pF}$ and $L_{bw}=1\mathrm{nH}$                                 | 75 |

|------|--------------------------------------------------------------------------------------------|----|

| 4.7  | Eye-diagram $C_d=0.5\mathrm{pF}$ and $L_{bw}=1\mathrm{nH}$                                 | 75 |

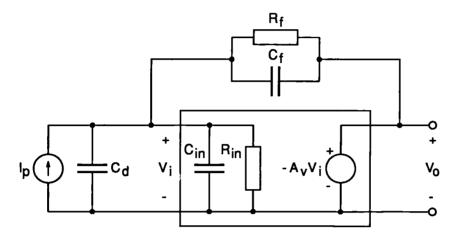

| 4.8  | Transimpedance optical receiver model                                                      | 77 |

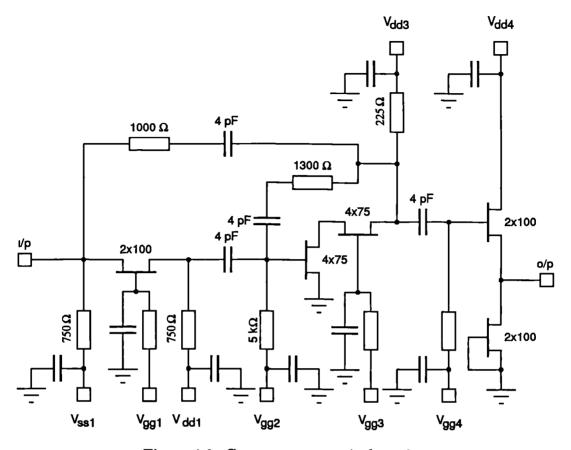

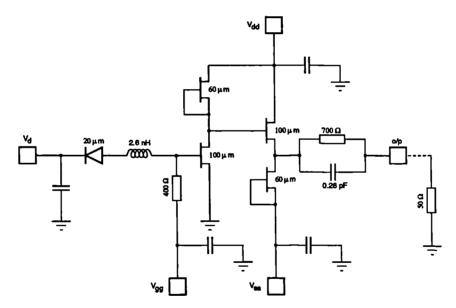

| 4.9  | Common-gate optical receiver                                                               | 79 |

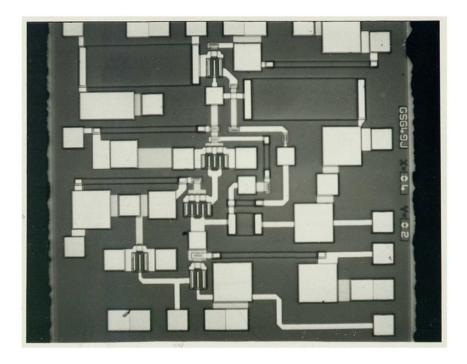

| 4.10 | Receiver photomicrograph                                                                   | 80 |

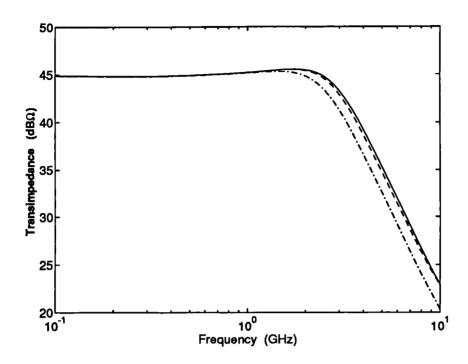

| 4.11 | Simulated receiver response: '' $C_d = 0.1  \mathrm{pF}$ , '' $C_d = 0.2  \mathrm{pF}$ and |    |

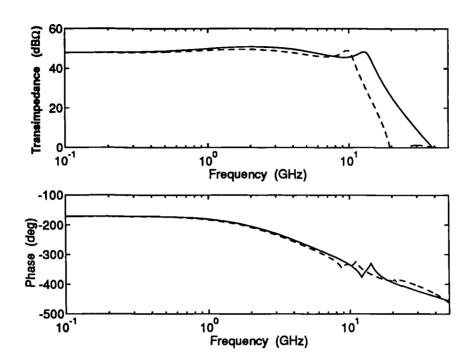

|      | '' $C_d=0.5\mathrm{pF}$                                                                    | 81 |

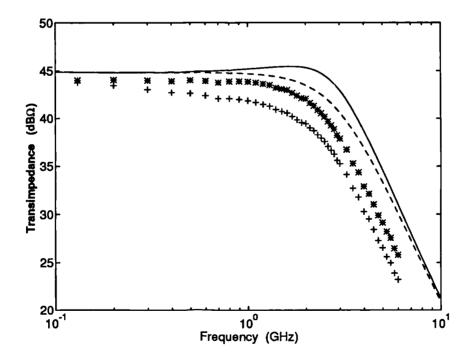

| 4.12 | CG receiver response: '+' measured, '*' corrected for PIN response, ''                     |    |

|      | simulated with $C_d=0.15\mathrm{pF}$ and '' simulated with added feedback ca-              |    |

|      | pacitances                                                                                 | 81 |

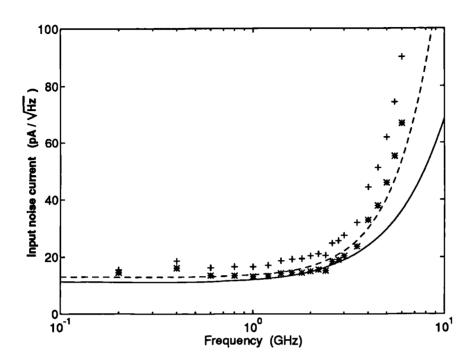

| 4.13 | Equivalent input noise current spectral density: '+' measured for the re-                  |    |

|      | ceiver with a 7 dB NF post-amplifier, '*' corrected for PIN response, ''                   |    |

|      | simulated and '' simulated for the receiver only                                           | 83 |

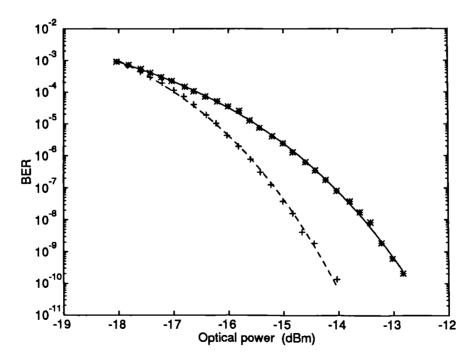

| 4.14 | Optical sensitivity: '*' $2^7 - 1$ PBRS and '+' '0101' pattern                             | 83 |

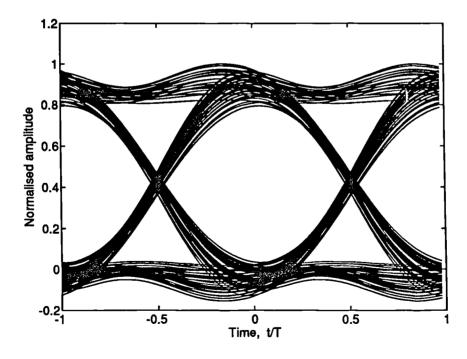

| 4.15 | Measured eye-diagram ( $B=5\mathrm{Gbit/s},\ P=-17\mathrm{dBm}$ )                          | 84 |

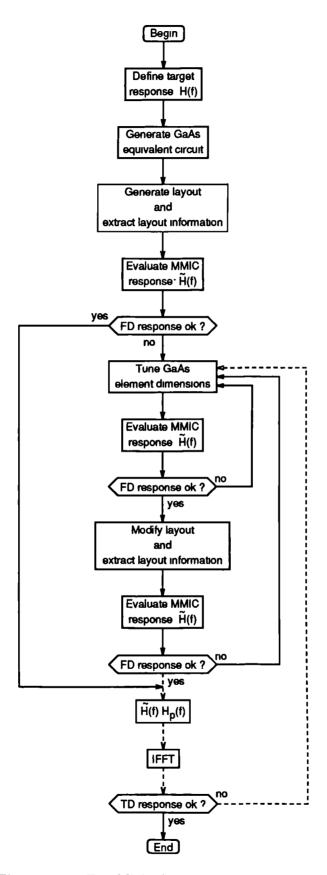

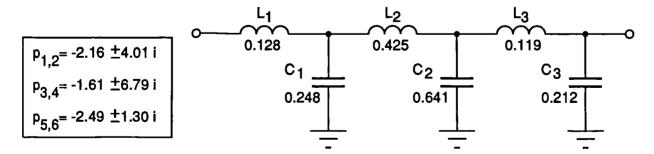

| 4.16 | Established optimisation procedure                                                         | 86 |

| 4.17 | Time domain optimisation procedure                                                         | 89 |

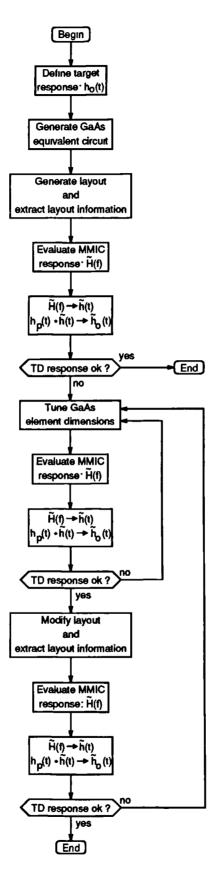

| 4.18 | Ideal lumped element filter and normalised pole positions                                  | 90 |

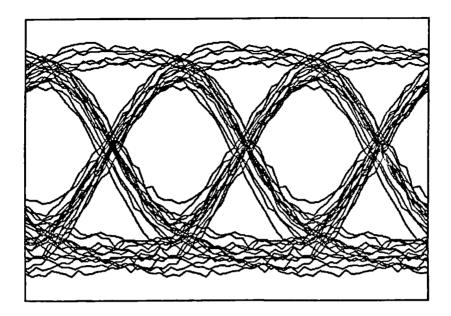

| 4.19 | Eye-diagram of the ideal lumped element network                                            | 92 |

| 4.20 | Eye-diagram of the unoptimised GaAs network                                                | 92 |

| 4.21 | Eye-diagram after conventional frequency domain optimisation                               | 92 |

| 4.22 | Eye-diagram after the proposed time domain optimisation                                    | 92 |

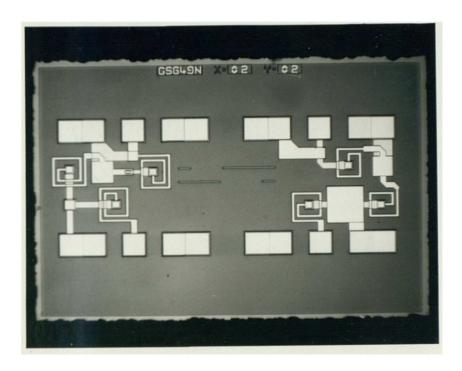

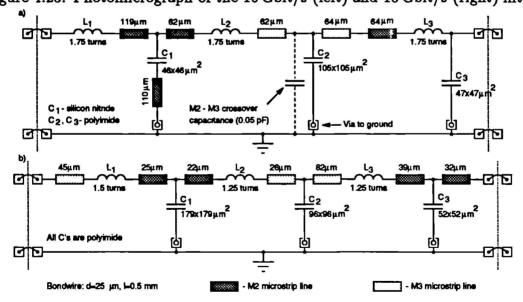

| 4.23 | Photomicrograph of the 10 Gbit/s (left) and 15 Gbit/s (right) filters                      | 93 |

| 4.24 | GaAs filters, extracted layout: a) 10 Gbit/s and b) 15 Gbit/s                              | 93 |

| 4.25 | 10 Gbit/s GaAs filter frequency response: '' predicted, '' measured.                       | 94 |

| 4.26 | 15 Gbit/s GaAs filter frequency response: '' predicted, '' measured.                       | 94 |

| 4.27 | 10 Gbit/s eye-diagram                                                                      | 95 |

| 4.28 | 15 Gbit/s eye-diagram                                                                      | 95 |

| 4.29 | Power penalty versus timing offset for the 10 Gbit/s filter: '' negative                   |    |

|      | and '····' positive timing offsets, '——' new signal design with $d=0.2$                    | 95 |

| 4.30 | Power penalty versus timing offset for the 15 Gbit/s filter: '' negative                   |    |

|      | and ' $\cdots$ ' positive timing offsets, ' $$ ' new signal design with $d=0.2$            | 95 |

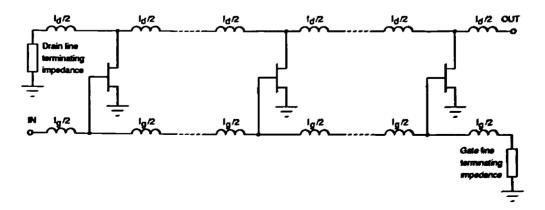

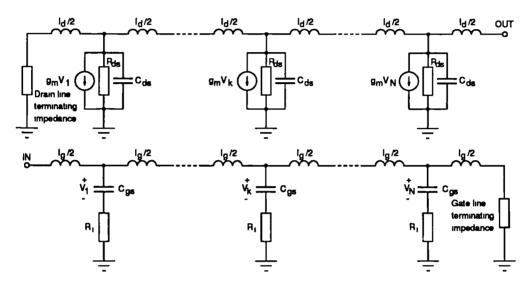

| 5.1  | Distributed amplifier                                                                | 99  |

|------|--------------------------------------------------------------------------------------|-----|

| 5.2  | Simplified model of a distributed amplifier                                          | 100 |

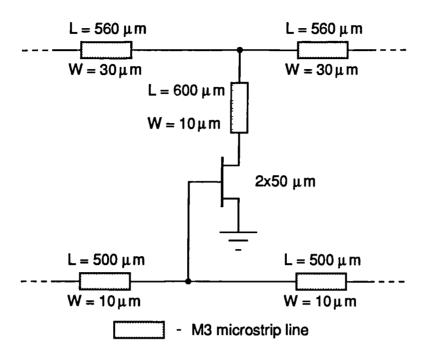

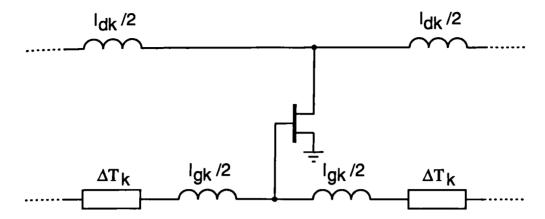

| 5.3  | Single stage of the distributed optical receiver                                     | 104 |

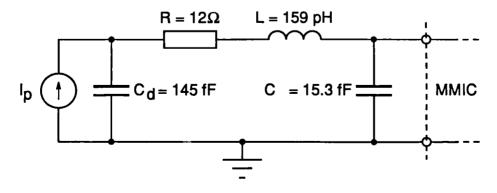

| 5.4  | PIN and PIN/MMIC transition equivalent circuit                                       | 104 |

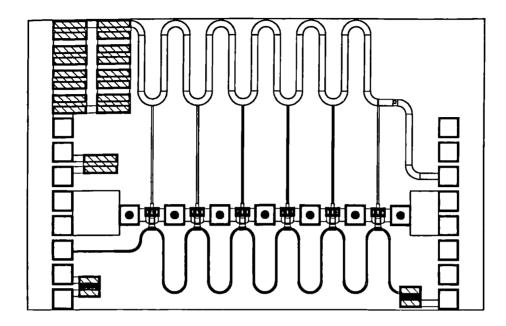

| 5.5  | Distributed receiver layout                                                          | 105 |

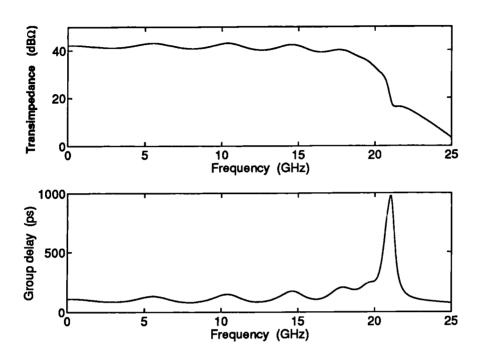

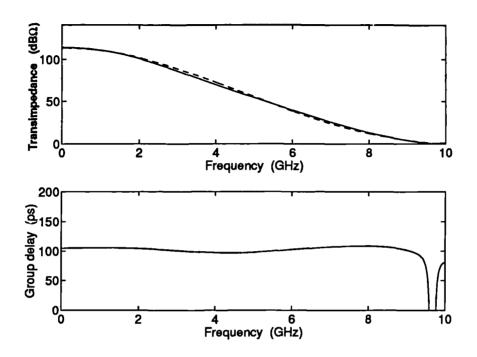

| 5.6  | Distributed receiver transimpedance and group delay                                  | 106 |

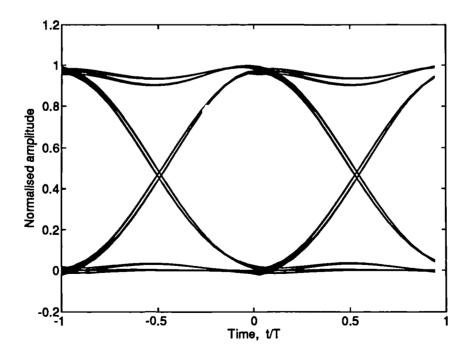

| 5.7  | 10 Gbit/s eye-diagram                                                                | 106 |

| 5.8  | 20 Gbit/s eye-diagram                                                                | 107 |

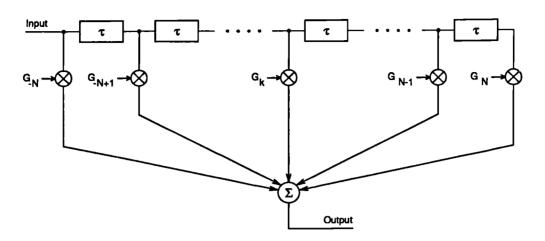

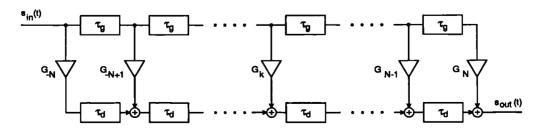

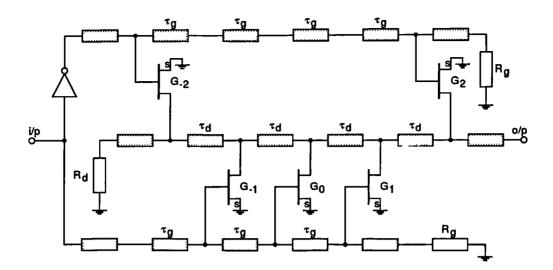

| 5.9  | Transversal filter                                                                   | 108 |

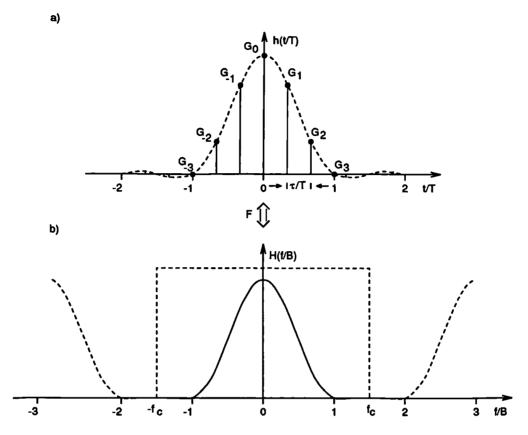

| 5.10 | Functional equivalent of a $2N+1$ stage distributed amplifier                        | 108 |

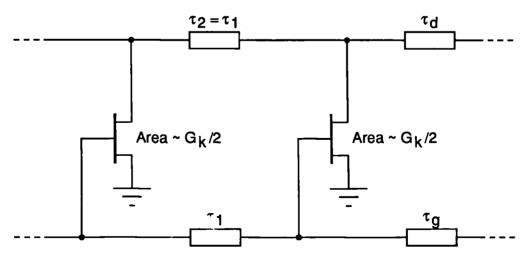

| 5.11 | Single section of the 'distributed transversal filter'                               | 110 |

| 5.12 | Determination of gain coefficients a), transmission line cutoff frequency b)         | 111 |

| 5.13 | Microwave transversal filter with both positive and negative gain coefficients       | 112 |

| 5.14 | Gain sharing between two MESFETs                                                     | 112 |

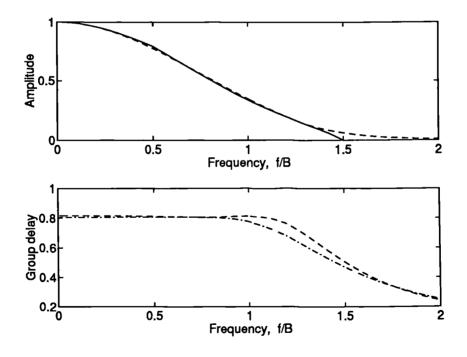

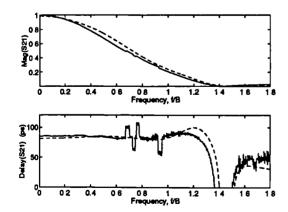

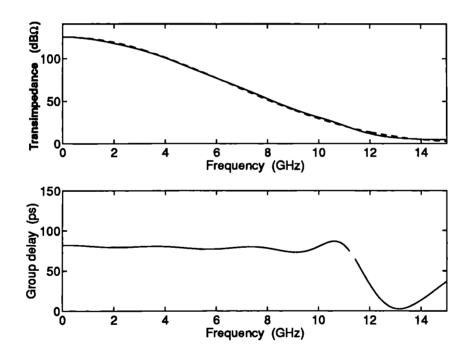

| 5.15 | Raised cosine receiver transimpedance gain and group delay, '' simulated             |     |

|      | response, '-·-' target response                                                      | 115 |

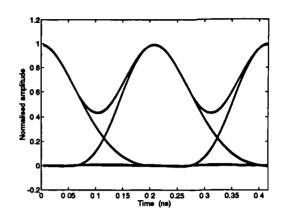

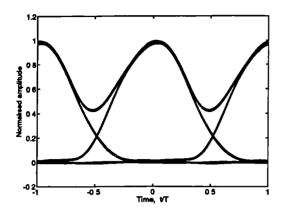

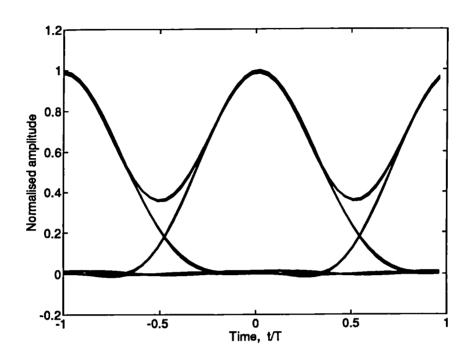

| 5.16 | Raised cosine receiver simulated eye diagram                                         | 115 |

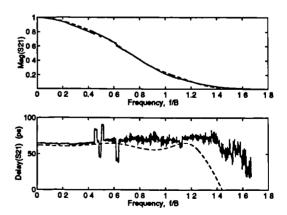

| 5.17 | New signal design receiver transimpedance gain and group delay, '' sim-              |     |

|      | ulated response, '-·-' target response                                               | 116 |

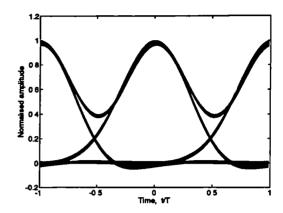

| 5.18 | New signal design distributed receiver simulated eye diagram                         | 117 |

| 5.19 | New signal design post-detection filter simulated eye diagram                        | 117 |

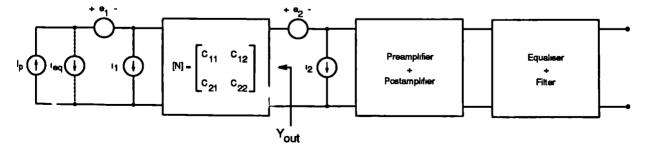

| 6.1  | Optical receiver noise model                                                         | 120 |

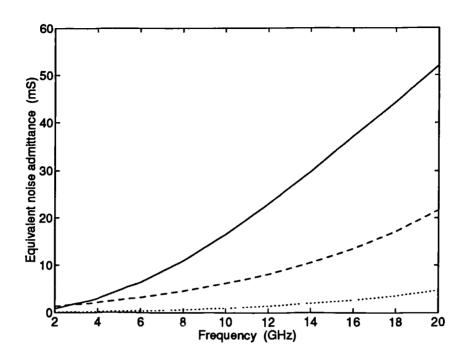

| 6.2  | Equivalent noise admittance for three matching situations: ('') no match-            |     |

|      | ing, (' ') matching to $Y_{opt}$ and ('') matching to $j \operatorname{Im}(Y_{opt})$ | 125 |

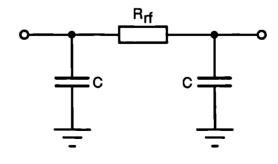

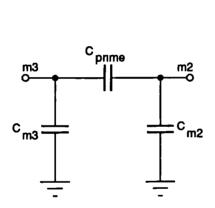

| 6.3  | Simplified GaAs capacitor equivalent circuit                                         | 128 |

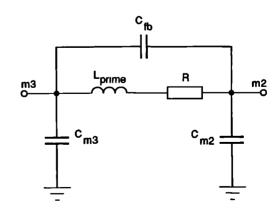

| 6.4  | Simplified GaAs inductor equivalent circuit                                          | 128 |

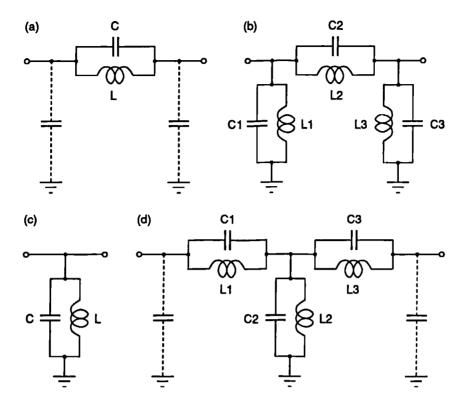

| 6.5  | Simplified models for the GaAs implementation of: (a) Series tuning, (b) II          |     |

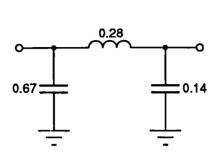

| •••  | tuning, (c) shunt tuning and (d) T tuning                                            | 129 |

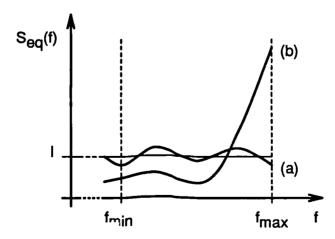

| 6.6  | Two possible outcomes of $S_{eq}(f)$ optimisation: (a) Conditions set by equa-       |     |

|      | tions (6.39) and (6.40) considered and (b) Condition set by equation (6.40)          |     |

|      | ignored                                                                              | 131 |

|      |                                                                                      |     |

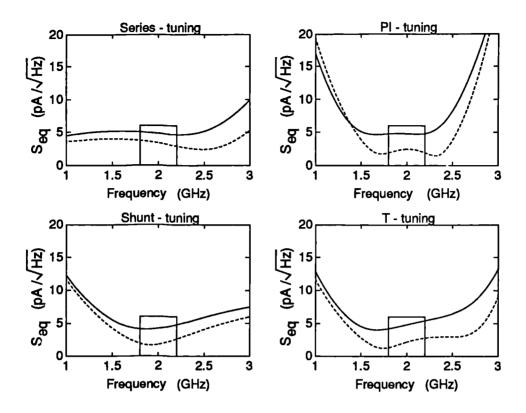

| 6.7  | Optimised $S_{eq}(f)$ for different tuning networks: '' full GaAs models |     |

|------|--------------------------------------------------------------------------|-----|

|      | and '' equation (6.28) $\dots$                                           | 132 |

| 6.8  | Transimpedance gain for different tuning networks: '' series tuning,     |     |

|      | '' shunt tuning, '' $\Pi$ tuning and '' $T$ tuning                       | 134 |

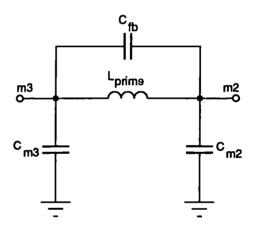

| 6.9  | Tuned receiver schematic                                                 | 135 |

| 6.10 | Tuned receiver photomicrograph                                           | 135 |

| 7.1  | General InP OEIC structure                                               | 138 |

| 7.2  | Schematic representation of the HFET layer structure                     | 139 |

| 7.3  | Edge-coupled InGaAs PIN structure                                        | 140 |

| 7.4  | Single stage InP OEIC receiver schematic diagram                         | 143 |

| 7.5  | Single stage OEIC receiver frequency response: '—' ideal passives compo- |     |

|      | nents, '' passives with added parasitics                                 | 144 |

| 7.6  | Single stage OEIC eye-diagram                                            | 144 |

| 7.7  | Two stage InP OEIC receiver schematic diagram                            | 145 |

| 7.8  | Two stage OEIC receiver frequency response: '' ideal passives compo-     |     |

|      | nents, '' passives with added parasitics                                 | 146 |

| 7.9  | Two stage OEIC eye-diagram                                               | 146 |

## List of Tables

| 3.1 | Transformation matrices                                              | 61  |

|-----|----------------------------------------------------------------------|-----|

| 3.2 | P, $R$ and $C$ values and standard deviation for the foundry MESFETs | 63  |

| 4.1 | Receiver design parameters                                           | 70  |

| 5.1 | Raised cosine receiver element dimensions                            | 114 |

| 5.2 | New signal design receiver element dimensions                        | 118 |

| 6.1 | Optimised components values                                          | 133 |

| 7.1 | Measured results for the BTL-InP HFETs                               | 140 |

# List of Symbols

| $A_{v}$                                                                                                        | Voltage gain                                                     |

|----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| $A_z(0)$                                                                                                       | Midband closed loop transimpedance                               |

| $A_z(s)$                                                                                                       | Closed loop transimpedance                                       |

| $A_{zo}$                                                                                                       | Midband open loop transimpedance                                 |

| APD                                                                                                            | Avalanche photodiode                                             |

| $b_o$                                                                                                          | Optical power $b_o \in \{b_{min}, b_{max}\}$                     |

| $b_{max}$                                                                                                      | Optical power for a signal '1'                                   |

| $b_{min}$                                                                                                      | Optical power for a signal '0'                                   |

| B                                                                                                              | Bit rate                                                         |

| $B_o$                                                                                                          | Optical bandwidth                                                |

| BER                                                                                                            | Bit error rate                                                   |

| BW                                                                                                             | Bandwidth                                                        |

| $c_{11}, c_{12}, c_{21}, c_{22}$                                                                               | Two-port chain matrix elements                                   |

| C                                                                                                              | Gate and drain noise correlation coefficient                     |

| C                                                                                                              | Two-port chain matrix                                            |

| $C_d$                                                                                                          | Photodiode capacitance                                           |

| $C_{dg}$                                                                                                       | Drain-gate capacitance                                           |

| $C_{ds}$                                                                                                       | Drain-source capacitance                                         |

| $C_f$                                                                                                          | Feedback capacitance                                             |

| $C_{gs}$                                                                                                       | Gate-source capacitance                                          |

| CAD                                                                                                            | Computer aided design                                            |

| CB                                                                                                             | Common-base                                                      |

| $\mathbf{C}_{\mathcal{O}}$                                                                                     | Correlation matrix, chain representation                         |

| CD                                                                                                             | Common-drain                                                     |

| CG                                                                                                             | Common-gate                                                      |

| CS                                                                                                             | Common-source                                                    |

| $C_{m{T}}$                                                                                                     | Total input capacitance                                          |

| $\mathbf{C}_{Y}$                                                                                               | Correlation matrix, admittance representation                    |

| $\mathbf{C}_{oldsymbol{Z}}$                                                                                    | Correlation matrix, impedance representation                     |

| d                                                                                                              | Decision threshold                                               |

| $rac{d}{dt}\langle i_d i_d^*  angle$                                                                          | Drain noise current power spectral density                       |

| $rac{d}{dt}\langle i_d i_d^* angle \ rac{d}{dt}\langle i_g i_d^* angle \ rac{d}{dt}\langle i_g i_g^* angle$ | Gate and drain noise currents cross-correlation spectral density |

| $\frac{d}{dt}\langle i_g i_g^* \rangle$                                                                        | Gate noise current power spectral density                        |

| $d_{opt}$                                                                                                      | Optimum decision threshold                                       |

| - &                                                                                                            | -                                                                |

| DA                                               | Distributed amplifier                                                     |

|--------------------------------------------------|---------------------------------------------------------------------------|

| $e$ , $e_1$ and $e_2$                            | Noise voltage sources                                                     |

| E                                                | Cost function                                                             |

| $E_{isi}$                                        | Total ISI squared error                                                   |

| $E_{td}$                                         | Total TD squared error                                                    |

| $E_{zs}$                                         | Total ISI slope squared error                                             |

| EDFA                                             | Erbium doped fibre amplifier                                              |

| f f                                              | Frequency                                                                 |

| $f_{cd}$                                         | Drain line cut-off frequency                                              |

| -                                                | Drain line cut-off frequency                                              |

| $f_{cg}$                                         | Current gain cut-off frequency                                            |

| $f_T \ F_e$                                      | APD excess noise factor                                                   |

| -                                                | -                                                                         |

| $F_{min}$                                        | Minimum noise factor                                                      |

| FA                                               | Fibre amplifier                                                           |

| FET                                              | Field effect transistor                                                   |

| FWHM                                             | Full width at half maximum                                                |

| $g_{ds}$                                         | Drain-source conductance                                                  |

| g <sub>m</sub>                                   | Transconductance                                                          |

| $g_{mo} \ G$                                     | Absolute value of $g_m$                                                   |

| $G_k$                                            | Optical gain                                                              |

| $G_{a}$                                          | Gain coefficient; Stage gain                                              |

| -                                                | Real part of $Y_{out}$                                                    |

| $h_{0,n/2}$                                      | ZFE output at intervals $T/2$<br>Matched filter output at intervals $T/2$ |

| $egin{aligned} h_{m,n/2} \ h_o(t) \end{aligned}$ | Output pulse shape                                                        |

| $h_o'(t)$                                        | Time derivative of $h_o(t)$                                               |

| $h_p(t)$                                         | Input pulse shape                                                         |

| $h_T(t)$                                         | Linear receiver impulse response                                          |

| $H_o(f)$                                         | Fourier transform of output pulse                                         |

| $H_p(f)$                                         | Fourier transform of input pulse                                          |

| $H_{DA}(f)$                                      | Distribute amplifier transfer function                                    |

| HFET                                             | Heterojunction MESFET                                                     |

| $H_{FT}(f)$                                      | Transversal filter transfer function                                      |

| $H_{\mathbf{M}}(f)$                              | Whitened matched filter transfer function                                 |

| $H_T(f)$                                         | Linear receiver frequency response                                        |

| $H_{\lambda}(f)$                                 | Zero forcing filter transfer function                                     |

| $i, i_1 \text{ and } i_2$                        | Noise current sources                                                     |

| $i_{eq}(t)$                                      | Equivalent input noise current                                            |

| $i_d$                                            | Gate noise current                                                        |

| $i_g$                                            | Drain noise current                                                       |

| $I_1$ , $I_2$ and $I_3$                          | Noise integrals                                                           |

| $I_{dss}$                                        | Saturated drain current                                                   |

| $I_{g}$                                          | Gate leakage current                                                      |

| $\operatorname{Im}(\cdot)$                       | Imaginary part                                                            |

| $I_p$                                            | Photodiode current                                                        |

|                                                  |                                                                           |

| IFFT                     | Inverse fast Fourier transform                   |

|--------------------------|--------------------------------------------------|

| ISI                      | Intersymbol interference                         |

| $\boldsymbol{k}$         | Boltzmann's constant                             |

| $l_d$                    | Drain line inductance per unit length            |

| $l_g$                    | Gate line inductance per unit length             |

| $	ilde{L}_d$             | Drain inductance                                 |

| $L_g^-$                  | Gate inductance                                  |

| $L_{m{s}}^{m{s}}$        | Source inductance                                |

| $m_t$                    | Transverse mode number                           |

| M                        | APD gain                                         |

| M1, M2, M3               | Metal levels 1, 2 and 3                          |

| $M_n(s, h_T(t))$         | MGF of the additive Gaussian noise               |

| $M_n(S, nT(t))$ MCB      | Modified Chernoff bound                          |

| MESFET                   | Metallic Schottky barrier FET                    |

| MFPP                     | Marked and filtered Poisson process              |

| MGF                      | <u>-</u>                                         |

| MGF<br>MIM               | Moment generating function Metal-Insulator-Metal |

| MMIC                     |                                                  |

|                          | Microwave Monolithic Integrated Circuit          |

| $M_{Y_0}(s,h_T(t))$      | Symbol conditioned MGF for symbol '0'            |

| $M_{Y_1}(s,h_T(t))$      | Symbol conditioned MGF for symbol '1'            |

| $n_{sp}$                 | Population inversion parameter                   |

| N                        | Network order                                    |

| $NF_{min}$               | Minimum noise figure                             |

| NRZ                      | Non return to zero                               |

| NSD                      | New signal design                                |

| OA                       | Optical amplifier                                |

| OEIC                     | Optoelectronic integrated circuit                |

| OTDM                     | Optical-time division multiplexing               |

| $p(y \mid 0)$            | Conditional PDF for a symbol '0'                 |

| $p(y \mid 1)$            | Conditional PDF for a symbol '1'                 |

| $p_n$                    | $n^{	ext{th}}$ pole                              |

| $\overline{P}$           | Drain noise coefficient                          |

| $\overline{P}$           | Sensitivity                                      |

| P(	au)                   | Power penalty                                    |

| $P_0$                    | Probability of a symbol '0'                      |

| $P_1$                    | Probability of a symbol '1'                      |

| $P_{dB}(	au)$            | Power penalty in dB                              |

| $P_{err}$                | Error probability                                |

| PDF                      | probability density function                     |

| PIN                      | p-i-n photodiode                                 |

| PRBS                     | Pseudo random bic sequence                       |

|                          | Electronic charge                                |

| $\stackrel{q}{Q}(\cdot)$ | Gaussian Q-function                              |

| <b>v</b> (')             | Jitter range                                     |

|                          | n <sup>th</sup> residue                          |

| $r_n$                    | n resique                                        |

| R                                | Gate noise coefficient                             |

|----------------------------------|----------------------------------------------------|

| $R_{co}$                         | Electrode contact resistance                       |

| $R_d$                            | Drain resistance                                   |

| $R_{ds}$                         | Drain-source resistance                            |

|                                  |                                                    |

| $\operatorname{Re}(\cdot)$       | Real part Feedback resistance                      |

| $R_f$                            | Gate resistance                                    |

| $R_g$                            |                                                    |

| $R_i$                            | Gate charging resistance                           |

| $R_{in}$                         | Resistive portion of the input impedance           |

| $R'_{in}$                        | Parallel combination of $R_{in}$ and $R_f$         |

| $R_n$                            | Noise resistance                                   |

| $R_s$                            | Source resistance                                  |

| $\mathcal{R}_s$                  | Responsivity                                       |

| RC                               | Raised cosine                                      |

| $R_L$                            | Load resistance                                    |

| RZ                               | Return to zero                                     |

| 8                                | MCB adjustable parameter                           |

| s(t)                             | Pulse sequence at the input of the decision device |

| $s_{in}(t)$                      | Input signal                                       |

| $s_{out}(t)$                     | Output signal                                      |

| $S_{eq}(f)$                      | Spectral density of equivalent input noise current |

| $S_{in}(f)$                      | Input signal spectrum                              |

| $S_{out}(f)$                     | Output signal spectrum                             |

| $S_{ser}$                        | Series noise generator power spectral density      |

| $S_{shn}$                        | Shunt noise generator power spectral density       |

| SI                               | semi-insulating                                    |

| SLA                              | Semiconductor laser amplifier                      |

| SNR                              | Signal to noise ratio                              |

| $oldsymbol{t}$                   | Time                                               |

| $t_s$                            | Sampling instant                                   |

| T                                | Bit period                                         |

| ${f T}$                          | Transformation matrix                              |

| $T_{gk}$                         | k-th stage artificial gate line delay              |

| $T_{dk}$                         | k-th stage artificial drain line delay             |

| $T_s$                            | Pulse width (FWHM)                                 |

| TD                               | Telegraph distortion                               |

| $V_{DD}$                         | Drain bias voltage                                 |

| $V_{GG}$                         | Gate bias voltage                                  |

| $V_{SS}$                         | Source bias voltage                                |

| VSWR                             | Voltage standing wave ratio                        |

| $W_{isi}$                        | ISI weight                                         |

| $W_{td}$                         | TD weight                                          |

| $W_{zs}$                         | ISI slope weight                                   |

| $WC_{isi}$                       | Worst case ISI                                     |

| $y_{11}, y_{12}, y_{21}, y_{22}$ | Two-port admittance matrix elements                |

| Y                                                                                                                          | Two-port admittance matrix                                |

|----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|

| $Y_{opt}$                                                                                                                  | Optimum noise admittance                                  |

| $Y_{out}$                                                                                                                  | Output admittance                                         |

| $Y_N(f)$                                                                                                                   | Equivalent noise admittance                               |

| $z_{11}, z_{12}, z_{21}, z_{22}$                                                                                           | Two-port impedance matrix elements                        |

| $\mathbf{Z}$                                                                                                               | Two-port impedance matrix                                 |

| $Z_0$                                                                                                                      | Line characteristic impedance                             |

| $Z_{od}$                                                                                                                   | Drain line characteristic impedance                       |

| $Z_{og}$                                                                                                                   | Gate line characteristic impedance                        |

| ZFE                                                                                                                        | Zero forcing equaliser                                    |

| $\alpha$                                                                                                                   | Spectrum roll-off factor                                  |

| Γ                                                                                                                          | Excess channel-noise factor                               |

| $\delta(\cdot)$                                                                                                            | Dirac impulse                                             |

| $\Delta_k$                                                                                                                 | matched line delay                                        |

| $\Delta F_1$                                                                                                               | Equivalent noise bandwidth for $\sigma_{sp}^2$            |

| $\Delta F_2$                                                                                                               | Equivalent noise bandwidth for $\sigma_{sp-sp}^{\hat{z}}$ |

| η                                                                                                                          | Quantum efficiency                                        |

| heta                                                                                                                       | Absolute temperature                                      |

| $	heta_{	extsf{o}}$                                                                                                        | Standard reference temperature                            |

| $\sigma^{2} \\ \sigma_{0}^{2} \\ \sigma_{1}^{2} \\ \sigma_{c}^{2} \\ \sigma_{d}^{2} \\ \sigma_{i}^{2} \\ \sigma_{isi}^{2}$ | Proportionality factor for OAs signal dependent noise     |

| $\sigma_0^2$                                                                                                               | Total mean square noise associated with a binary '0'      |

| $\sigma_1^2$                                                                                                               | Total mean square noise associated with a binary '1'      |

| $\sigma_c^2$                                                                                                               | electronic receiver mean square noise                     |

| $\sigma_d^2$                                                                                                               | Mean square signal dependent noise                        |

| $\sigma_i^2$                                                                                                               | Mean square signal independent noise                      |

| $\sigma_{isi}$                                                                                                             | Intersymbol interference standard deviation               |

| $\sigma_o$ $\sigma_s^2$ $\sigma_{sp}^2$ $\sigma_{sp-sp}^2$ $\sigma_{s-sp}^2$                                               | Output noise standard deviation                           |

| $\sigma_s^2$                                                                                                               | OA signal shot noise                                      |

| $\sigma_{sp}^2$                                                                                                            | OA spontaneous emission shot noise                        |

| $\sigma_{sp-sp}^2$                                                                                                         | OA beat noise between spontaneous emission components     |

| $\sigma_{s-sp}^{z}$                                                                                                        | OA beat noise between signal and spontaneous emission     |

| $\Sigma_1$                                                                                                                 | Noise summation                                           |

| au                                                                                                                         | Normalised timing offset; Tap delay                       |

| $	au_{m{g}}$                                                                                                               | Gate line interstage delay                                |

| $	au_d$                                                                                                                    | Drain line interstage delay                               |

| $	au_{k}$                                                                                                                  | k-th stage equivalent tap delay                           |

| $	au_o$                                                                                                                    | Carriers travel delay                                     |

| $	au_{s}$                                                                                                                  | Soliton width parameter                                   |

| *                                                                                                                          | Convolution                                               |

| †                                                                                                                          | Complex conjugate                                         |

| 1                                                                                                                          | Hermitian conjugation                                     |

## Chapter 1

### Introduction

The very large bandwidth potential of optical fibre based systems and their low cost makes the optical fibre the preferred carrier for the long-haul telecommunication traffic. In fact, optical fibre communication systems cover 50% of the required capacity of all long-haul traffic world-wide and 70% in the UK [1]. Supporting new services such as tele-conferencing, high speed computer data networks, high definition cable TV and integrated services to the home necessitates research in the telecommunications industry directed towards the development of higher data rate systems in the interest of minimising the bit transport costs to the customer. Indeed, demonstrations of 10 Gbit/s optical systems are already common in laboratories worldwide [2, 3, 4, 5] and soliton, optical time division multiplexed and polarisation division multiplexed based system experiments demonstrating optical transmission out to 100 Gbit/s have been reported [6, 7, 8, 9]. As the bit rates increase lightwave systems employing optical amplifiers clearly out-perform the more traditional regenerative systems [10]. As the systems evolve towards the use of optical amplifiers and higher bit rates, transmission impairments such as intersymbol interference, signal and timing jitter and signal dependent noise assume greater importance and must be considered in the system design process. In particular these impairments must be taken into consideration and included in the design and optimisation of optical receivers. Accordingly, in this thesis the development of rigorous design strategies for high performance optical receivers and their proof via practical realisation is considered for the next generation of optical systems.

#### 1.1 Receivers and signal processing for direct detection optical communication systems

In direct detection optical communication systems the optical signal incident on the photodiode is converted into an electrical current, which is then amplified and further processed before the information carried by the optical signal can be extracted. The role of signal processing is to condition and reshape the electrical signal at the input of the decision device so that recovery of the information is facilitated and made with minimum ambiguity. Signal processing at the receiver must then take account of the transmitted signal format, shaping the wave form appropriately whilst at the same time minimising noise so as to enable clear decisions to be made [11]. The goal of signal shaping in digital optical receivers is thus the minimisation of the amount of optical power needed to achieve a given probability of error — the maximisation of the receiver sensitivity — in the presence of transmission impairments [12]. The move towards high speeds increases the importance of timing considerations. The signal must be filtered to achieve an eye pattern which is open vertically (low intersymbol interference) and horizontally (providing good jitter tolerance), whilst simultaneous maximisation of the receiver sensitivity requires its equivalent noise bandwidth be kept as small as possible within the above constraints. Since all high performance systems that are currently envisaged employ optical amplifiers, any signal design strategy proposed must account for the signal dependent nature of noise in optically amplified systems [10].

In parallel with the above developments in core network optical fibre transmission there is marked growth in mobile telecommunications [13] and in the use of subcarrier multiplexed optical fibre systems [14] to support mobility, as well as for other applications. This makes it appropriate to consider analogue optical receivers with rather different requirements, addressing specifically these applications. Analogue optical receivers should generate low noise across the band to maximise the signal to noise ratio of all the received channels and have good gain flatness across the band of each of the received channels to preserve the channel spectral content.

Various general receiver structures have been identified in the literature both for analogue and digital transmission with different performances and benefits. Among these the high impedance and the transimpedance [11] remain the more popular for wide band applications with the high impedance approach achieving the highest values of sensitivity and

the transimpedance approach obviating the need for bandwidth equalisation. For analogue applications, due to the usually narrow band requirements, the high impedance structure with some form of signal and noise tuning network is the favoured solution [15].

Receiver performance ultimately depends on the technology used and the best reported results for multi-Gbit/s optical receivers have been obtained using high electron mobility transistors and hybrid technology [16, 17]. However, there is a move towards integration to reduce production costs, improve repeatability and reliability, and ultimately achieve high performance. Accordingly, this study concentrates on integrated receivers intimately incorporating signal shaping/processing functions. The main focus is on GaAs MESFET technology exploring readily available foundry facilities, but preliminary consideration is given to the potential of InP-based technology for future requirements.

#### 1.2 Thesis organisation

Following this introductory chapter, signal processing techniques for digital optical receivers will be considered in chapter 2. In the case of PIN receivers different signal shaping solutions are reviewed and their performance compared with that of a raised cosine receiver which is shown to provide nearly ideal noise filtering and time domain performance. The raised cosine solution is then investigated for receivers where the signal dependence of the noise cannot be ignored, i.e. APD or optically preamplified receivers. It is shown that optimised sensitivity can be only achieved at the expense of poor tolerance to timing imp irments such as sampling and signalling jitter; conversely, timing robustness can be only achieved at the expense of sensitivity. To overcome this limitation a new family of waveforms for digital optical communication systems is derived that allows both optimised sensitivity and jitter tolerant operation to be obtained in optical receivers dominated by signal dependent noise. System implications for optical preamplified receivers are examined. Finally, an assessment of the realisability of the equalisation functions necessary to implement the new signal designs is effected.

Practical demonstration of the signal shaping strategies discussed in chapter 2 require the choice of an appropriate technology. GaAs microwave monolithic integrated circuit technology is now mature, achieving operating frequencies compatible with todays multi-Gbit/s optical communication system requirements. Also, custom fabrication facilities are readily available from the GaAs process manufacturers. Chapter 3 describes briefly

the GaAs technology and the models used in the practical implementation of the circuits discussed in subsequent chapters in this thesis. Noise modelling of the GaAs foundry active devices is considered in detail and a noise de-embedding technique is developed and applied to the determination of the noise coefficients that characterise the noise model chosen to represent the noise behaviour of the foundry MESFETs. The noise modelling and the de-embedding technique are then validated.

Chapter 4 discusses the practical implementation of the signal processing strategies proposed in chapter 2 for the realisation of jitter tolerant optical receivers. The discussed designs are implemented as GaAs MMICs. Two signal shaping designs are considered. The first is an optical receiver that incorporates the signal shaping necessary to secure optimum noise filtering and jitter tolerant operation according to the modified Chernoff bound criterion, while the second explores the possibility of using passive GaAs MMIC networks to effect signal shaping at very high bit rates and two practical post-detection filters are demonstrated for operation at 10 and 15 Gbit/s. In connection with the post-detection filter designs a novel direct time domain optimisation technique is developed that allows accurate design of GaAs MMIC passive filters. In this chapter, the realisation of optical receivers tolerant to the input circuit parasitics is also considered and a transimpedance configuration with a common-gate front-end stage is proposed as a means to achieve the desired robustness. The common-gate concept applied to optical receivers is demonstrated in this chapter through the implementation of a 5 Gbit/s optical receiver.

In chapter 5 the use of distributed amplifiers in optical communication systems is considered. The basic principles of operation of the distributed amplifier are reviewed and its use as an optical receiver discussed. A design example suggesting that standard GaAs MESFET technology can be used to implement distributed optical receivers operating at bit rates well over 10 Gbit/s is given. A novel technique is presented for using the distributed amplifier as an active pulse shaping/filtering network by effectively constructing the amplifier as a transversal filter. To illustrate the use and potential of the distributed amplifier as a pulse shaping network two 10 Gbit/s optical receiver designs with embedded signal shaping are presented. The first is designed to have a 100% raised cosine roll-off while the second implements a particular case of the new signal designs and its time domain performance is compared with its equivalent passive realisation.

Chapter 6 discusses electronic noise minimisation for optical receivers. Some well known noise reduction design solutions are discussed in an unified manner by considering the gen-

eral case of an optical receiver that uses a generic noise matching network between the photodiode and the front-end amplifying stage. From this general treatment the criteria for optimum noise matching in optical receivers are established. The design and optimisation of a noise tuned optical receiver for subcarrier multiplexed systems integrated as a GaAs MMIC is considered. A critical study of tuning networks suitable for integration is undertaken and the details of the design and optimisation strategy are given.

Chapter 7 is a first exploration of the potential of a still experimental InP-based process for the construction of 10 Gbit/s OEIC optical receivers. The InP-based process is briefly described and two optical receiver designs are proposed that satisfy the basic design requirements established in this chapter and demonstrate the potential of the technology for the realisation of 10 Gbit/s optical receivers.

Finally, chapter 8 concludes the thesis, summarising the main findings and identifying areas where further research may be appropriate.

#### 1.3 Summary of main contributions

The main contributions of this thesis may be summarised as follows:

- A new class of signal designs (NSD) is derived for optical communication systems that allow for the optimisation of the optical receiver sensitivity while maintaining jitter tolerant operation in systems dominated by signal dependent noise.

- An assessment of the realisability of the necessary equalisation functions to implement

the NSD is made and it is shown that optimised all-pole networks can provide close to

optimum performance. As a step in the simplification of the design and optimisation

process it is shown that a bandwidth optimised Thomson filter can be used as a near

optimum equaliser.

- A computationally simple noise de-embedding procedure is developed and applied to the noise modelling of the GaAs foundry MESFETs that are used in the active circuit implementations discussed in this thesis.

- Design and fabrication of a GaAs MMIC optical receiver with embedded signal shaping based on the modified Chernoff bound optimisation technique.

- Demonstration of the first common-gate transimpedance optical receiver. The receiver operates at 5 Gbit/s and is desensitised with respect to the input parasitic capacitances.

- Development and implementation of a novel direct time domain optimisation technique suitable for the design of very high speed GaAs MMIC signal shaping passive structures.

- Demonstration of GaAs MMIC post-detection signal shaping filters designed to satisfy the new signal design requirements and for operation at 10 and 15 Gbit/s. The optimisation of the impulse response of these filters is made using the optimisation technique mentioned above.

- The equivalence between the transversal filter and the distributed amplifier is demonstrated. It is thus proposed that a modified distributed amplifier due to its very high frequency capabilities can be used as a signal shaping/filtering network for multi-Gbit/s optical systems. In particular, two 10 Gbit/s design examples are given that demonstrate the possibility of implementing optical receivers with embedded pulse shaping using distributed amplifiers structures. Additionally alternative structures are proposed that can overcome some limitations of the originally proposed technique.

- The optimum noise matching criteria for optical receivers is established.

- Design, optimisation and fabrication of the first GaAs receiver with an integrated noise tuning network for subcarrier multiplexed applications.

- Demonstration of the capability of an experimental InP-based process for the realisation of 10 Gbit/s optical receivers.

The contributions made during the course of this research have led to the following publications:

I. Darwazeh, P. Lane, W. Marnane, P. Moreira, L. Watkins and M. Capstick. A high bit-rate GaAs MMIC optical receiver with optimum signal shaping. *Digest of 3rd.* Bangor Communications Symposium, pages 321-324, Bangor Wales, May 1991.

- 2. P. Moreira, P. Lane, I. Darwazeh and J. O'Reilly. Time domain optimisation of GaAs signal shaping filters for very high bit rate optical communications. Digest of IEE-11th Saraga Colloquium on Digital and Analogue Filters and Filtering Systems, pages 11/1-11/4, London UK, December 1991.

- J. J. O'Reilly and P. M. R. S. Moreira. Signal design for multi-Gbit/s optical receivers. Proc. Conference on Information Science and Systems, Vol. 1, pages 101-105, Princeton USA, March 1992.

- I. Darwazeh, P. Lane, W. Marnane, P. Moreira, L. Watkins, M. Capstick and J. O'Reilly. GaAs MMIC optical receiver with embedded signal processing. *IEE Proc.-G*, 139(2):241-243, April 1992.

- 5. P. Moreira, I. Darwazeh and J. O'Reilly. Design of an integrated tuned front-end GaAs receiver for SCM applications. Digest of 4th. Bangor Communications Symposium, pages 180-183, Bangor Wales, May 1992.

- 6. I. Darwazeh, P. Moreira, P. Lane and J. O'Reilly. A low input impedance multi Gbit GaAs optical receiver tolerant to photodiode parasitics. Digest of IEEE International Symposium on MMICs in Communications Systems, London UK, September 1992. Postdeadline paper.

- 7. P. Moreira, P. Lane, I. Darwazeh and J. O'Reilly. A GaAs signal shaping network with a controlled response from DC to 25 GHz. Digest of IEE-12th Saraga Colloquium on Digital and Analogue Filters and Filtering Systems, pages 12/1-12/4, London UK, November 1992.

- 8. I. Darwazeh, P. Moreira, P. Lane and J. O'Reilly. GaAs integrated common gate optical receiver. Workshop on Integrated Circuits for Optical Communications, Conference of Optical Fibre Communications-OFC'93, San Jose USA, February 1993.

- J. O'Reilly, P. Lane, P. Moreira and I. Darwazeh. A GaAs based approach to signal shaping for optical communications. Workshop on Integrated Circuits for Optical Communications, Conference of Optical Fibre Communications-OFC'93, San Jose USA, February 1993.

- P. Moreira, I. Darwazeh and J. O'Reilly. Distributed amplifier signal shaping strategy for multigigabit digital optical transmission. *Electron. Lett.*, 29(8):655-657, April 1993.

- P. Moreira, I. Darwazeh and J. O'Reilly. Noise optimisation of tuned integrated GaAs receiver. Proc. International Symposium on Fibre Optic Networks and Video Communications SPIE Vol. 1974: Transport Technologies for Broadband Optical Access Networks, pages 20-25, Berlin Germany, April 1993. in Press.

- 12. P. Lane, I. Darwazeh, P. Moreira and J. O'Reilly. GaAs MMIC technology applied to signal shaping for high bit-rate optical communications. Proc. International Symposium on Fibre Optic Networks and Video Communications SPIE Vol. 1974: Transport Technologies for Broadband Optical Access Networks, pages 57-67, Berlin Germany, April 1993, In Press.

- I. Darwazeh, P. Moreira, P. Lane and J. O'Reilly. 5 Gbit/s GaAs optical receiver MMIC. Digest of 5th. Bangor Communications Symposium, pages 163-166, Bangor Wales, June 1993.

- P. M. R. S. Moreira, P. M. Lane, I. Darwazeh and J. O'Reilly. Time domain optimisation of high bit rate optical receivers. Proc. Sixth Annual IEEE International ASIC Conference, pages 494-497, Rochester USA, September 1993.

- P. Moreira, I. Darwazeh and J. O'Reilly. Novel optical receiver design using distributed amplifier pulse shaping network. Digest of IEE-Colloquium on Optical Detectors and Receivers, pages 8/1-8/4, London UK, October 1993.

- 16. P. Moreira, I. Darwazeh and J. O'Reilly. Design and optimisation of a fully integrated GaAs tuned receiver preamplifier MMIC for optical SCM applications. *IEE Proc.-J Special Issue on Analogue Optical Fibre Communications*, 1993, In Press.

In the next chapter signal processing techniques for digital optical receivers will be considered.

## Chapter 2

# Signal shaping and noise filtering for optical communications

In this chapter, the relations between noise filtering, control of intersymbol interference and sensitivity relating to optical receivers will be further explored in the context of optimising the receiver performance by tailoring its impulse response. Signal designs for receivers dominated by Gaussian noise (PIN-receivers) will be reviewed. For systems where signal-dependent noise is dominant, depressed threshold signals will be examined and a new class of signals with optimum time domain characteristics will be derived. These signals offer advantages over more conventional ones, when system impairments such as signaling or timing jitter are important considerations [18]. Equalisers that use these targets will be compared with those obtained by a rigorous optimisation method based on the modified Chernoff bound. Finally, the possibility of using realisable networks to implement the required signal shaping will be investigated.

#### 2.1 Signal shaping for PIN-receivers