## **Bangor University**

## **DOCTOR OF PHILOSOPHY**

A roll-to-roll compatible vacuum-evaporation route to organic circuit production

Patchett, Eifion

Award date: 2014

Awarding institution: Bangor **University**

Link to publication

**General rights**Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal?

Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

Download date: 29. Jun. 2024

## **Bangor University**

# A Roll-to-roll Compatible Vacuumevaporation Route to Organic Circuit Production

## By

## Eifion Rhys Patchett

A thesis submitted for the degree of Doctor of Philosophy

College of Physical and Applied Sciences School of Electronics

| St | at | en | 1e | nt | 1: |  |

|----|----|----|----|----|----|--|

|----|----|----|----|----|----|--|

| This work has not previously been accepted in substance for any degree and is not being |

|-----------------------------------------------------------------------------------------|

| concurrently submitted in candidature for any degree unless as agreed by the University |

| for approved dual awards.                                                               |

| Signed (candidate)                                                                                                                                                                                                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Date                                                                                                                                                                                                                                                                       |

| Statement 2:                                                                                                                                                                                                                                                               |

| This thesis is the result of my own investigations, except where otherwise stated. Where correction services have been used, the extent and nature of the correction is clearly marked in a footnote(s).                                                                   |

| All other sources are acknowledged by footnotes and/or a bibliography.                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                            |

| Signed (candidate)                                                                                                                                                                                                                                                         |

| Date                                                                                                                                                                                                                                                                       |

| Statement 3:                                                                                                                                                                                                                                                               |

| I hereby give consent for my thesis, if accepted, to be available for photocopying, for inter-library loan and for electronic storage (subject to any constraints as defined in statement 4), and for the title and summary to be made available to outside organisations. |

| Signed (candidate)                                                                                                                                                                                                                                                         |

| Date                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                            |

## **Contents**

| Declaration of Authorship                                      | i        |

|----------------------------------------------------------------|----------|

| Contents                                                       | ii       |

| List of Figures                                                | v        |

| List of Tables                                                 | vii      |

| Papers and Poster Presentations                                | viii     |

| Abstract                                                       |          |

| Acknowledgements                                               |          |

| Chapter 1 Introduction                                         |          |

| 1.1 Introduction                                               |          |

| 1.2 Thesis Outline                                             |          |

|                                                                |          |

| 1.3 References                                                 |          |

| Chapter 2 Background Theory and Literature Review              | 5        |

| 2.1 Organic Semiconductors                                     | 5        |

| 2.1.1 Introduction                                             | 5        |

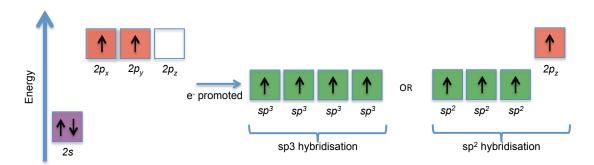

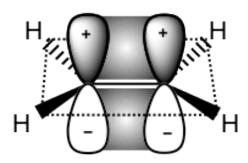

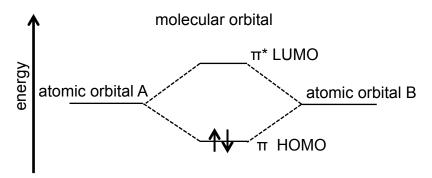

| 2.1.2 Bond Hybridisation                                       | 6        |

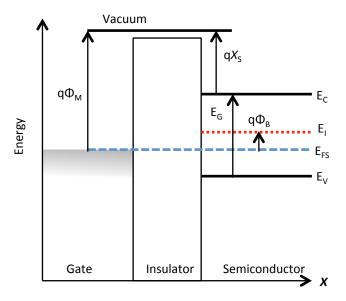

| 2.1.3 Energy Bands and Band Bending                            | 8        |

| 2.1.4 MIS Capacitors                                           |          |

| 2.1.5 Role of Dopants                                          |          |

| 2.1.6 Charge Trapping                                          |          |

| 2.1.7 Charge Transport in Organic Semiconductors               |          |

| 2.1.8 Organic Semiconductors                                   |          |

| 2.2 Organic Thin Film Transistors                              |          |

| 2.2.1 Introduction                                             |          |

| 2.2.2 The Gradual Channel Approximation and Mobility Equations |          |

| 2.2.3 Characterisation of OTFTs                                |          |

| 2.2.4 OTFTs in Literature                                      |          |

| 2.3 The Dielectric                                             |          |

| 2.3.1 Introduction                                             |          |

| 2.3.2 Common Dielectric Materials                              | 26       |

| 2.4 Organic Circuits                                           |          |

| 2.4.1 Introduction                                             | 27       |

| 2.4.2 Inverter                                                 | 28       |

| 2.4.3 Ring Oscillator                                          |          |

| 2.4.4 NOR and NAND Gates                                       |          |

| 2.4.5 SR Flip-flop                                             |          |

| 2.5 R2R Printing                                               |          |

| 2.5.1 Introduction                                             |          |

| 2.5.2 Printing Methods                                         |          |

| 2.5.3 The Development of Organic Circuit Printing              |          |

| 2.6 Summary and the Path Forward                               |          |

| 2.7 References                                                 | 46       |

| Chapter 3 Materials and Methods                                | 55       |

| 3.1 Introduction                                               |          |

| 3.2 Materials                                                  | 55<br>55 |

|                                                                |          |

|   | 3.2.2 Synthesis of DNTT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                          |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

|   | 2.2.3 Preparation of TPGDA Dielectric                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 56                                                       |

|   | 3.3 Substrate Cleaning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 57                                                       |

|   | 3.4 Fabrication Methods                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 57                                                       |

|   | 3.5 Device Fabrication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 58                                                       |

|   | 3.5.1 Si/SiO <sub>2</sub> /DNTT Transistor Fabrication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                          |

|   | 3.5.2 Bottom-Contact-Top-Gate PS/DNTT Device Fabrication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 58                                                       |

|   | 3.5.3 Top-Contact-Bottom-Gate PS/DNTT Device Fabrication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 59                                                       |

|   | 3.5.4 TPGDA/DNTT Device Fabrication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 60                                                       |

|   | 3.5.5 PS-TPGDA/DNTT Device Fabrication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                          |

|   | 3.5.6 Mask Designs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                          |

|   | 3.6 Surface Characterisation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                          |

|   | 3.7 Transistor Characterisation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 67                                                       |

|   | 3.8 Circuit Characterisation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 68                                                       |

|   | 3.8.1 Inverter Characterisation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 68                                                       |

|   | 3.8.2 Ring Oscillator Characterisation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                          |

|   | 3.8.3 Characterisation of NOR/NAND and SR Flip-flop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 69                                                       |

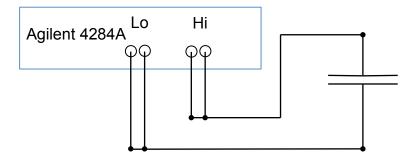

|   | 3.9 Capacitance Measurements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 70                                                       |

|   | 3.10 Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 70                                                       |

|   | 3.11 References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 70                                                       |

| _ | Chapter 4 Si/SiO <sub>2</sub> /DNTT Transistors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 72                                                       |

| · | 4.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                          |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                          |

|   | 4.2 Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                          |

|   | 4.3 Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                          |

|   | 4.4 Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 82                                                       |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0.0                                                      |

|   | 4.5 References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 82                                                       |

| C | 4.5 References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                          |

| C | 4.5 References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 84                                                       |

| C | 4.5 References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>84</b>                                                |

| C | 4.5 References  Chapter 5 Polystyrene/DNTT Devices  5.1 Introduction  5.2 The Semiconductor/Dielectric Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <b>84</b><br>84                                          |

| C | 4.5 References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>84</b><br>84<br>85                                    |

| • | 4.5 References  Chapter 5 Polystyrene/DNTT Devices  5.1 Introduction  5.2 The Semiconductor/Dielectric Interface  5.3 Top-Gate-Bottom-Contact Polystyrene/DNTT Transistors  5.3.1 Results                                                                                                                                                                                                                                                                                                                                                                                                                                            | <b>84</b><br>84<br>85<br>85                              |

| C | 4.5 References  Chapter 5 Polystyrene/DNTT Devices  5.1 Introduction  5.2 The Semiconductor/Dielectric Interface  5.3 Top-Gate-Bottom-Contact Polystyrene/DNTT Transistors  5.3.1 Results  5.4 Top Gate Polystyrene DNTT Inverter                                                                                                                                                                                                                                                                                                                                                                                                    | <b>84</b><br>84<br>85<br>85                              |

| • | 4.5 References  Chapter 5 Polystyrene/DNTT Devices  5.1 Introduction  5.2 The Semiconductor/Dielectric Interface  5.3 Top-Gate-Bottom-Contact Polystyrene/DNTT Transistors  5.3.1 Results  5.4 Top Gate Polystyrene DNTT Inverter  5.4.1 Results                                                                                                                                                                                                                                                                                                                                                                                     | <b>84</b><br>84<br>85<br>85<br>87                        |

| C | 4.5 References  Chapter 5 Polystyrene/DNTT Devices  5.1 Introduction  5.2 The Semiconductor/Dielectric Interface  5.3 Top-Gate-Bottom-Contact Polystyrene/DNTT Transistors  5.3.1 Results  5.4 Top Gate Polystyrene DNTT Inverter                                                                                                                                                                                                                                                                                                                                                                                                    | <b>84</b> 848585858788                                   |

| • | 4.5 References  Chapter 5 Polystyrene/DNTT Devices  5.1 Introduction  5.2 The Semiconductor/Dielectric Interface  5.3 Top-Gate-Bottom-Contact Polystyrene/DNTT Transistors  5.3.1 Results  5.4 Top Gate Polystyrene DNTT Inverter  5.4.1 Results  5.5 Bottom-Gate-Top-Contact Polystyrene/DNTT Transistors                                                                                                                                                                                                                                                                                                                           | <b>84</b> 848585878990                                   |

|   | 4.5 References  Chapter 5 Polystyrene/DNTT Devices  5.1 Introduction  5.2 The Semiconductor/Dielectric Interface  5.3 Top-Gate-Bottom-Contact Polystyrene/DNTT Transistors  5.3.1 Results  5.4 Top Gate Polystyrene DNTT Inverter  5.4.1 Results  5.5 Bottom-Gate-Top-Contact Polystyrene/DNTT Transistors  5.5.1 Transistor Characteristics  5.6 Discussion                                                                                                                                                                                                                                                                         | <b>84</b> 84858587899090                                 |

|   | 4.5 References  Chapter 5 Polystyrene/DNTT Devices  5.1 Introduction  5.2 The Semiconductor/Dielectric Interface  5.3 Top-Gate-Bottom-Contact Polystyrene/DNTT Transistors  5.3.1 Results  5.4 Top Gate Polystyrene DNTT Inverter  5.4.1 Results  5.5 Bottom-Gate-Top-Contact Polystyrene/DNTT Transistors  5.5.1 Transistor Characteristics                                                                                                                                                                                                                                                                                         | <b>84</b> 848587889090                                   |

|   | 4.5 References  Chapter 5 Polystyrene/DNTT Devices  5.1 Introduction  5.2 The Semiconductor/Dielectric Interface  5.3 Top-Gate-Bottom-Contact Polystyrene/DNTT Transistors  5.3.1 Results  5.4 Top Gate Polystyrene DNTT Inverter  5.4.1 Results  5.5 Bottom-Gate-Top-Contact Polystyrene/DNTT Transistors  5.5.1 Transistor Characteristics  5.6 Discussion  5.7 Summary  5.8 References                                                                                                                                                                                                                                            | 84<br>84<br>85<br>87<br>88<br>90<br>90                   |

|   | 4.5 References  Chapter 5 Polystyrene/DNTT Devices  5.1 Introduction  5.2 The Semiconductor/Dielectric Interface  5.3 Top-Gate-Bottom-Contact Polystyrene/DNTT Transistors  5.3.1 Results  5.4 Top Gate Polystyrene DNTT Inverter  5.4.1 Results  5.5 Bottom-Gate-Top-Contact Polystyrene/DNTT Transistors  5.5.1 Transistor Characteristics  5.6 Discussion  5.7 Summary  5.8 References  Chapter 6 TPGDA/DNTT Devices                                                                                                                                                                                                              | 84<br>84<br>85<br>85<br>87<br>90<br>90<br>90             |

|   | 4.5 References  Chapter 5 Polystyrene/DNTT Devices  5.1 Introduction  5.2 The Semiconductor/Dielectric Interface  5.3 Top-Gate-Bottom-Contact Polystyrene/DNTT Transistors  5.3.1 Results  5.4 Top Gate Polystyrene DNTT Inverter  5.4.1 Results  5.5 Bottom-Gate-Top-Contact Polystyrene/DNTT Transistors  5.5.1 Transistor Characteristics  5.6 Discussion  5.7 Summary  5.8 References  Chapter 6 TPGDA/DNTT Devices  6.1 Introduction                                                                                                                                                                                            | 84<br>84<br>85<br>85<br>90<br>90<br>99<br>99             |

|   | 4.5 References  Chapter 5 Polystyrene/DNTT Devices  5.1 Introduction  5.2 The Semiconductor/Dielectric Interface  5.3 Top-Gate-Bottom-Contact Polystyrene/DNTT Transistors  5.3.1 Results  5.4 Top Gate Polystyrene DNTT Inverter  5.4.1 Results  5.5 Bottom-Gate-Top-Contact Polystyrene/DNTT Transistors  5.5.1 Transistor Characteristics  5.6 Discussion  5.7 Summary  5.8 References  Chapter 6 TPGDA/DNTT Devices  6.1 Introduction  6.2 TPGDA/DNTT Transistors                                                                                                                                                                | 84<br>84<br>85<br>85<br>87<br>90<br>90<br>99<br>96<br>99 |

|   | 4.5 References  Chapter 5 Polystyrene/DNTT Devices  5.1 Introduction  5.2 The Semiconductor/Dielectric Interface  5.3 Top-Gate-Bottom-Contact Polystyrene/DNTT Transistors  5.3.1 Results  5.4 Top Gate Polystyrene DNTT Inverter  5.4.1 Results  5.5 Bottom-Gate-Top-Contact Polystyrene/DNTT Transistors  5.5.1 Transistor Characteristics  5.6 Discussion  5.7 Summary  5.8 References  Chapter 6 TPGDA/DNTT Devices  6.1 Introduction  6.2 TPGDA/DNTT Transistors  6.2.1 Experimental Results                                                                                                                                    | 84<br>84<br>85<br>85<br>87<br>90<br>90<br>99<br>96<br>97 |

|   | 4.5 References  Chapter 5 Polystyrene/DNTT Devices  5.1 Introduction  5.2 The Semiconductor/Dielectric Interface  5.3 Top-Gate-Bottom-Contact Polystyrene/DNTT Transistors  5.3.1 Results  5.4 Top Gate Polystyrene DNTT Inverter  5.4.1 Results  5.5 Bottom-Gate-Top-Contact Polystyrene/DNTT Transistors  5.5.1 Transistor Characteristics  5.6 Discussion  5.7 Summary  5.8 References  Chapter 6 TPGDA/DNTT Devices  6.1 Introduction  6.2 TPGDA/DNTT Transistors  6.2.1 Experimental Results  6.2.2 Discussion                                                                                                                  | 84<br>84<br>85<br>90<br>90<br>96<br>97<br>97<br>99<br>90 |

|   | 4.5 References  Chapter 5 Polystyrene/DNTT Devices  5.1 Introduction  5.2 The Semiconductor/Dielectric Interface  5.3 Top-Gate-Bottom-Contact Polystyrene/DNTT Transistors  5.3.1 Results  5.4 Top Gate Polystyrene DNTT Inverter  5.4.1 Results  5.5 Bottom-Gate-Top-Contact Polystyrene/DNTT Transistors  5.5.1 Transistor Characteristics  5.6 Discussion  5.7 Summary  5.8 References  Chapter 6 TPGDA/DNTT Devices  6.1 Introduction  6.2 TPGDA/DNTT Transistors  6.2.1 Experimental Results  6.2.2 Discussion  6.3 Environmental Stability of DNTT                                                                             | 8484858790999697999190100105                             |

|   | 2. Chapter 5 Polystyrene/DNTT Devices 5.1 Introduction 5.2 The Semiconductor/Dielectric Interface 5.3 Top-Gate-Bottom-Contact Polystyrene/DNTT Transistors 5.3.1 Results 5.4 Top Gate Polystyrene DNTT Inverter 5.4.1 Results 5.5 Bottom-Gate-Top-Contact Polystyrene/DNTT Transistors 5.5.1 Transistor Characteristics 5.6 Discussion 5.7 Summary 5.8 References  Chapter 6 TPGDA/DNTT Devices 6.1 Introduction 6.2 TPGDA/DNTT Transistors 6.2.1 Experimental Results 6.2.2 Discussion 6.3 Environmental Stability of DNTT 6.3.1 Experimental Results                                                                               | 848485879094969799100105112                              |

|   | 4.5 References  Chapter 5 Polystyrene/DNTT Devices  5.1 Introduction 5.2 The Semiconductor/Dielectric Interface 5.3 Top-Gate-Bottom-Contact Polystyrene/DNTT Transistors 5.3.1 Results 5.4 Top Gate Polystyrene DNTT Inverter 5.4.1 Results 5.5 Bottom-Gate-Top-Contact Polystyrene/DNTT Transistors 5.5.1 Transistor Characteristics 5.6 Discussion 5.7 Summary 5.8 References  Chapter 6 TPGDA/DNTT Devices 6.1 Introduction 6.2 TPGDA/DNTT Transistors 6.2.1 Experimental Results 6.2.2 Discussion 6.3 Environmental Stability of DNTT 6.3.1 Experimental Results 6.3.2 Discussion                                                | 8484859090969799100100112113                             |

|   | 2. Seferences  Chapter 5 Polystyrene/DNTT Devices  5.1 Introduction 5.2 The Semiconductor/Dielectric Interface 5.3 Top-Gate-Bottom-Contact Polystyrene/DNTT Transistors 5.3.1 Results 5.4 Top Gate Polystyrene DNTT Inverter 5.4.1 Results 5.5 Bottom-Gate-Top-Contact Polystyrene/DNTT Transistors 5.5.1 Transistor Characteristics 5.6 Discussion 5.7 Summary 5.8 References  Chapter 6 TPGDA/DNTT Devices 6.1 Introduction 6.2 TPGDA/DNTT Transistors 6.2.1 Experimental Results 6.2.2 Discussion 6.3 Environmental Stability of DNTT 6.3.1 Experimental Results 6.3.2 Discussion 6.4 Transistors In Vacuum                       | 848485879099969799100105112113                           |

|   | 4.5 References  Chapter 5 Polystyrene/DNTT Devices  5.1 Introduction 5.2 The Semiconductor/Dielectric Interface 5.3 Top-Gate-Bottom-Contact Polystyrene/DNTT Transistors 5.3.1 Results. 5.4 Top Gate Polystyrene DNTT Inverter. 5.4.1 Results. 5.5 Bottom-Gate-Top-Contact Polystyrene/DNTT Transistors 5.5.1 Transistor Characteristics. 5.6 Discussion 5.7 Summary 5.8 References  Chapter 6 TPGDA/DNTT Devices 6.1 Introduction 6.2 TPGDA/DNTT Transistors 6.2.1 Experimental Results 6.2.2 Discussion 6.3 Environmental Stability of DNTT 6.3.1 Experimental Results 6.3.2 Discussion 6.4 Transistors In Vacuum 6.4.1 Results    | 84848587909099969799100105112113113                      |

|   | 2. References  2. Introduction 5. 2 The Semiconductor/Dielectric Interface 5. 3 Top-Gate-Bottom-Contact Polystyrene/DNTT Transistors 5. 3.1 Results 5.4 Top Gate Polystyrene DNTT Inverter 5.4.1 Results 5.5 Bottom-Gate-Top-Contact Polystyrene/DNTT Transistors 5.5.1 Transistor Characteristics 5.6 Discussion 5.7 Summary 5.8 References  2. References  2. Introduction 6.2 TPGDA/DNTT Devices 6.1 Introduction 6.2 TPGDA/DNTT Transistors 6.2.1 Experimental Results 6.2.2 Discussion 6.3 Environmental Stability of DNTT 6.3.1 Experimental Results 6.3.2 Discussion 6.4 Transistors In Vacuum 6.4.1 Results 6.4.2 Discussion | 848485879099999699100112113113113                        |

|   | 4.5 References  Chapter 5 Polystyrene/DNTT Devices  5.1 Introduction 5.2 The Semiconductor/Dielectric Interface 5.3 Top-Gate-Bottom-Contact Polystyrene/DNTT Transistors 5.3.1 Results. 5.4 Top Gate Polystyrene DNTT Inverter. 5.4.1 Results. 5.5 Bottom-Gate-Top-Contact Polystyrene/DNTT Transistors 5.5.1 Transistor Characteristics. 5.6 Discussion 5.7 Summary 5.8 References  Chapter 6 TPGDA/DNTT Devices 6.1 Introduction 6.2 TPGDA/DNTT Transistors 6.2.1 Experimental Results 6.2.2 Discussion 6.3 Environmental Stability of DNTT 6.3.1 Experimental Results 6.3.2 Discussion 6.4 Transistors In Vacuum 6.4.1 Results    | 848485879094969799100112113113113113                     |

| 6.6 TPGDA/DNTT Inverter                                  | 122 |

|----------------------------------------------------------|-----|

| 6.6.1 Experimental Results                               | 122 |

| 6.6.2 Discussion                                         | 123 |

| 6.7 Summary                                              | 124 |

| 6.8 References                                           | 125 |

| Chapter 7 Polystyrene/TPGDA DNTT Devices                 | 129 |

| 7.1 Introduction                                         |     |

| 7.2 PS-TPGDA/DNTT Transistors                            | 129 |

| 7.2.1 Results                                            |     |

| 7.2.2 Transistor Characteristics After Six Months in Air |     |

| 7.2.3 A Closer Look At Parasitic Currents                |     |

| 7.2.4 Discussion                                         |     |

| 7.3 PS-TPGDA/DNTT Inverters                              |     |

| 7.3.1 Experimental Results                               |     |

| 7.3.2 Discussion                                         |     |

| 7.4 PS-TPGDA/DNTT Ring Oscillator                        |     |

| 7.4.1 Results and Discussion                             |     |

| 7.5 Summary                                              |     |

| 7.6 References                                           | 154 |

| Chapter 8 Logic Devices                                  | 158 |

| 8.1 Introduction                                         | 158 |

| 8.2 NOR and NAND Logic Gates                             | 158 |

| 8.2.1 NOR Gate Results                                   |     |

| 8.2.2 NAND Gate Results                                  |     |

| 8.2.3 Discussion                                         |     |

| 8.3 NAND SR Flip-Flop                                    |     |

| 8.3.1 NAND SR Flip-flop Experimental Results             |     |

| 8.4 Summary                                              |     |

| 8.5 References                                           | 173 |

| Chapter 9 Conclusions and Further Work                   | 175 |

| 9.1 Conclusions                                          | 175 |

| 9.2 Further Work                                         | 178 |

| 0.3 References                                           | 180 |

# List Of Figures

| 2.1 Bond Hybridisation                                                                                                                                                            | 6  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 Ethene showing p <sub>z</sub> orbitals                                                                                                                                        | 7  |

| 2.3 HOMO and LUMO energy levels                                                                                                                                                   | 7  |

| 2.4 Schematic cross-section of an MIS capacitor                                                                                                                                   |    |

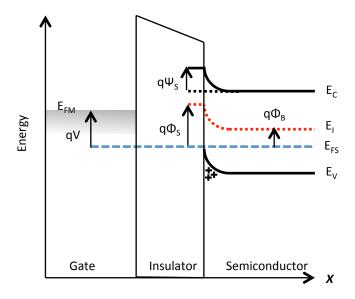

| 2.5 Flatband conditions                                                                                                                                                           |    |

| 2.6 Band bending showing accumulation                                                                                                                                             |    |

| 2.7 Band bending showing depletion                                                                                                                                                |    |

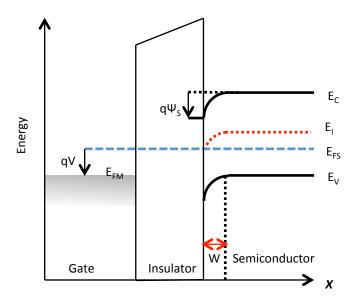

| 2.8 Oxygen doping                                                                                                                                                                 |    |

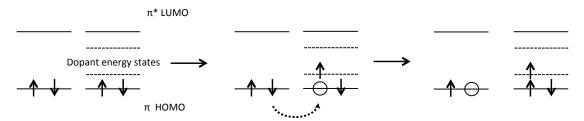

| 2.9 Circuit schematic of a transistor.                                                                                                                                            |    |

| 2.10 Schematic cross-section of a transistor in accumulation.                                                                                                                     |    |

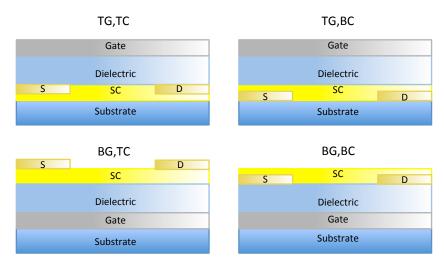

| 2.11 The four configurations of the transistor                                                                                                                                    |    |

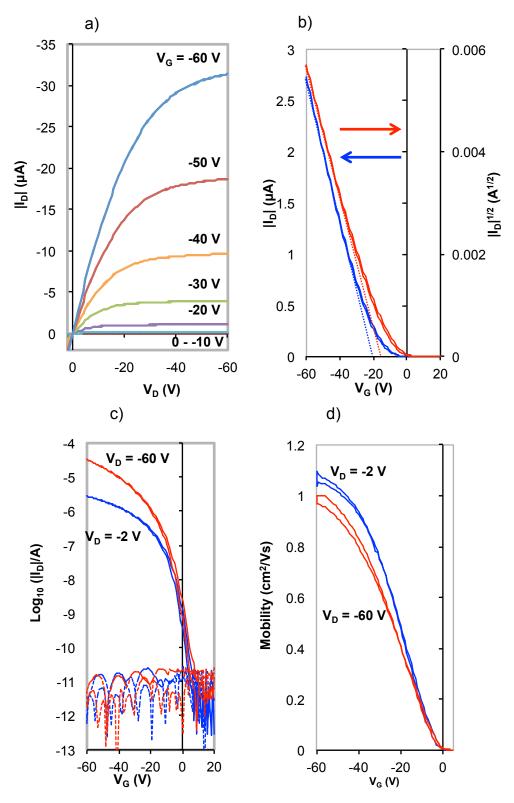

| 2.12 Typical set of transistor characteristics                                                                                                                                    |    |

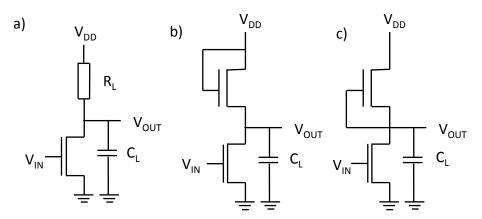

| 2.13 Circuit schematics for inverters.                                                                                                                                            |    |

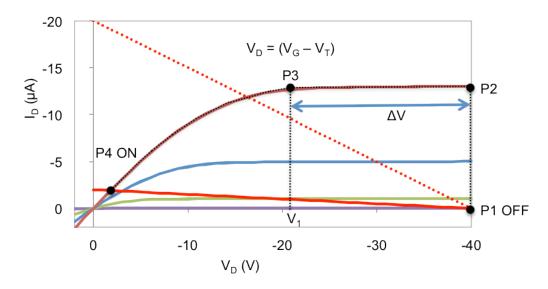

| 2.14 Resistor load inverter load line                                                                                                                                             |    |

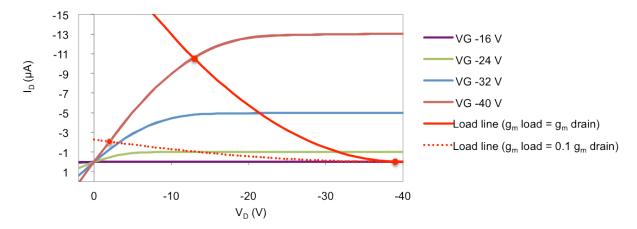

| 2.15 Enhancement mode load inverter load line                                                                                                                                     |    |

| 2.16 Voltage transfer plot.                                                                                                                                                       |    |

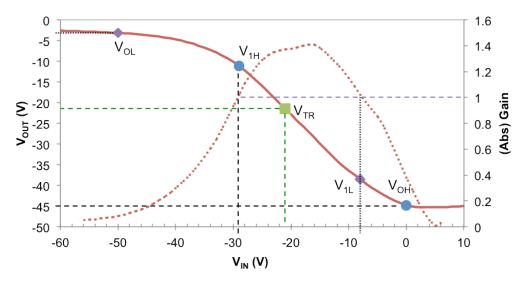

| 2.17 Ring oscillator circuit schematic                                                                                                                                            |    |

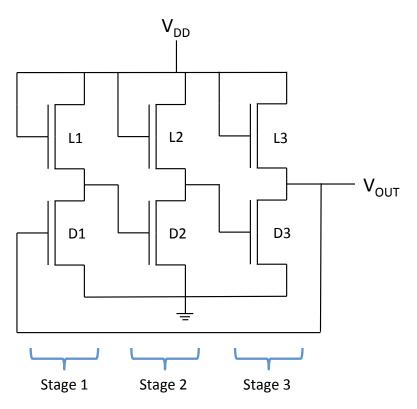

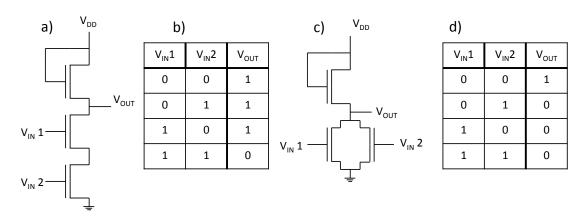

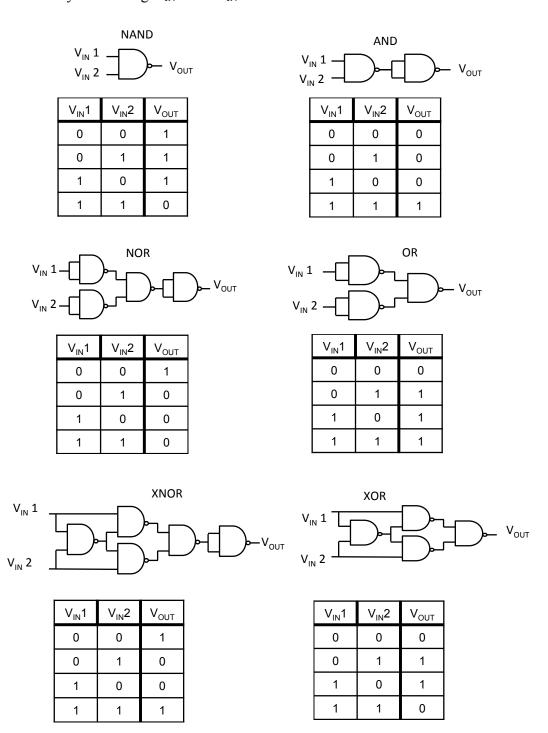

| 2.18 NOR/NAND gates circuit schematics and truth tables                                                                                                                           |    |

| 2.19 All logic functions completed solely by NAND gates                                                                                                                           |    |

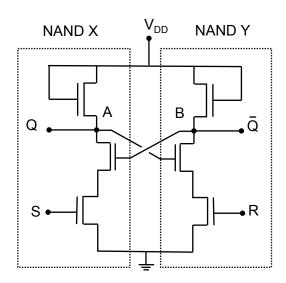

| 2.20 NAND SR Flip-flop circuit schematic and truth table                                                                                                                          |    |

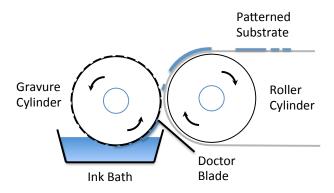

| 2.21 Gravure printing process                                                                                                                                                     |    |

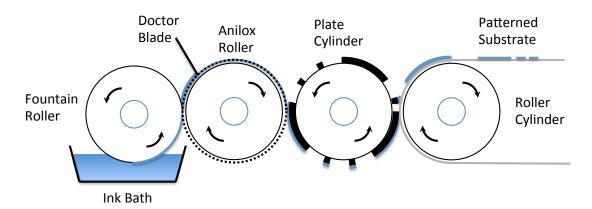

| 2.22 Flexographic printing process                                                                                                                                                |    |

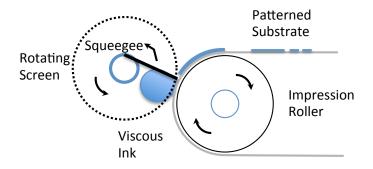

| 2.23 Screen printing process                                                                                                                                                      |    |

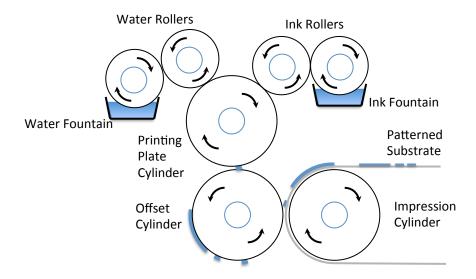

| 2.24 Offset printing process                                                                                                                                                      |    |

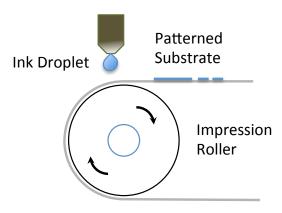

| 2.25 Inkjet printing process                                                                                                                                                      |    |

|                                                                                                                                                                                   |    |

| 3.1 Synthesis of DNTT                                                                                                                                                             |    |

|                                                                                                                                                                                   |    |

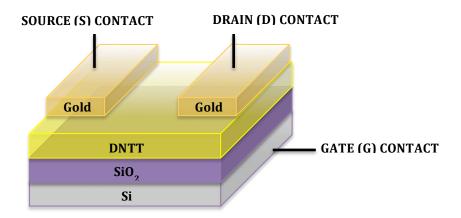

| 3.3 Schematic cross-section of a Si/SiO <sub>2</sub> /DNTT transistor                                                                                                             |    |

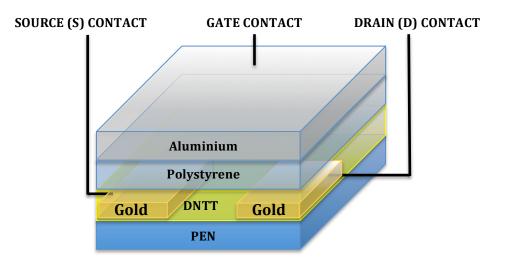

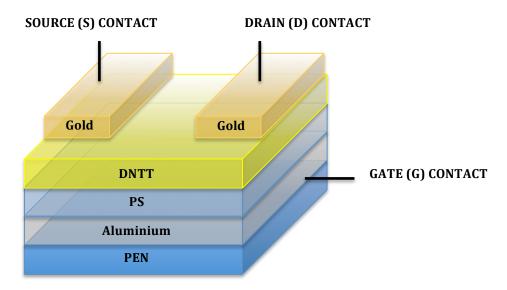

| <ul><li>3.4 Schematic cross-section of a top-gate bottom-contact PS/DNTT transistor</li><li>3.5 Schematic cross-section of a bottom-gate top-contact PS/DNTT transistor</li></ul> |    |

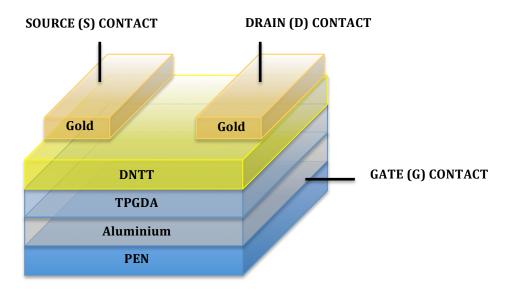

| 3.6 Schematic cross-section of a Dottom-gate top-contact PS/DIV11 transistor                                                                                                      |    |

|                                                                                                                                                                                   |    |

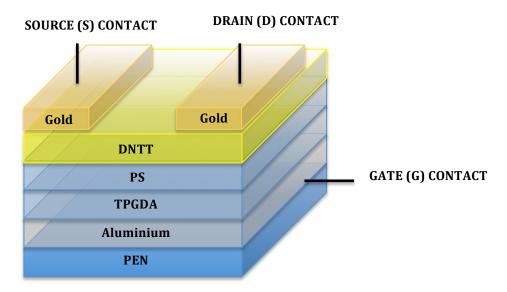

| 3.7 Schematic cross-section of a PS-TPGDA/DNTT transistor                                                                                                                         |    |

|                                                                                                                                                                                   |    |

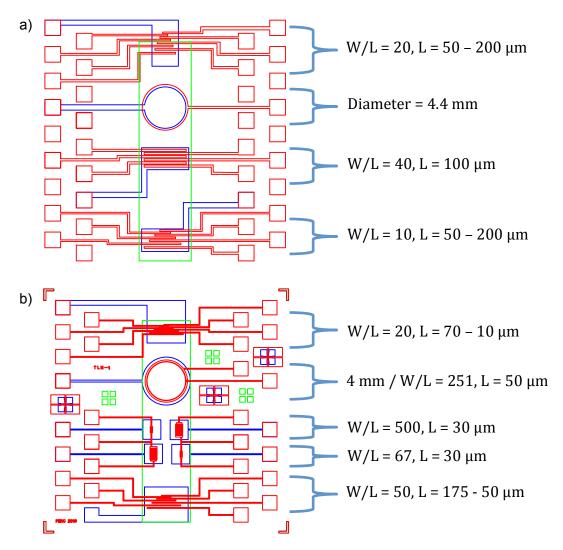

| 3.9 Mask Set 3                                                                                                                                                                    |    |

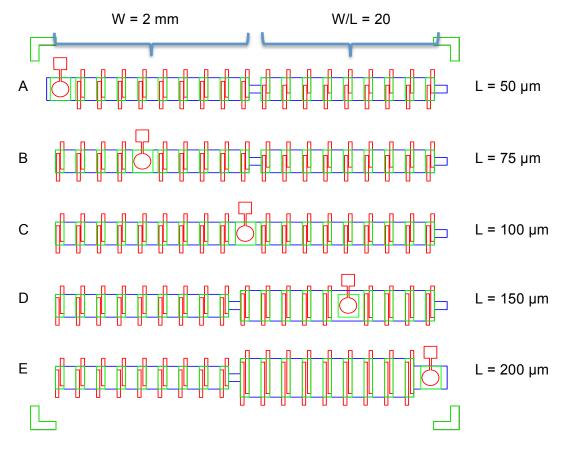

|                                                                                                                                                                                   |    |

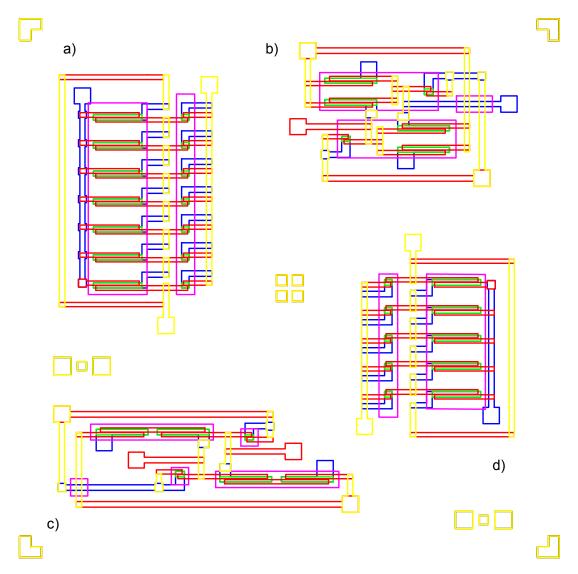

| 3.11 Mask Set 5                                                                                                                                                                   |    |

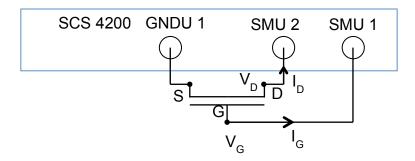

| 3.12 Transistor characterisation setup                                                                                                                                            |    |

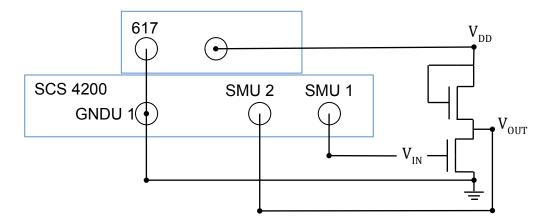

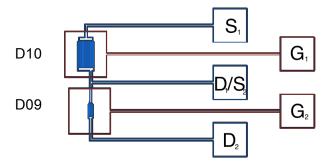

| 3.13 Inverter characterisation setup                                                                                                                                              |    |

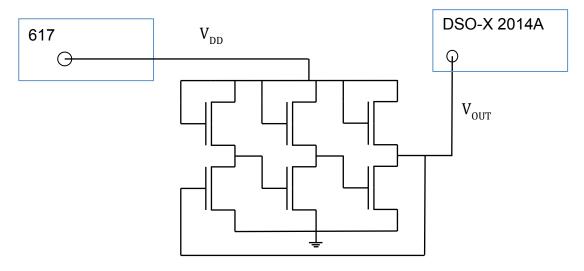

| 3.14 Ring oscillator characterisation setup                                                                                                                                       |    |

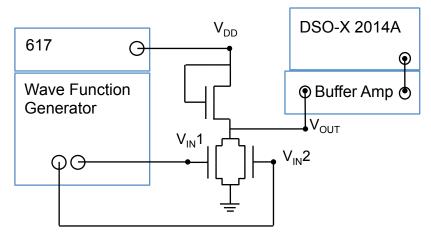

| 3.15 NOR/NAND gate characterisation setup                                                                                                                                         |    |

| 3.16 Capacitance measurements setup                                                                                                                                               |    |

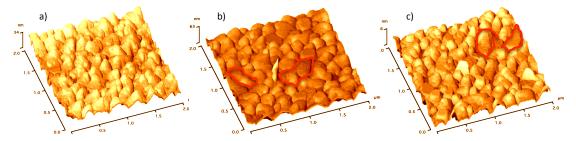

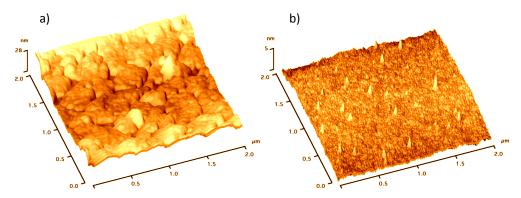

| 4.1 AFM of the surfaces of the three DNTT samples                                                                                                                                 |    |

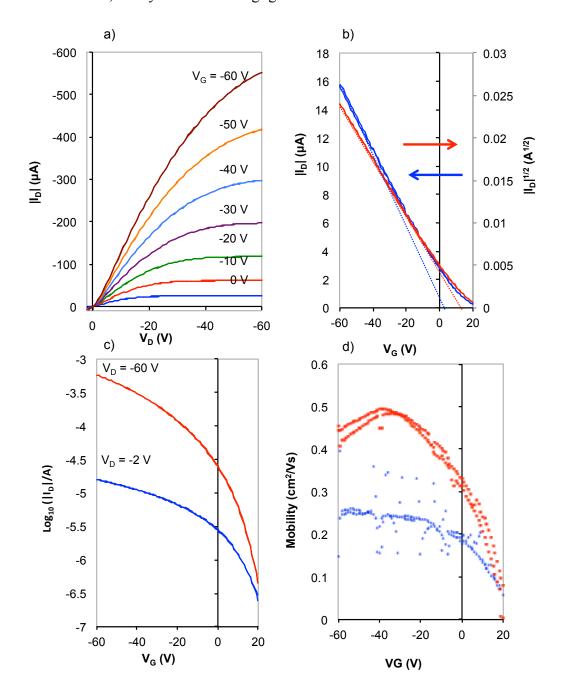

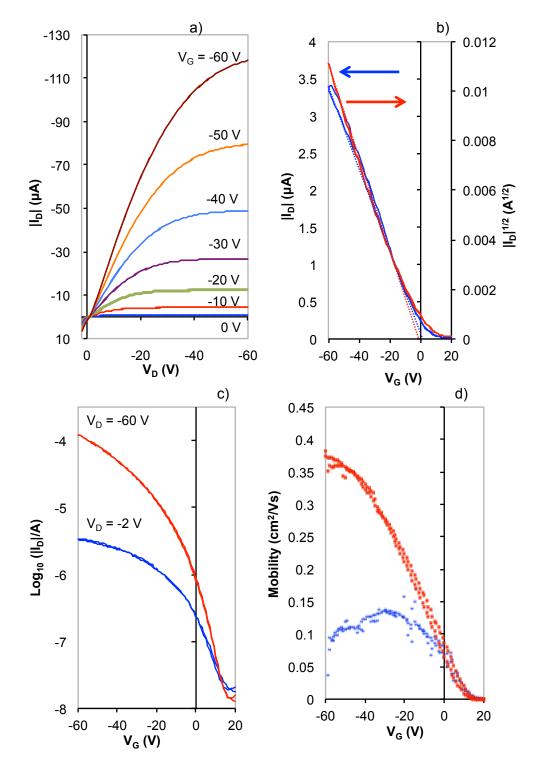

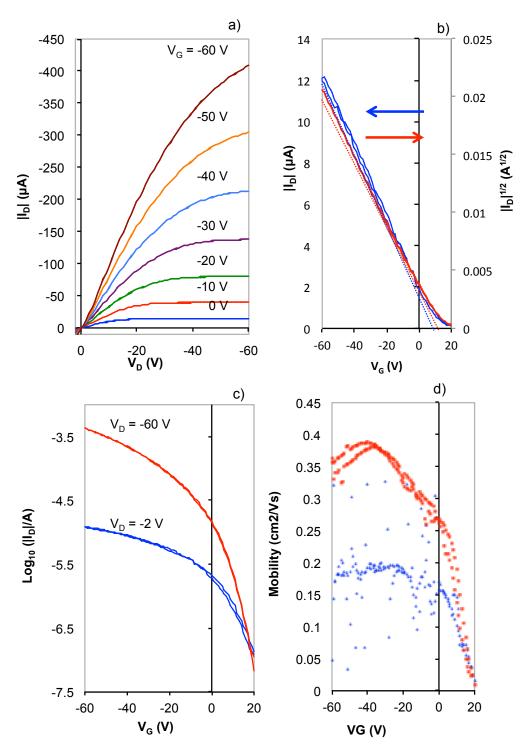

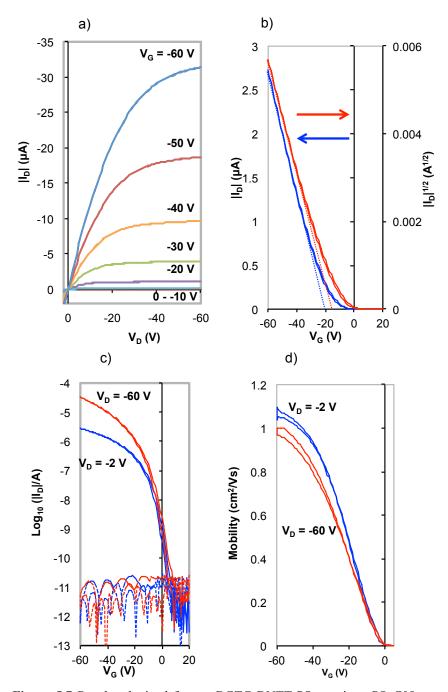

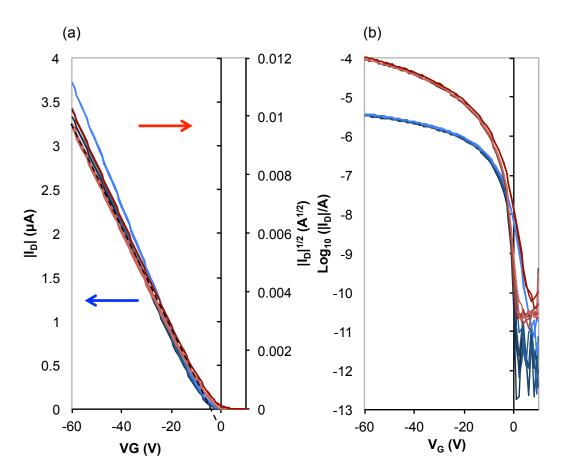

| 4.2 R-DNTT transistor characteristics                                                                                                                                             |    |

| 4.3 S-DNTT transistor characteristics                                                                                                                                             |    |

| 4.4 SR-DNTT transistor characteristics                                                                                                                                            |    |

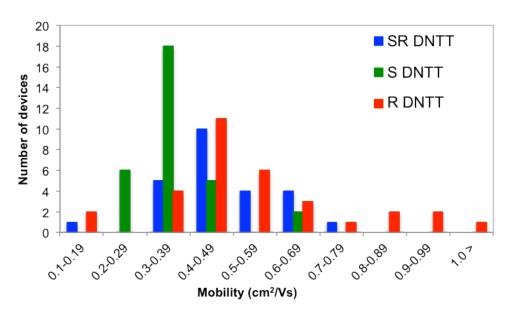

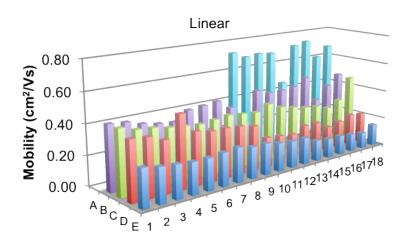

| 4.5 Histogram of transistor mobilities                                                                                                                                            | 79 |

| 5.1 AFM images of the surfaces of TPGDA and DNTT on PEN substrate                                                                                                                 | 85 |

| 5.2 Top-gate-bottom-contact PS/DNTT transistor characteristics                           | 86  |

|------------------------------------------------------------------------------------------|-----|

| 5.3 Inverter mask design from Mask Set 2                                                 | 88  |

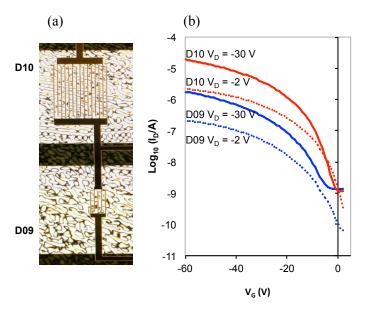

| 5.4 Inverter microscope image and semi-log plots of transistor transfers                 | 88  |

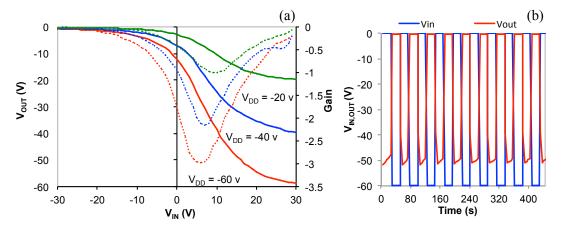

| 5.5 Voltage transfer and dynamic square wave response of PS/DNTT inverter                |     |

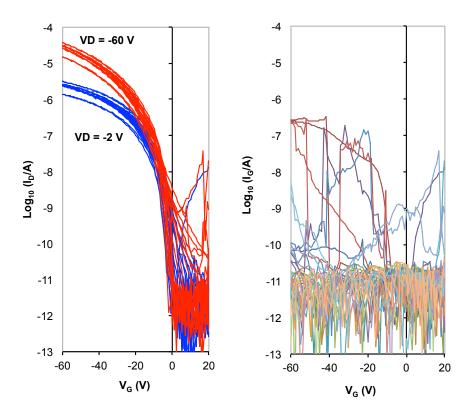

| 5.6 Semi-log transfer plots of 9 PS transistors of identical geometry                    | 91  |

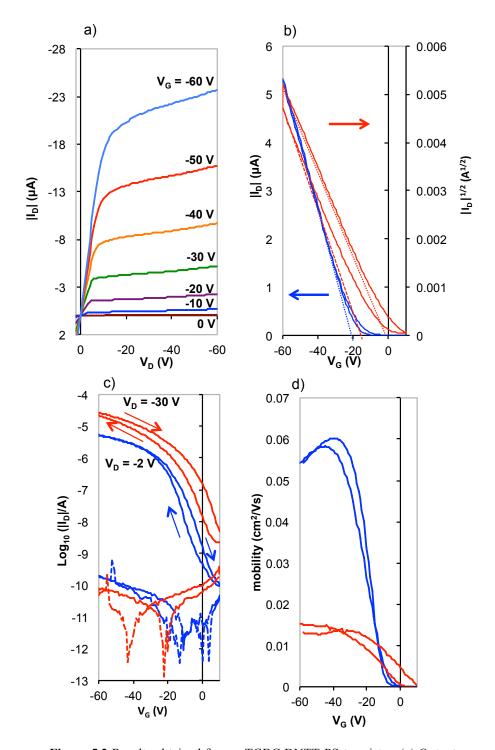

| 5.7 Bottom-gate-top-contact PS transistor characteristics                                |     |

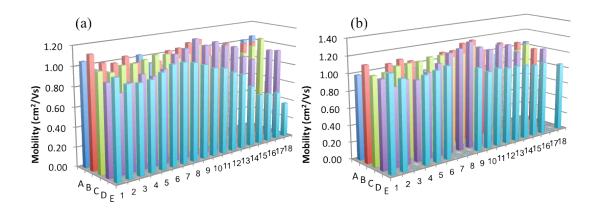

| 5.8 Map of mobilities of PS transistors                                                  |     |

| -                                                                                        |     |

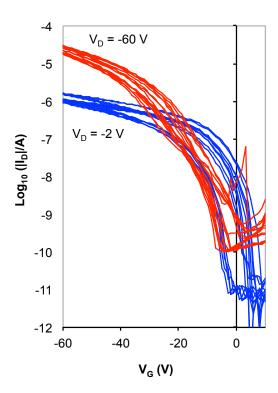

| 6.1 Semi-log transfer plots of 9 TPGDA transistors of identical geometry                 | 101 |

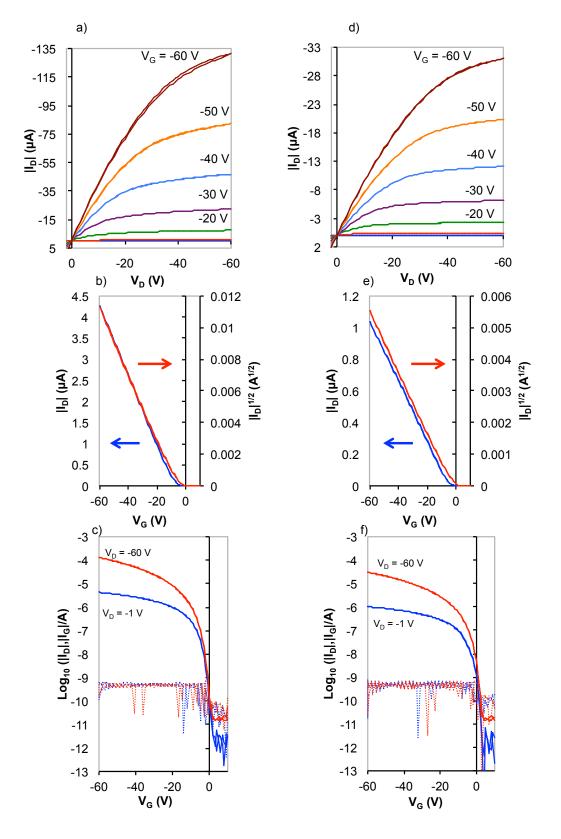

| 6.2 Bottom-gate-top-gate TPGDA transistor characteristics                                | 102 |

| 6.3 Map of mobilities of TPGDA transistors                                               | 104 |

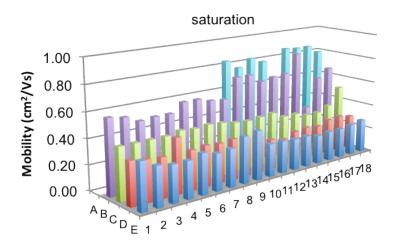

| 6.4 Magnified section of Mask Set 3 showing d <sub>p</sub>                               | 110 |

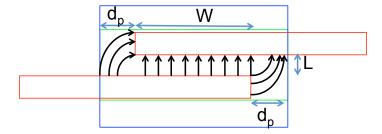

| 6.5 Slow polarisation of ionic species leading to parasitic current                      |     |

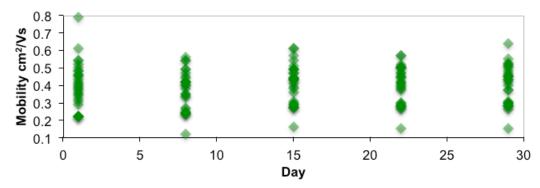

| 6.6 The maximum saturation mobilities of 29 TPGDA transistors over 29 days               |     |

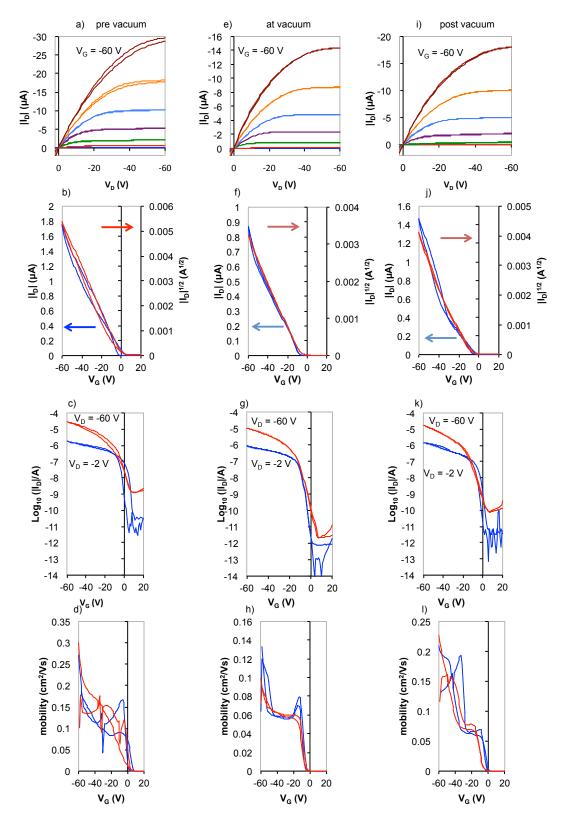

| 6.7 Characteristics of TPGDA in ambient and under vacuum                                 |     |

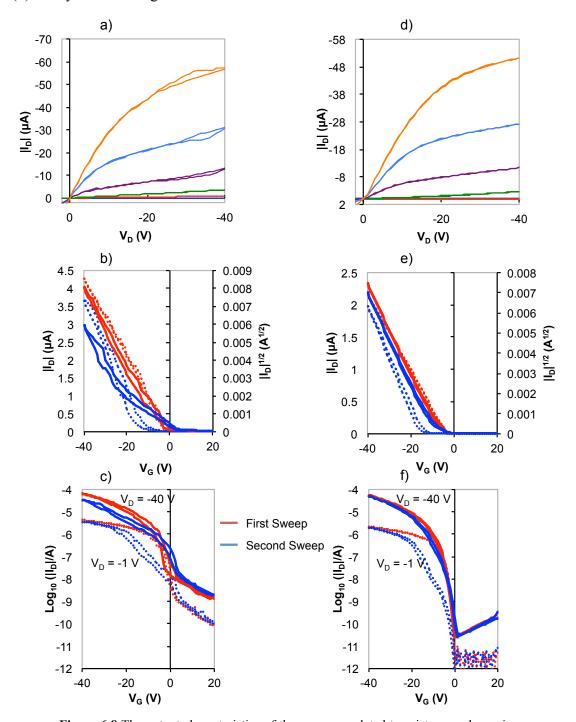

| 6.8 Characteristics of unencapsulated and encapsulated TPGDA transistors                 |     |

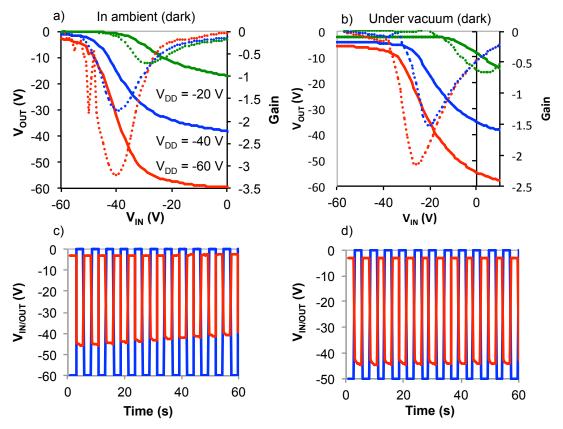

| 6.9 Voltage transfer and square wave response of TPGDA inverters                         |     |

| 0.9 Voltage transfer and square wave response of 11 ODA inverters                        | 123 |

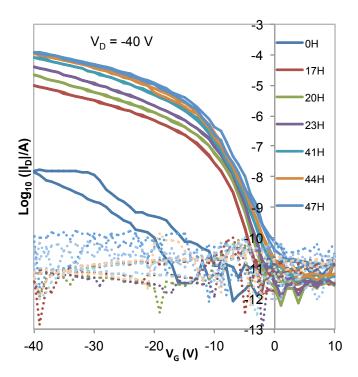

| 7.1 Saturation semi-log plots of a PS-TPGDA transistor taken over 48 hours               | 130 |

| 7.2 Semi-log transfer plots of 9 PS-TPGDA transistors of identical geometry              | 131 |

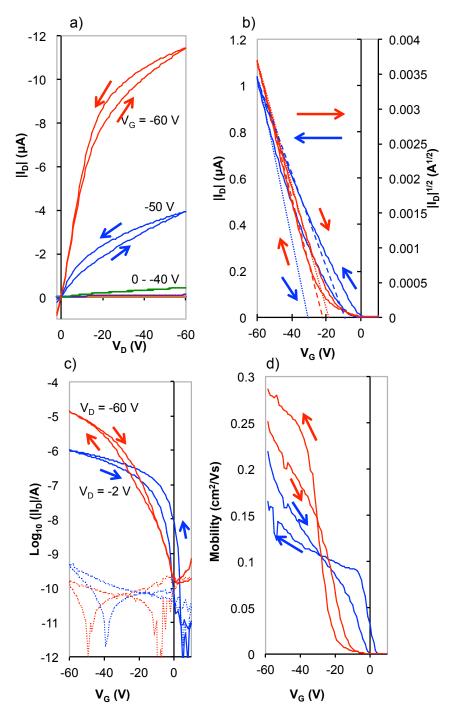

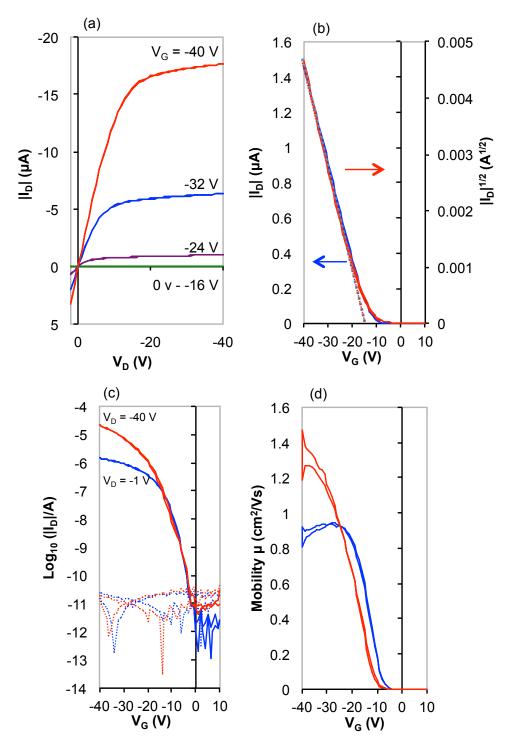

| 7.3 Characteristics of a PS-TPGDA transistor                                             | 133 |

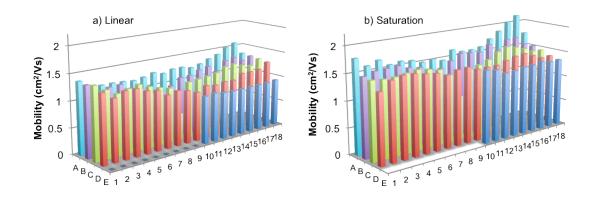

| 7.4 Map of mobilities of PS-TPGDA transistors                                            |     |

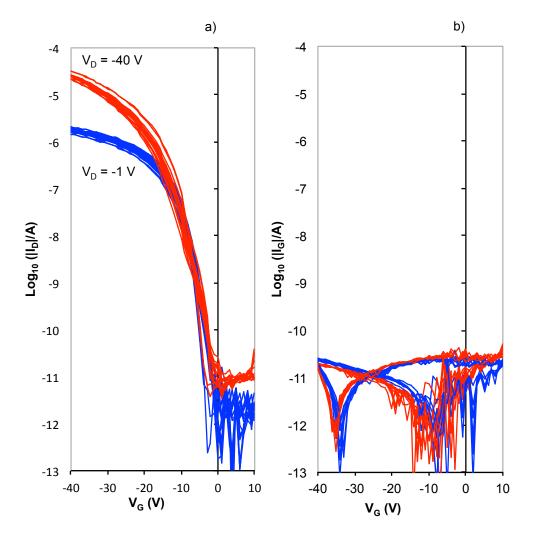

| 7.5 Transfer and semi-log plots of PS-TPGDA transistors after 6 months                   |     |

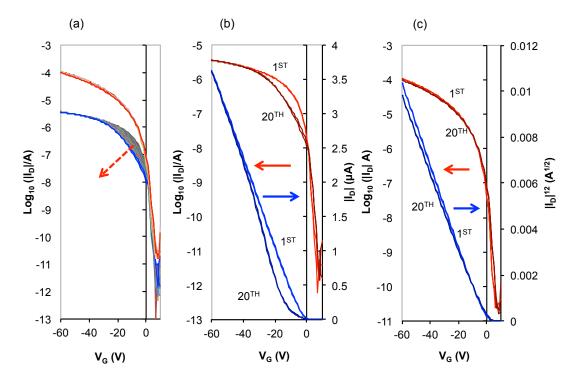

| 7.6 Cycled semi-log transfer plots of PS-TPGDA transistors                               |     |

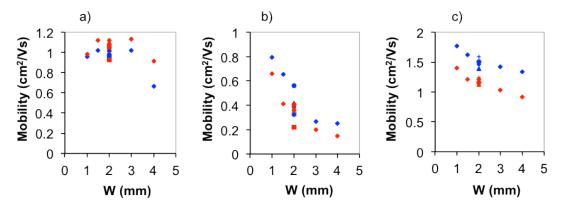

| 7.7 W dependent average mobility of the three dielectric samples                         |     |

| 7.8 Diagram of the channel removal for the analysis of parasitics                        |     |

| 7.9 Characteristics of PS-TPGDA transistor before and after channel is removed.          |     |

|                                                                                          |     |

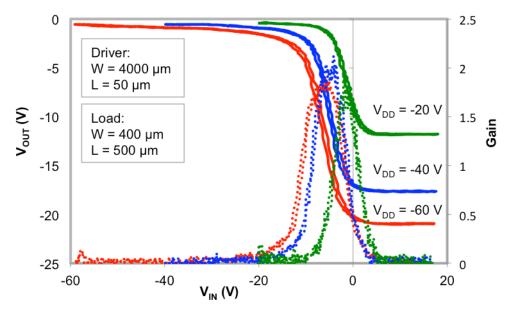

| 7.10 Voltage transfer and gain of PS-TPGDA inverter                                      |     |

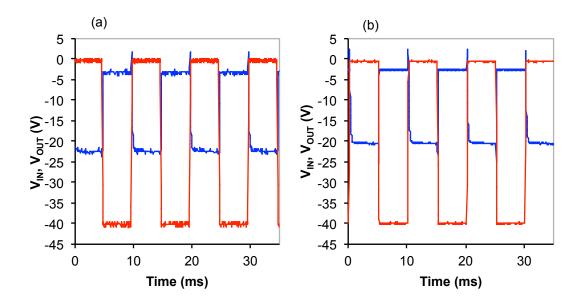

| 7.11 Square wave response of two inverters of different geometry                         |     |

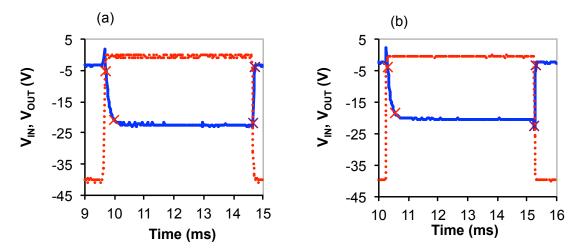

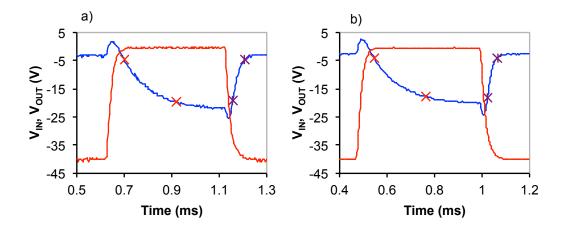

| 7.12 Expanded square wave plots showing switching speed                                  |     |

| 7.13 Square wave response of PS-TPGDA inverters to 1 KHz input signal                    |     |

| 7.14 Expanded square wave plots showing switching speed at 1 KHz                         |     |

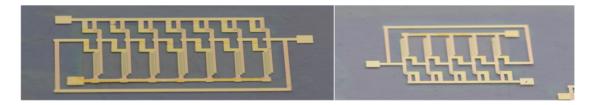

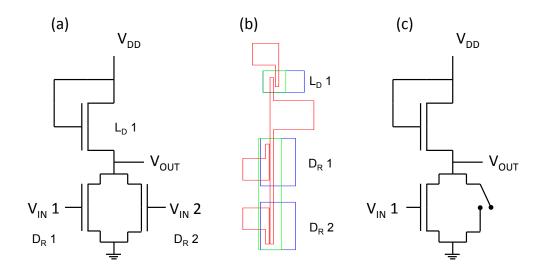

| 7.15 Ring oscillator circuit photographs                                                 | 149 |

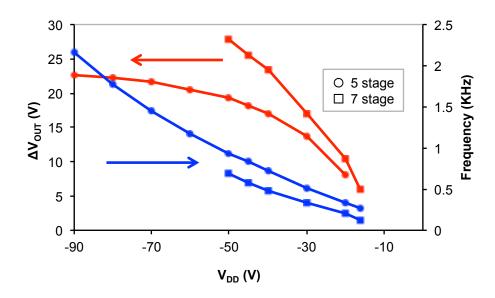

| 7.16 Output frequencies and $\Delta V_{OUT}$ of two ring oscillators                     | 149 |

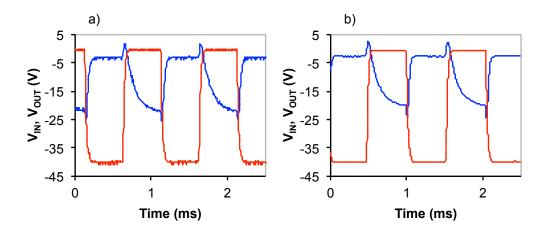

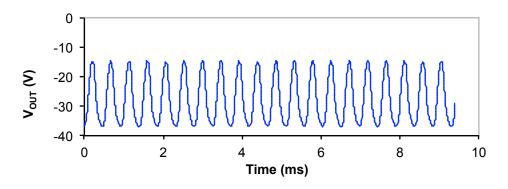

| 7.17 Output signal of a five stage ring oscillator                                       | 150 |

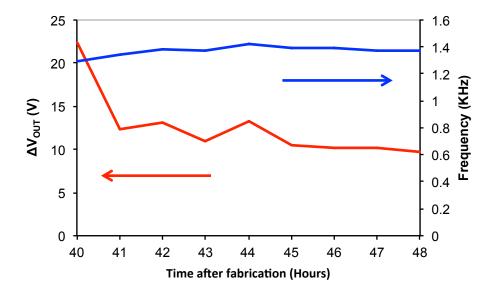

| 7.18 Output frequency and $\Delta V_{OUT}$ of a seven stage ring oscillator over 8 hours | 151 |

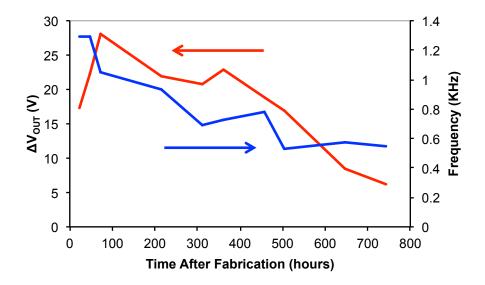

| 7.19 Output frequency and $\Delta V_{OUT}$ of a seven stage ring oscillator over 31 days | 152 |

|                                                                                          |     |

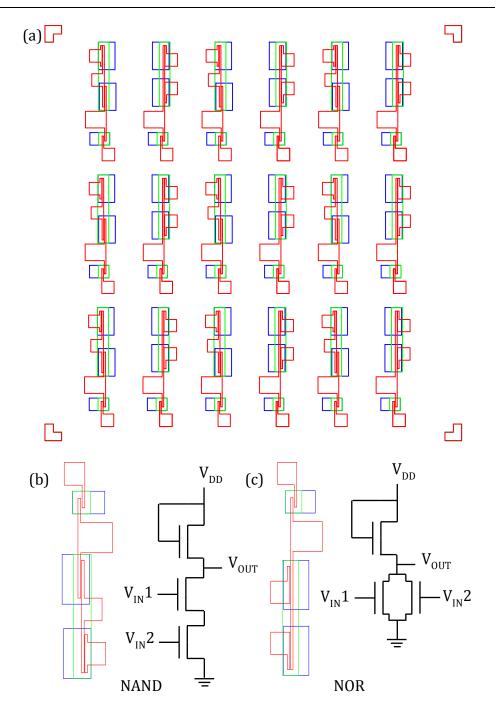

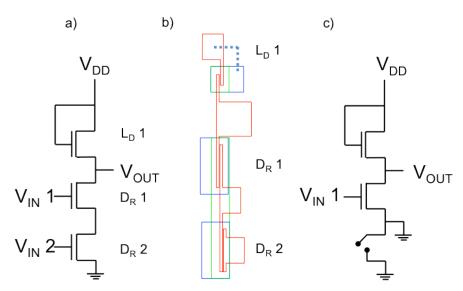

| 8.1 Circuit schematic and mask design of a NOR gate                                      |     |

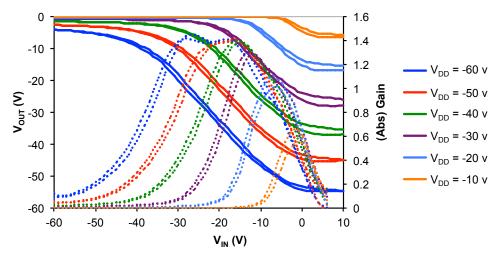

| 8.2 Voltage transfer and gain of a PS-TPGDA NOR inverter                                 |     |

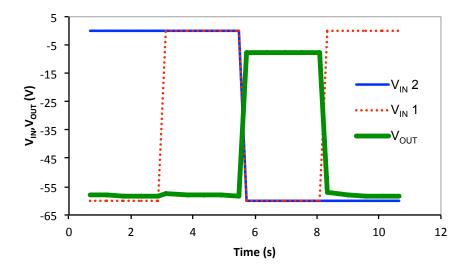

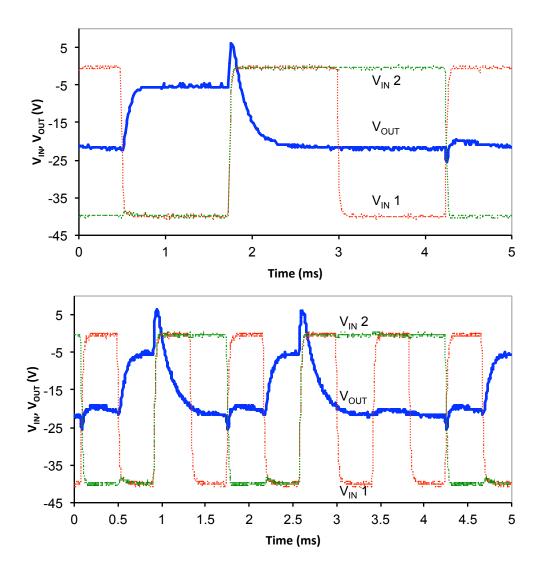

| 8.3 Preliminary NOR gate response measurement                                            |     |

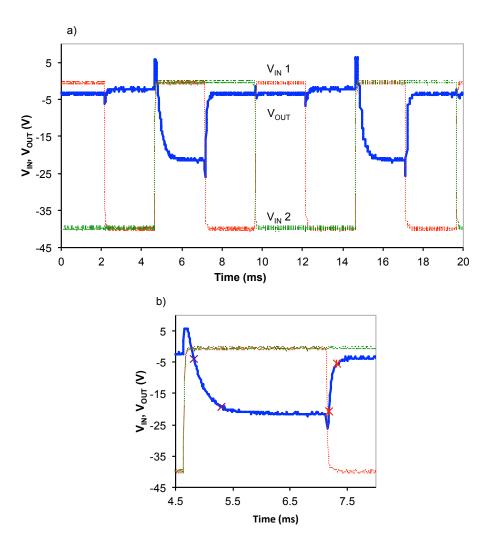

| 8.4 100 Hz NOR gate response and expanded section                                        |     |

| 8.5 NOR gate response to higher frequency input signals                                  | 163 |

| 8.6 Circuit schematic and mask design of a NAND gate                                     | 164 |

| 8.7 Voltage transfer and gain of a PS-TPGDA NAND inverter                                | 165 |

| 8.8 Preliminary NAND gate response measurement                                           | 166 |

| 8.9 100 Hz NAND gate response and expanded section                                       |     |

| 8.10 NAND gate response to higher frequency input signals                                |     |

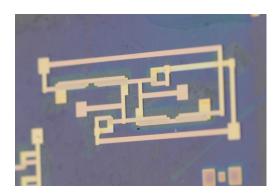

| 8.11 Photograph of a NAND SR Flip-flop circuit                                           |     |

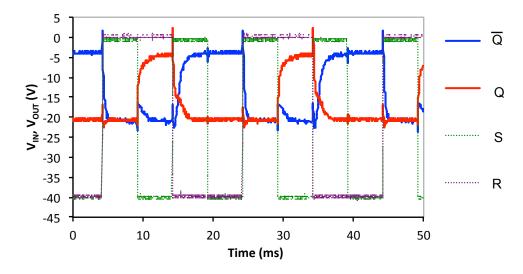

| 8.12 NAND SR Flip-flop response to two input signal S and R                              |     |

|                                                                                          |     |

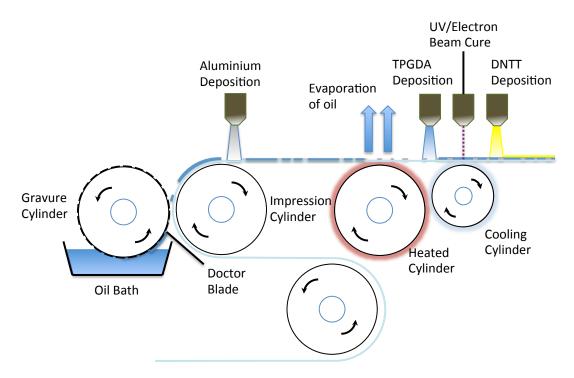

| 9.1 Envisioned R2R process                                                               | 179 |

## List of Tables

| 2.1 HOMO and LUMO levels of various semiconductors                                      | 15  |

|-----------------------------------------------------------------------------------------|-----|

| 2.2 Various characteristics of a number of common semiconductors                        | 23  |

| 2.3 Properties of some common dielectrics                                               | 26  |

| $4.1\ Average\ mobilities\ of\ SiO_2/DNTT\ transistors\ for\ different\ DNTT\ samples\$ | 80  |

| 5.1 Average mobilities for different transistor geometries on PS dielectric             | 94  |

| 6.1 Average mobilities for different transistor geometries on TPGDA dielectric          | 105 |

| 6.2 Table detailing d <sub>p</sub> for the different device geometries                  | 110 |

| 7.1 Properties of a PS-TPGA inverter                                                    | 145 |

| 8.1 Properties of a PS-TPGDA NOR inverter                                               | 160 |

| 8.2 Properties of a PS-TPGDA NAND inverter                                              | 165 |

## Papers and Poster Presentations

## Papers:

- [1] D. M. Taylor, A. Williams, E. R. Patchett, G. Abbas, Z. Ding, H. Assender, J. J. Morrison, S. G. Yates, "Simulating the Electrical Characteristics of Organic TFTs Prepared by Vacuum Processing", *Journal of Display Technology*, **9**, 877-882, 2013

- [2] E. R. Patchett, A. Williams, Z. Ding, G. A. W. Abbas, H. Assender, J. J. Morrison, S. G. Yates, D. M. Taylor, "A high-yield vacuum-evaporation-based R2R-compatible fabrication route for organic electronic circuits", *Organic Electronics*, 15, 1493-1502, 2014

- [3] G. A. Abbas, Z. Ding, H. E. Assender, J. J. Morrison, S. G. Yeates, E. R. Patchett, D. M. Taylor, "A High-Yielding Evaporation-Based Process for Organic Transistors Based on the Semiconductor DNTT" (re-submitted)

- [4] D. M. Taylor, E. R. Patchett, A. Williams, N. J. Neto, Z. Ding, H. Assender, J. J. Morrison, S. G. Yates, "Organic Digital Logic and Analog Circuits Fabricated in a Roll-to-Roll Compatible Vacuum Evaporation Process" (submitted)

- [5] Z. Ding, G. A. Abbas, H. E. Assender, J. J. Morrison, S. G. Yeates, E. R. Patchett, D. M. Taylor, "Effect of oxygen, moisture and illumination on the stability of dinaptho[2,3-b:2',3'-f]thieno[3,2-b]thiophene OTFTs during operation and storage" (In preparation)

#### **Poster Presentations:**

Materials Research Society (MRS) Spring Meeting 2012, San Francisco, USA. Poster presented: Roll-to-roll Printed Electronics by Vacuum Deposition

International Conference on Organic Electronics (ICOE) 2013, Grenoble, France Poster Presented: A Vacuum Approach to Roll-to-roll Production of Organic Electronics

European Conference on Micro Electronics (ECME) 2013, London, UK Poster Presented: A Vacuum Approach to Roll-to-roll Production of Organic Electronics Giving 100% Yield

## Abstract

The properties of organic electronics allow them to be processed at low temperatures onto flexible substrates, opening up a new and novel field of low-cost high throughput electronics. Up to date, research into the roll-to-roll printing of electronics has concentrated on the use of solution based methods for the deposition of material. That is, the use of solvents, which presents a number of problems. Here the methods used for the deposition of materials were compatible with vacuum deposition processes, avoiding the problems that are encountered with the use of solvents.

First transistors were fabricated using naphtho[2,3-b]naphtho[2',3':4,5]thieno[2,3-d]thiophene (DNTT) semiconductor on Si/SiO<sub>2</sub> substrates to determine if recrystallization alone was a suitable method for the purification of DNTT when compared to sublimation. It was found by transistor transfer measurements that although recrystallized DNTT gave a larger spread in mobilities than sublimated DNTT, it had a higher average saturation mobility, 0.54 cm<sup>2</sup>/Vs compared to 0.36 cm<sup>2</sup>/Vs.

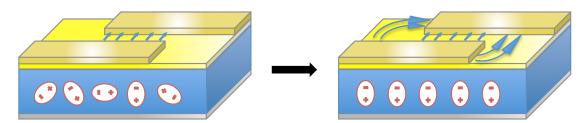

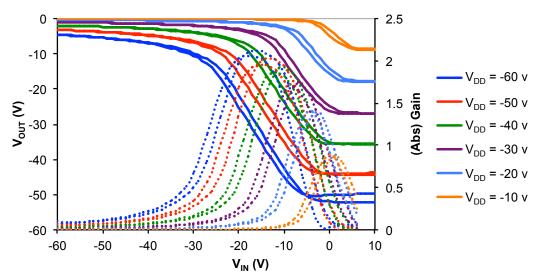

Two transistor configurations were then investigated on poly(ethylene 2,6-naphthalate) (PEN) substrates with polystyrene (PS) dielectric and recrystallized DNTT semiconductor. The performance of top-gate-bottom-contact (TGBC) and bottom-gate-top-contact (BGTC) transistors was evaluated by output and transfer measurements. It was found that the mobilities of the BGTC transistors were significantly higher, an average of 1.01 cm<sup>2</sup>/Vs in the linear regime and 0.97 cm<sup>2</sup>/Vs in the saturation regime, than those of the TGBC transistors,  $\sim$ 0.05 cm<sup>2</sup>/Vs in the linear regime and  $\sim$ 0.016 cm<sup>2</sup>/Vs in the saturation regime. However, despite the high mobility the transistor yield was unacceptably low, at best  $\sim$  65 %. Although the mobilities of the TGBC transistors were relatively low, it was still possible using that configuration to fabricate inverters that had a gain in excess of 1 for a number of rail voltages, (-60 V, -40 V, -20 V = V<sub>DD</sub>).

BGTC Transistors were then fabricated on tri(propylene glycol) diacrylate (TPGDA) dielectric with recrystallized DNTT semiconductor. The average mobility in the saturation regime was found to be 0.44 cm<sup>2</sup>/Vs, lower than for the PS dielectric transistors, and had a dependence on channel width, W, due to device design. However, the device yield was 89%, an improvement on the solution processed device yield. Although the device yield was good, the stability of the devices made it difficult to fabricate inverters with stable operation. Due to the device instability it was not feasible to fabricate more complicated devices.

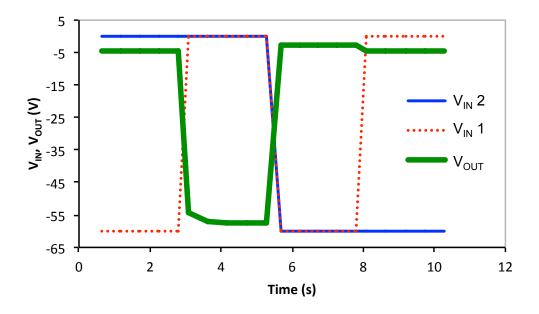

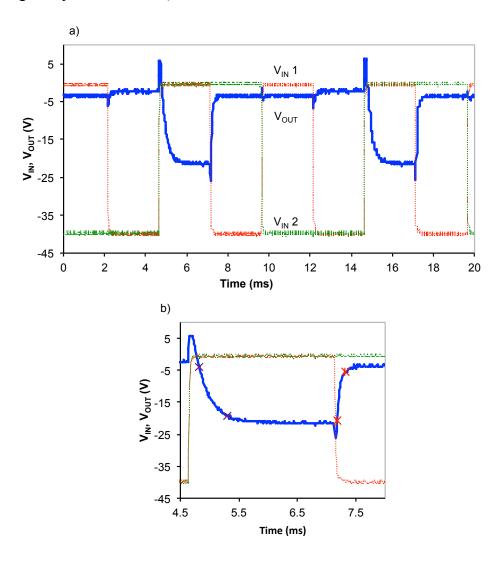

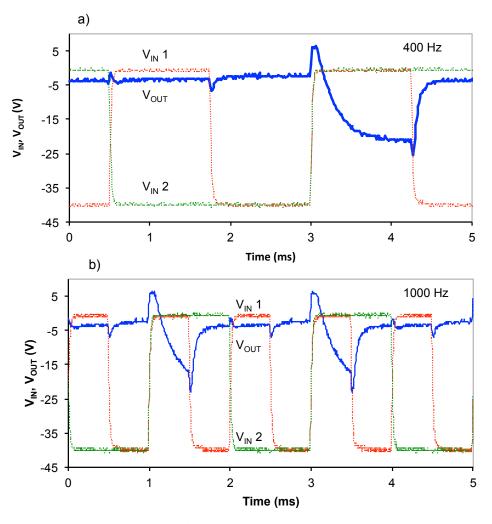

By using a PS buffer layer to improve the surface of TPGDA, transistors with an average saturation mobility of 1.51 cm<sup>2</sup>/Vs were fabricated with a yield of 90%. Here again the mobility was shown to be W dependent, although not to the same degree as for TPGDA/DNTT transistors. Transistors that had been stored under lab conditions for six months in the dark were shown to still have good mobility and stable device operation with no hysteresis. Using the same device configuration it was possible to fabricate working, stable inverters with high switching speeds with total rise and fall times of less than 1 ms. Ring oscillators were also fabricated with output frequencies in the low KHz range, in excess of previously published R2R printed ring oscillators. Functioning NAND and NOR gates were also fabricated with similar switching speeds as the inverters. Finally, a working fully-integrated NAND-based SR Flip-flop gate was also fabricated.

## Acknowledgements

I would like to thank first of all my supervisor Professor Martin Taylor. His experience, knowledge, support and contributions have been invaluable in my development during this project.

I have had the privilege of meeting and working with many friendly and interesting colleagues over the last three years, Daniel, Huw, Elder, Rafael, Nikola, Melanie and Bruno. Thanks to Dr. Collin Watson and Dr. Paul Sayers who have given me their time, help and advice from the day I started.

The work would not have been possible without the assistance of Dr. John Morrison in the preparation of DNTT, Mr. Ziqian Ding for the deposition of the TPGDA, and Mr. Aled Williams for his advice on circuit design and production of the buffer amplifier. I would also like to thank Iwan from the workshop, and Dr. Yanhua Hong for her assistance with AFM work.

Last I would like to thank my family and friends, my parents Sian and John, in particular Donna, who has been somewhat neglected during my write up, for all of their love and support. I would not have completed this without all of you.

## Chapter 1

## Introduction

## 1.1 Introduction

Electronic devices are undeniably an important part of modern day life. Over the last two decades the personal computer has become essential for work and for school, for adults and children alike. A significant proportion of the population would not walk out of the house without a phone in their pocket, and a number find it to be an indispensable tool. More recently such appliances have almost become fashion accessories with a number of modern devices such as tablets combining the features of several different appliances. Industry is currently trying to look at new areas where electronic technology can be adapted. An area that is generating considerable interest is foldable displays [1], with a number of prototypes having been produced. Another example is wearable electronics [2,3], where everyday clothes can harvest energy through the use of organic photovoltaics (OPVs) [4], and store that energy in batteries that are also a flexible woven part the clothing [5].

One of the drawbacks of current technology is the reliance on rigid silicon chips that are produced in batches at a high cost. It means that it can be prohibitively expensive to produce single-use disposable electronics. Products such as displays can only be produced on single pieces of glass at a time, this also limits display size and restricts the display to rigid applications. Concepts such as foldable displays and wearable electronics cannot be produced with such technology. There is a need for new technology where the microelectronics can be flexed without damaging their properties. This would allow such electronics to be produced in a roll-to-roll system, increasing throughput and reducing cost.

Organic semiconductors have lower processing temperatures than their inorganic counterparts. This allows them to be deposited onto flexible substrates that can pass through a roll-to-roll (R2R) system. Although organic semiconductor mobilities are comparatively much lower than the mobilities of inorganics, the idea is not to directly compete with inorganic electronics, but to open up the market for cheap and disposable electronics. Applications for such electronics could include smart

Chapter 1 Introduction

packaging, smart magazines, large area displays and RFID tags. Organic materials are already prevalent in commercial products, particularly display technology. Television and mobile phone displays have already been manufactured that feature organic light emitting diodes (OLEDs).

Currently research into the printing methods for depositing organic materials onto substrates rely heavily on the use of solvents. The solvent acts as a carrier, depositing the organic material onto the substrate as it evaporates away. However, this can lead to several problems that can result in processing bottlenecks and poor device properties.

- 1. Although the solvent evaporates to leave a film of material behind, a certain amount of that solvent will remain trapped within the deposited film. This makes it necessary to anneal the films to remove excess solvent, adding time and heating costs to the production process.

- 2. For a good dielectric to be formed it needs to be pinhole free. Evaporation of solvents can leave pinholes in the deposited films that annealing may not completely remove.

- 3. Solvents have to be carefully selected; when the same solvent is used for sequential layers the previously deposited layer will be removed or damaged. This makes it necessary to have orthogonal solvents. There is also the problem of some semiconductors being highly sensitive to solvents. Semiconductors can be damaged regardless of solubility in the solvent used.

- 4. Solvents tend to be harmful to the environment and can also lead to health and safety issues. Therefore waste solvent capture systems would be an additional but essential cost to a production system.

An alternative route to the R2R production of electronics would be a vacuum deposition approach. Metallisation of polyethylene terephthalate (PET) film is already a commercial process [6], and has been used to pattern antennas. It has also been shown that it is possible to pattern capacitors using the metallisation technique in combination with diffusion pump oil in a process similar to lift-off patterning [6]. Transparent barrier layers have also been deposited using the technique, showing that it may be possible to pattern dielectric layers in this way. Many small molecule semiconductors are already deposited under vacuum in laboratory conditions.

2

Chapter 1 Introduction

In the work to be reported here, R2R compatible vacuum deposition methods will be used to fabricate transistors, and further devices, to demonstrate the suitability of a vacuum 2R2 process as an alternative to conventional R2R printing techniques.

#### 1.2 Thesis Outline

The theoretical background of the work is presented in Chapter 2, which also provides an introduction to how values such as carrier mobility and device capacitance were calculated. The current research in the area of R2R organic electronics is also reviewed.

The experimental methods are given in detail in Chapter 3, together with a list of the fabrication materials that are used – aluminium, gold, tri(propylene glycol) diacrylate (TPGDA), polystyrene (PS) and naphtho[2,3-b]naphtho[2',3':4,5]thieno[2,3-d]thiophene (DNTT).

Experimental results for transistors fabricated from different samples of DNTT on SiO<sub>2</sub> substrates are presented in Chapter 4. The results are used to determine whether recrystallization is a suitable purification method for DNTT when compared against the more conventional method of sublimation.

In Chapter 5 experimental results for DNTT transistors on a polystyrene dielectric are presented. Here also the characteristics of bottom-gate and top-gate transistors are investigated to determine the best configuration for transistor fabrication. The work here was also used to demonstrate the failing of solution processing in terms of device yield.

All-evaporated transistor experimental results are presented in Chapter 6. Here, for the first time in this work, only vacuum R2R techniques were used to fabricate transistors. This work was undertaken to demonstrate the high transistor yield of the fabrication processes used.

In Chapter 7, results are presented for transistors fabricated on a polystyrene (PS) buffered dielectric. It also contains experimental results for inverters and ring oscillators. Work here was undertaken to demonstrate the true capability of the vacuum R2R processes.

3

Chapter 1 Introduction

Experimental results for logic devices fabricated using the same techniques as for the transistors in Chapter 7 are presented in Chapter 8. This work was undertaken to further demonstrate the capability of the vacuum R2R compatible processes.

The conclusions from this work are presented in Chapter 9, together with ideas for further work in pursuit of an all-evaporated R2R system for the production of electronics.

## 1.3 References

- [1] J. C. Lee, S. E. Hudson, E. Tse, "Foldable interactive displays", *Proceedings* of the 21st annual ACM symposium on User interface software and technology, 287-290, 2008.

- [2] X. M. Tao, "Wearable electronics and photonics", Elsevier, 2005

- [3] S. Wagner, E. Bonderover, W. B. Jordan, J. C. Sturm. "Electrotextiles: concepts and challenges", *International Journal of High Speed Electronics and Systems*, **12**, 391-399, 2002