## **Bangor University**

#### **DOCTOR OF PHILOSOPHY**

## Advanced study of pentacene-based organic memory structures

Fakher, Sundes

Award date: 2014

Awarding institution: Bangor **University**

Link to publication

**General rights**Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal?

Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

Download date: 29. Jun. 2024

# **Advanced Study of Pentacene-Based Organic Memory Structures**

By

**Sundes Juma Fakher**

A thesis submitted in partial fulfillment for the degree of Doctor of Philosophy

in the

College of Physical and Applied Sciences

School of Electronic Engineering

January 2014

## **Declaration and Consent**

#### **Details of the Work**

I hereby agree to deposit the following item in the digital repository maintained by Bangor University and/or in any other repository authorized for use by Bangor University.

Author Name: Sundes Juma Fakher

Title: Advanced Study of Pentacene-Based Organic Memory Structures

Supervisor/Department: Dr. Mohammed Mabrook/Electronic Engineering

Qualification/Degree obtained: **PhD**

This item is a product of my own research endeavours and is covered by the agreement below in which the item is referred to as "the Work". It is identical in content to that deposited in the Library, subject to point 2 below.

## **Non-exclusive Rights**

Rights granted to the digital repository through this agreement are entirely non-exclusive. I am free to publish the Work in its present version or future versions elsewhere.

I agree that Bangor University may electronically store, copy or translate the Work to any approved medium or format for the purpose of future preservation and accessibility. Bangor University is not under any obligation to reproduce or display the Work in the same formats or resolutions in which it was originally deposited.

## **Bangor University Digital Repository**

I understand that work deposited in the digital repository will be accessible to a wide variety of people and institutions, including automated agents and search engines via the World Wide Web.

I understand that once the Work is deposited, the item and its metadata may be incorporated into public access catalogues or services, national databases of electronic theses and dissertations such as the British Library's EThOS or any service provided by the National Library of Wales.

I understand that the Work may be made available via the National Library of Wales Online Electronic Theses Service under the declared terms and conditions of use (http://www.llgc.org.uk/index.php?id=4676). I agree that as part of this service the

National Library of Wales may electronically store, copy or convert the Work to any approved medium or format for the purpose of future preservation and accessibility. The National Library of Wales is not under any obligation to reproduce or display the Work in the same formats or resolutions in which it was originally deposited.

#### **Statement 1:**

This thesis is the result of my own investigations, except the preparation and deposition of SWCNTs (one of materials that used in this study) were performed in collaboration with the School of Engineering, Durham University, UK.

| Signed | (candidate) |

|--------|-------------|

| Date   |             |

## **Statement 2:**

I agree to deposit an electronic copy of my thesis (the Work) in the Bangor University (BU) Institutional Digital Repository, the British Library ETHOS system, and/or in any other repository authorized for use by Bangor University and where necessary have gained the required permissions for the use of third party material.

#### In addition to the above I also agree to the following:

- 1. That I am the author or have the authority of the author(s) to make this agreement and do hereby give Bangor University the right to make available the Work in the way described above.

- 2. That the electronic copy of the Work deposited in the digital repository and covered by this agreement, is identical in content to the paper copy of the Work deposited in the Bangor University Library, subject to point 4 below.

- 3. That I have exercised reasonable care to ensure that the Work is original and, to the best of my knowledge, does not breach any laws including those relating to defamation, libel and copyright.

- 4. That I have, in instances where the intellectual property of other authors or copyright holders is included in the Work, and where appropriate, gained explicit permission for the inclusion of that material in the Work, and in the electronic form of the Work as accessed through the open access digital

- 5. Repository, or that I have identified and removed that material for which adequate and appropriate permission has not been obtained and which will be inaccessible via the digital repository.

- 6. That Bangor University does not hold any obligation to take legal action on behalf of the Depositor, or other rights holders, in the event of a breach of intellectual property rights, or any other right, in the material deposited.

- 7. That I will indemnify and keep indemnified Bangor University and the National Library of Wales from and against any loss, liability, claim or damage, including without limitation any related legal fees and court costs (on a full indemnity bases), related to any breach by myself of any term of this agreement.

| Signature: | . Date : |

|------------|----------|

|------------|----------|

## **Contents**

| List of Figures                                                                                                                                                                                              | i                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| List of Tables                                                                                                                                                                                               | vi                   |

| Abstract                                                                                                                                                                                                     | vii                  |

| Acknowledgements                                                                                                                                                                                             | xi                   |

|                                                                                                                                                                                                              |                      |

| 1 Introduction                                                                                                                                                                                               | 1                    |

| 1.1 Introduction                                                                                                                                                                                             | 1                    |

| 1.2 Historical bentackground                                                                                                                                                                                 | 3                    |

| 1.3 Organic electronic applications                                                                                                                                                                          | 4                    |

| 1.4 Memory devices                                                                                                                                                                                           | 6                    |

| 1.4.1 Floating gate memory device                                                                                                                                                                            | 8                    |

| 1.5 Outline of the thesis                                                                                                                                                                                    | 9                    |

| References                                                                                                                                                                                                   | 11                   |

| 2 Devices Theory of Organic Electronic                                                                                                                                                                       | 16                   |

| 2.1 Introduction                                                                                                                                                                                             | 16                   |

| 2.2 Organic semiconductors                                                                                                                                                                                   | 17                   |

|                                                                                                                                                                                                              | 17                   |

| 2.2.1 Charge transport in organic semiconductores                                                                                                                                                            | 1 /                  |

| 2.2.1 Charge transport in organic semiconductores                                                                                                                                                            |                      |

|                                                                                                                                                                                                              | 20                   |

| 2.2.2 Small molecular organic semiconductors                                                                                                                                                                 | 20                   |

| 2.2.2 Small molecular organic semiconductors      2.2.3 Polymeric semiconductors                                                                                                                             | 20<br>22<br>23       |

| 2.2.2 Small molecular organic semiconductors  2.2.3 Polymeric semiconductors  2.3 Gate dielectrics                                                                                                           | 20<br>22<br>23       |

| 2.2.2 Small molecular organic semiconductors  2.2.3 Polymeric semiconductors  2.3 Gate dielectrics  2.3.1 Polymer dielectrics                                                                                | 20<br>23<br>25<br>26 |

| 2.2.2 Small molecular organic semiconductors 2.2.3 Polymeric semiconductors 2.3 Gate dielectrics 2.3.1 Polymer dielectrics 2.4 Metal-semiconductor interface                                                 |                      |

| 2.2.2 Small molecular organic semiconductors 2.2.3 Polymeric semiconductors 2.3 Gate dielectrics 2.3.1 Polymer dielectrics 2.4 Metal-semiconductor interface 2.5 Metal-insulator-semiconductor (MIS) devices |                      |

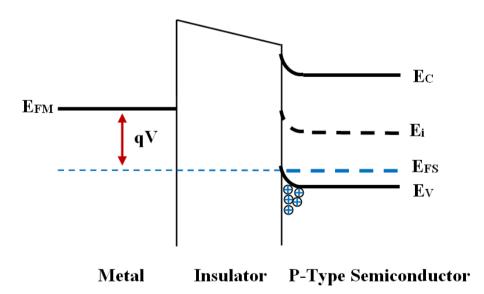

| 2.5.1.1.2 Accumulation mode                                     | 30                                                                                                        |

|-----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| 2.5.1.1.3 Depletion mode                                        | 31                                                                                                        |

| 2.5.1.1.4 Inversion mode                                        | 33                                                                                                        |

| 2.5.1.2 Ideal MIS capacitance-voltage characteristics           | 33                                                                                                        |

| 2.5.2 Doping density                                            | 36                                                                                                        |

| 2.5.3 Equivalent circuits of MIS capacitor                      | 36                                                                                                        |

| 2.6 Organic thin film transistor (OTFT) devices                 | 38                                                                                                        |

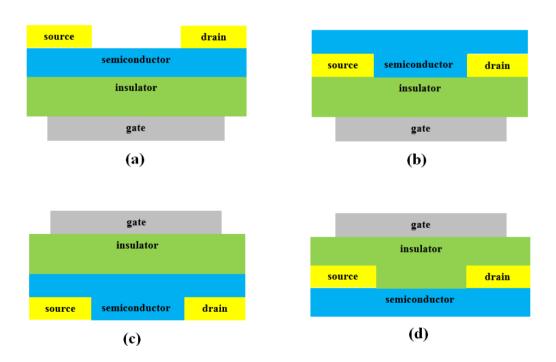

| 2.6.1 Device Structures of OTFTs                                | 39                                                                                                        |

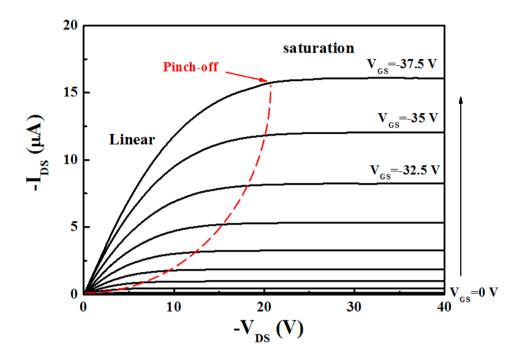

| 2.6.2 Electrical characteristics of OTFTs                       | 41                                                                                                        |

| 2.7 Organic non-volatile memory devices                         | 44                                                                                                        |

| 2.7.1 Floating gate memories                                    | 45                                                                                                        |

| 2.7.2 Characterisation of foating gate memory devices           | 48                                                                                                        |

| 2.7.2.1 Write/Erase processes                                   | 48                                                                                                        |

| 2.7.2.2 Retention properties                                    | 50                                                                                                        |

| References                                                      | 52                                                                                                        |

| 3 Materials and Experimental Techniques                         | 58                                                                                                        |

| 3.1 Introduction                                                | 58                                                                                                        |

| 3.2 Materials                                                   | 59                                                                                                        |

| 3.2.1 Pentacene                                                 | 59                                                                                                        |

| 3.2.2 Poly (methyl methacrylate) (PMMA)                         | 60                                                                                                        |

| 3.2.3 Poly(vinyl phenol) (PVP)                                  | 61                                                                                                        |

| 3.2.4 Poly(3,4-ethylenedioxythiophene) poly(styrenesulfonate) ( |                                                                                                           |

|                                                                 | 02                                                                                                        |

| 3.2.5 Gold nanoparticles (AuNPs)                                | 62.                                                                                                       |

| 3.2.5 Gold nanoparticles (AuNPs)                                |                                                                                                           |

| 3.2.5 Gold nanoparticles (AuNPs)                                | 63                                                                                                        |

| 3.2.6 Single walled carbon nanotubes (SWCNTs)                   | 63                                                                                                        |

| 3.2.6 Single walled carbon nanotubes (SWCNTs)                   |                                                                                                           |

| 3                                                               | 2.5.1.1.3 Depletion mode  2.5.1.1.4 Inversion mode  2.5.1.2 Ideal MIS capacitance-voltage characteristics |

| 3.3.4 Layer-by-layer deposition                                  | 69  |

|------------------------------------------------------------------|-----|

| 3.4 Experimental details                                         | 69  |

| 3.4.1 Substrate preparation                                      | 69  |

| 3.4.2 Film deposition                                            | 71  |

| 3.4.2.1 Metal gate evaporation                                   | 71  |

| 3.4.2.2 Spin coating of the insulator                            | 72  |

| 3.4.2.3 Floating gate deposition                                 | 72  |

| (a) Gold floating gate preparation and deposition                | 73  |

| (b) SWCNTs deposition                                            | 74  |

| 3.4.2.4 Organic semiconductore evaporation                       | 75  |

| 3.4.2.5 Evapotation of metal contacts                            | 76  |

| 3.4.3 Thin film characterization                                 | 76  |

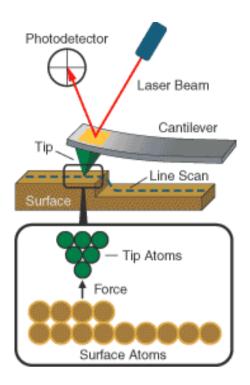

| Atomic force microscopy (AFM)                                    | 76  |

| 3.4.4 Electrical characterisation                                | 78  |

| 3.4.4.1 AC Measurements                                          | 78  |

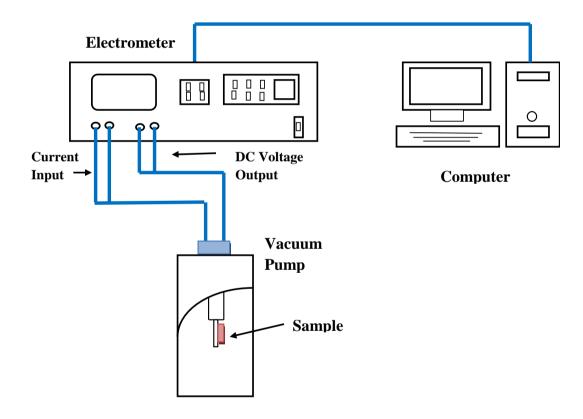

| 3.4.4.2 DC Measurements                                          | 78  |

| References                                                       | 81  |

| 4 Organic Metal-Insulator-Semiconductor (OMIS) Devices           | 88  |

| 4.1 Introduction                                                 | 88  |

| 4.2 Organic metal-insulator-semiconductor capacitor devices      | 89  |

| 4.2.1 PMMA-based OMIS devices                                    | 89  |

| 4.2.1.1 Fabrication process                                      | 89  |

| 4.2.1.2 Surface morphology                                       | 90  |

| 4.2.1.3 Electrical characterisation                              | 95  |

| 4.2.2 PMMA-based OMIS devices whith PEDOT:PSS as the top contact | 99  |

| 4.2.2.1 Electrical characterisation                              | 100 |

| 4.2.3 OMIS capacitor with PVP as insulator                       | 102 |

| 4.2.3.1 Fabrication process                                      | 102 |

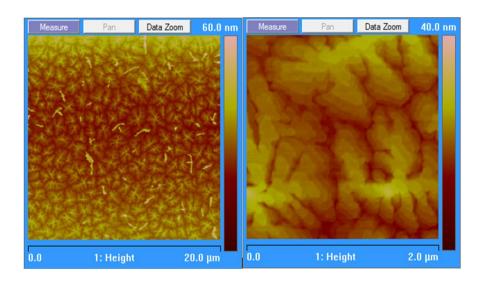

| 4.2.3.2 Surface Morphology                                              | 102 |

|-------------------------------------------------------------------------|-----|

| 4.2.3.3 Electrical characterisation                                     | 104 |

| 4.3 Organic metal-insulator-semiconductor memory devices                | 105 |

| 4.3.1 OMIS memory devices with PMMA as insulator and thin floating gate | -   |

| 4.3.1.1 Fabrication process                                             | 105 |

| 4.3.1.2 Electrical characterisation                                     | 106 |

| 4.3.2 MIS memory devices with PMMA as insulator and with Augate         | •   |

| 4.3.2.1 Fabrication process                                             | 109 |

| 4.3.2.2 Electrical characterisation                                     | 110 |

| 4.3.3 OMIS memory devices with PMMA as insulator and wit floating gate  |     |

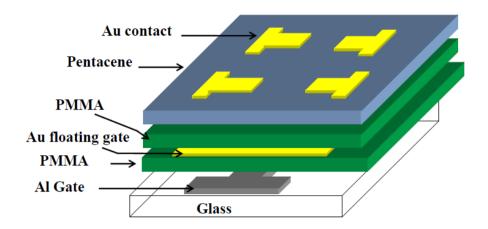

| 4.3.3.1 Fabrication process                                             | 113 |

| 4.3.3.2 Electrical characterisation                                     | 113 |

| 4.3.4 OMIS memory devices with PVP as insulator and with AuNPs a        |     |

| 4.3.4.1 Fabrication process                                             | 115 |

| 4.3.4.2 Electrical characterisation                                     | 117 |

| 4.4 Summary                                                             | 119 |

| References                                                              | 121 |

| 5 Organic Thin Film Transistor (OTFTs)                                  | 125 |

| 5.1 Introduction                                                        | 125 |

| 5.2 PMMA-based OTFTs                                                    | 126 |

| 5.2.1 Device fabrication                                                | 126 |

| 5.2.2 Device optimisation                                               | 127 |

| 5.2.3 Electrical characterisation of OTFTs fabrication process          | 129 |

| 5.3 Repeatability study of OTFTs fabrication                            | 138 |

| 5.4 PVP-based OTFTs                                                     | 140 |

| 5.4.1 Device fabrication                                                | 140 |

|   | 5.4.2 Electrical characterisation                                                   | 141      |

|---|-------------------------------------------------------------------------------------|----------|

|   | 5.5 Bias stress effect in pentacene-based OTFTs device with PMMA as insula          | ator 143 |

|   | 5.5.1 Initial test                                                                  | 143      |

|   | 5.5.2 Gate bias-stress of -40 V at various stress time                              | 144      |

|   | 5.5.3 Various gate bias-stress at 1000 s stress time                                | 147      |

|   | 5.5.4 Various drain bias stress voltages at constants gate bias stress and time     |          |

|   | 5.6 Summary                                                                         | 152      |

|   | References                                                                          | 154      |

| 6 | Organic Thin Film Memory Transistors (OTFMTs)                                       | 158      |

|   | 6.1 Introduction                                                                    | 158      |

|   | 6.2 PMMA-based OTFMTs with thin layer of gold and AuNPs as floating gar             | tes 158  |

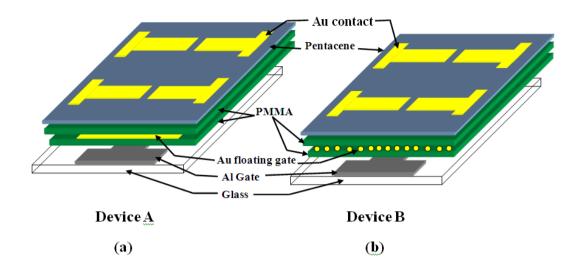

|   | 6.2.1 OTFMT fabrication                                                             | 159      |

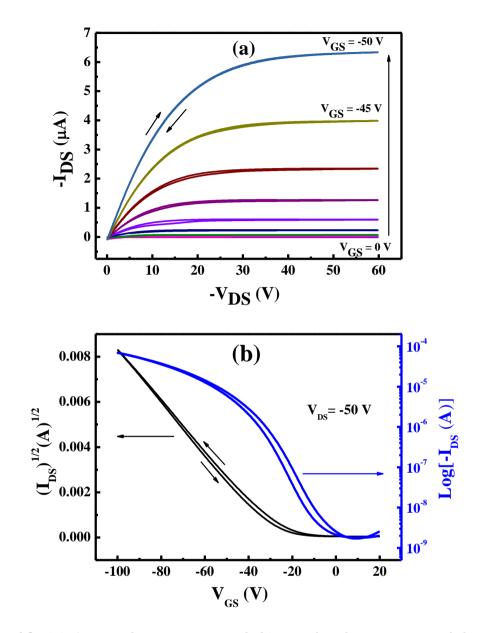

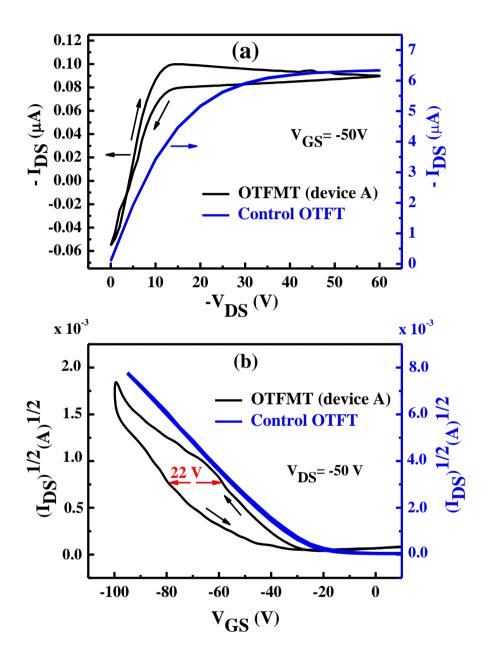

|   | 6.2.2 OTFMTs characterisations                                                      | 160      |

|   | 6.3 PMMA-based OTFMTs, with SWCNTs as the floating gate                             | 175      |

|   | 6.3.1 Fabrication process                                                           | 176      |

|   | 6.3.2 OTFMTs characterisations                                                      | 176      |

|   | 6.4 PVP-based organic thin film memory transistors (OTFMTs), with Au floating gates |          |

|   | 6.4.1 OTFMTs fabrication                                                            | 182      |

|   | 6.4.2 OTFM characterisation                                                         | 183      |

|   | 6.5 Summary                                                                         | 188      |

|   | References                                                                          | 191      |

| 7 | Conclusions and Further Work                                                        | 194      |

|   | 7.1 Conclusions                                                                     | 194      |

|   | 7.2 Further work                                                                    | 198      |

|   | Publications                                                                        | 199      |

# **List of Figures**

| 1.1  | Evolution of carrier mobility in organic field-effect transistor4                                                   |

|------|---------------------------------------------------------------------------------------------------------------------|

| 1.2  | A typical applications of organic electronic technology                                                             |

| 1.3  | A classification of memory devices technologies                                                                     |

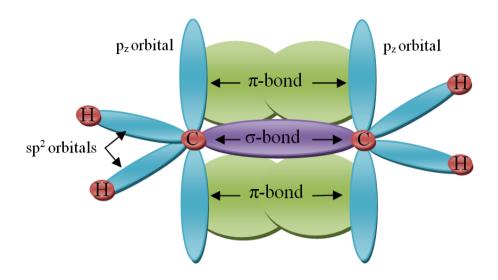

| 2.1  | Diagram of the bonds and orbital for two sp <sup>2</sup> -hybridised of carbon atoms18                              |

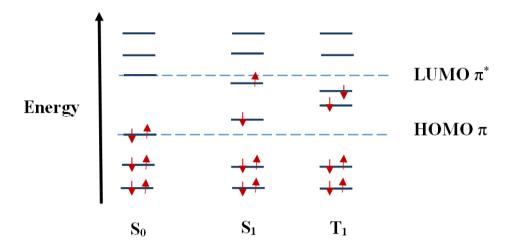

| 2.2  | Molecular orbital diagrams corresponding to the electronic ground and excited states                                |

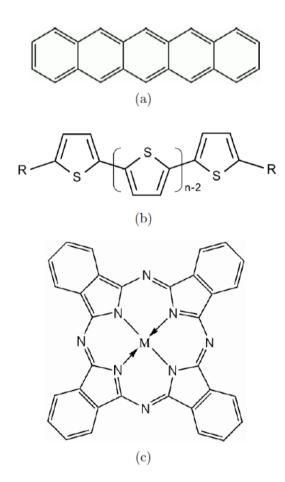

|      | Chemical structure of (a) pentacene, (b) oligothiophenes and (c) meta phthalocyanine                                |

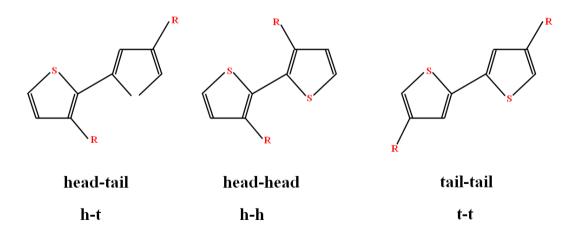

|      | Chemical structure of poly(3-alkylthiophene) with different couplings of pairs of monomers                          |

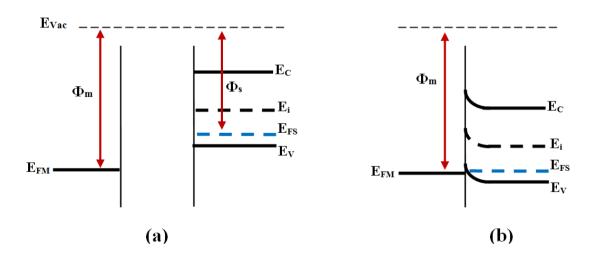

| 2.5  | Ohmic contact formation between a metal and a p-type semiconductor (a) before and (b) they are brought into contact |

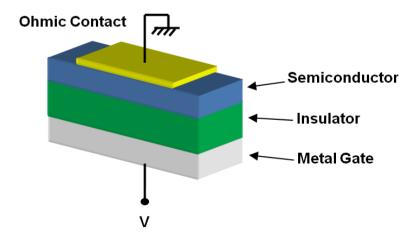

| 2.6  | Schematic diagram of an MIS structure                                                                               |

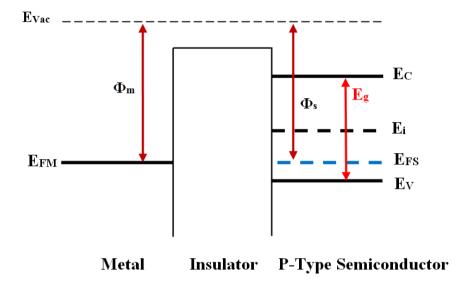

| 2.7  | Energy band diagram of an ideal p-type-based MIS capacitor at flatband condition 29                                 |

|      | Energy band diagram of an ideal p-type-based MIS capacitor in accumulation mode                                     |

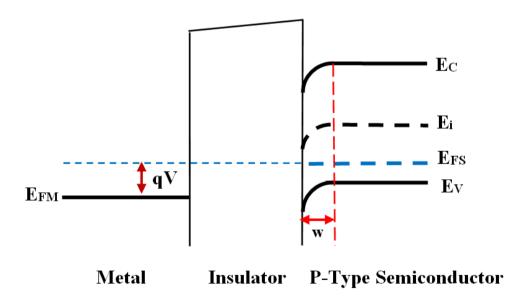

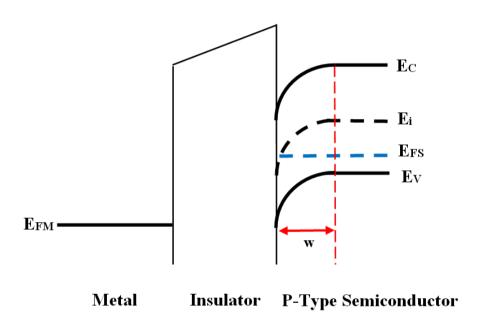

| 2.9  | Energy band diagram of an ideal p-type-based MIS capacitor in depletion mode 31                                     |

| 2.10 | Energy band diagram of an ideal p-type-based MIS capacitor in inversion mode                                        |

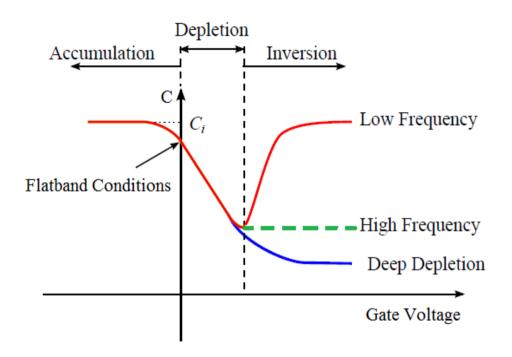

| 2.11 | Capacitance-voltage (C-V) response of an ideal MIS capacitor structure34                                            |

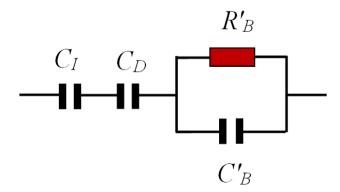

| 2.12 | Equivalent circuit for a MIS capacitor device in accumulation region                                                |

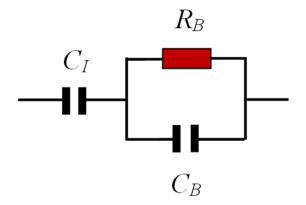

| 2.13 | Equivalent circuit for a MIS capacitor device in depletion region37                                                 |

| 2.14 | Schematic diagrams of OTFTs configurations                                                                          |

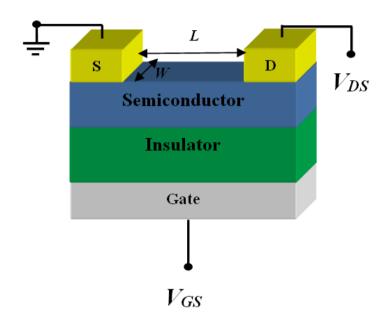

| 2.15 | Structure of bottom-gate, top-contact thin-film transistor TFT41                                                    |

| 2.16 | Output characteristics for a typical OTFT based on a p-type semiconductor42                                         |

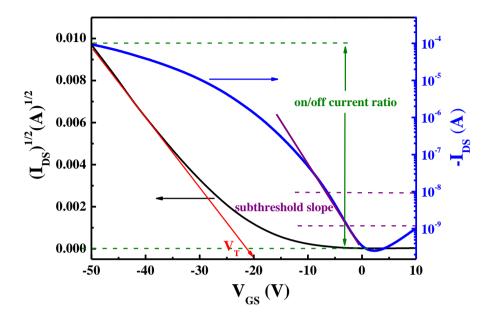

| 2.17 | Transfer characteristics for a typical OTFT based on a p-type semiconductor44                                       |

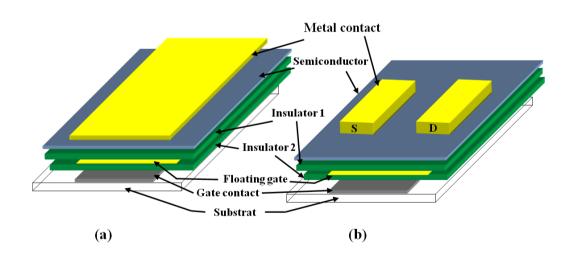

| 2.18 | Basic structure of floating gate memory based on (a) MIS. (b) TFT devices45                                         |

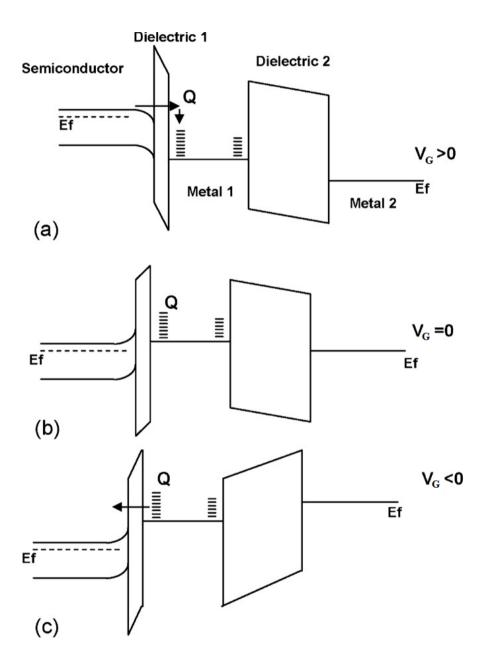

| 2.19 | Energy band structures of floating gate-based memory device under different gate voltages47                                                                                                          |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

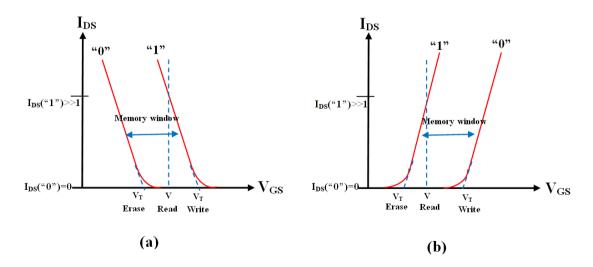

| 2.20 | The write and erase operations for a floating gate memory device based on TFTs                                                                                                                       |

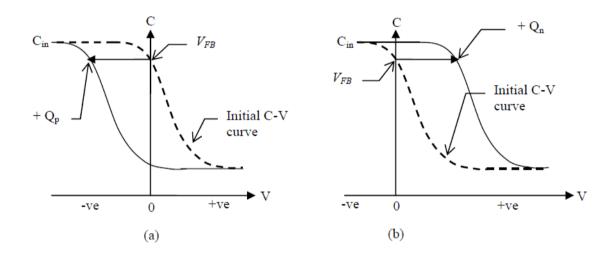

| 2.21 | Typical C-V characteristics of MIS-based memory structure with (a) positive charge, $Q_p$ , and (b) negative charge $Q_n$ in the floating gate50                                                     |

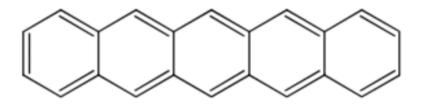

| 3.1  | Structure of a pentacene molecule                                                                                                                                                                    |

| 3.2  | Molecular structure of Poly(methyl methacrylate) (PMMA)60                                                                                                                                            |

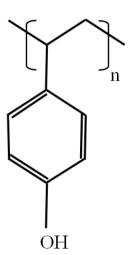

| 3.3  | Molecular structure of Poly(vinyl phenol) (PVP)61                                                                                                                                                    |

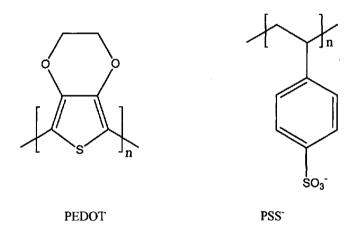

| 3.4  | Molecular structure of PEDOT: PSS                                                                                                                                                                    |

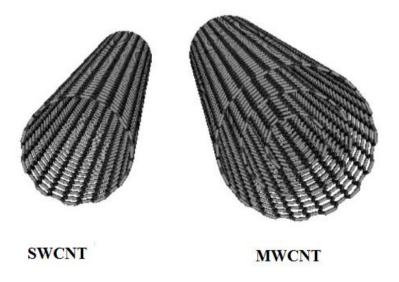

| 3.5  | Molecular structure of a SWCNT and a MWCNT64                                                                                                                                                         |

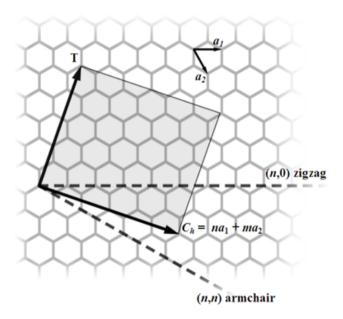

| 3.6  | The $(n, m)$ nanotube naming scheme of a chiral vector $(C_h)$ in the honeycomb graphene sheet of SWCNT                                                                                              |

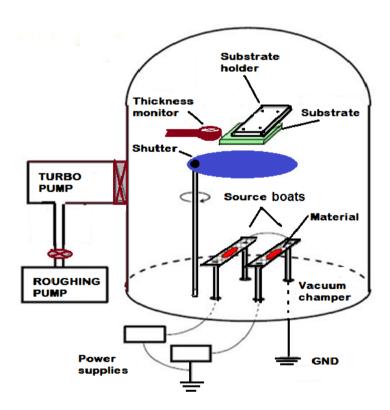

| 3.7  | Schematic diagram of a Kurt Lesker mini-spectros system                                                                                                                                              |

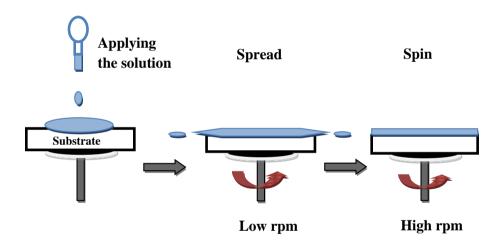

| 3.8  | Schematic diagram of spin coating process                                                                                                                                                            |

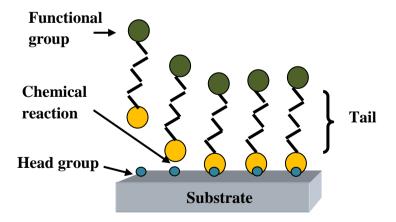

| 3.9  | Representation of a Self- assembly monolayer (SAM) structure                                                                                                                                         |

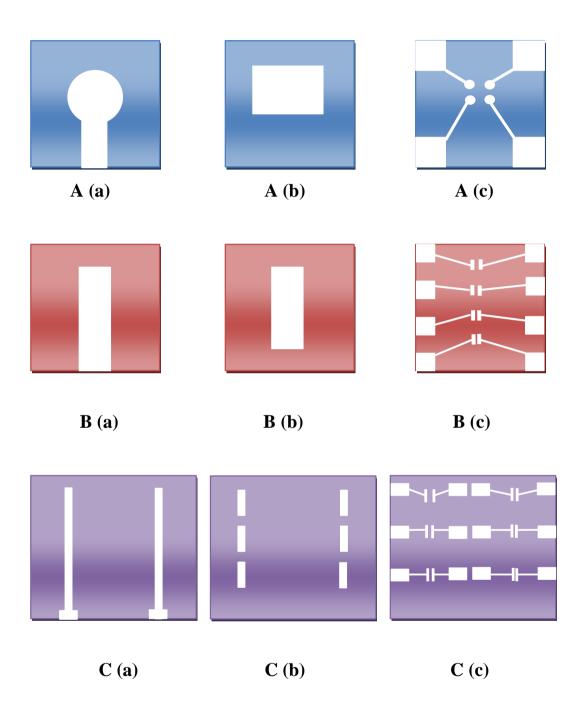

| 3.10 | The three types of shadow mask70                                                                                                                                                                     |

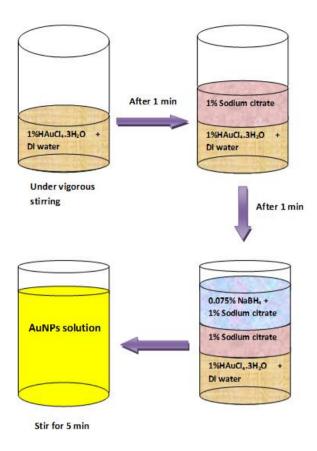

| 3.11 | Preparation method of gold nanoparticles (AuNPs) solution                                                                                                                                            |

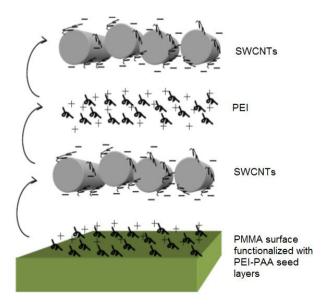

| 3.12 | 2 A schematic of the layer-by-layer SWCNTs deposition technique75                                                                                                                                    |

| 3.13 | Schematic diagram of atomic force microscopy (AFM)78                                                                                                                                                 |

| 3.14 | Diagram of experimental setup for electrical characterisation for MIS, TFTs and TFMTs samples                                                                                                        |

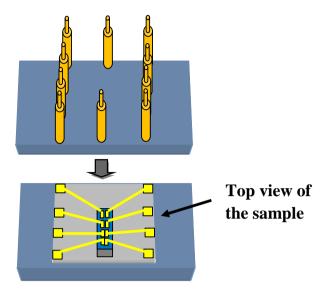

| 3.15 | The sample holder test used for charge injection device measurements and the top view of the sample80                                                                                                |

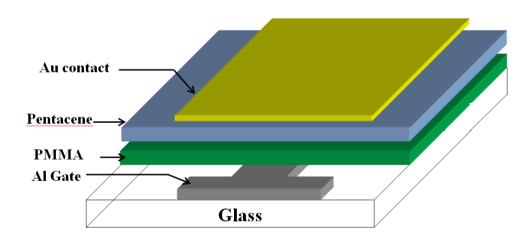

| 4.1  | Schematic diagram of PMMA-based OMIS capacitor structure                                                                                                                                             |

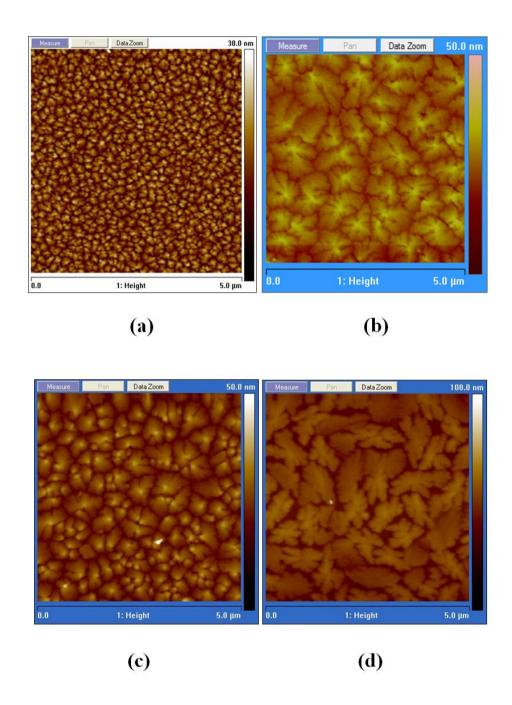

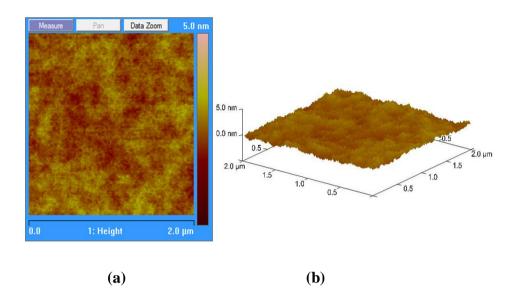

| 4.2  | AFM images of 50 nm pentacene film deposited on 150 nm PMMA at rates of (a) $0.05 \text{ nm s}^{-1}$ (b) $0.03 \text{ nm s}^{-1}$ (c) $0.01 \text{ nm s}^{-1}$ and (d) $0.0015 \text{ nm s}^{-1}$ 91 |

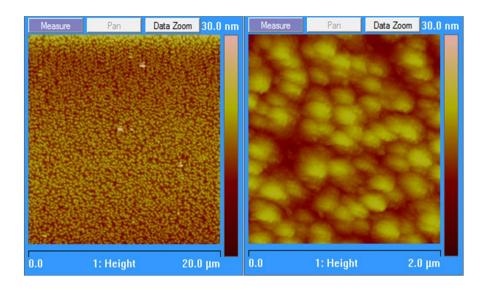

| 4.3  | AFM images of 50 nm pentacene films deposited at rate of 0.03 nm s <sup>-1</sup> on (a) 50 nm and (b) 300 nm thickness of PMMA93                                                                     |

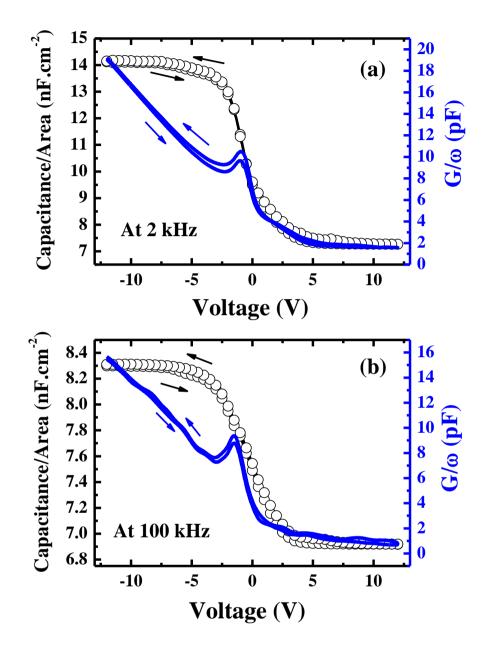

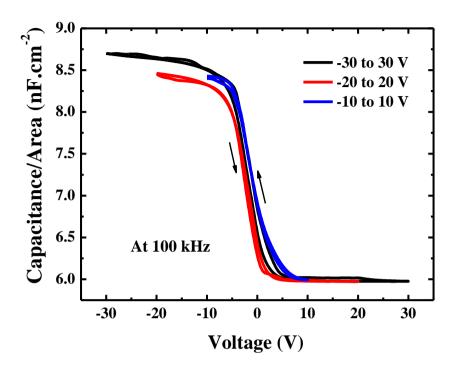

| 4.4  | C-V and G/ω-V characteristics for Al/PMMA/pentacene/Au structure96                                                                                                                                   |

| 4.5  | Capacitance per unit area versus voltage for Al/PMMA/pentacene/Au structure addifferent voltage sweeps                                                                                               |

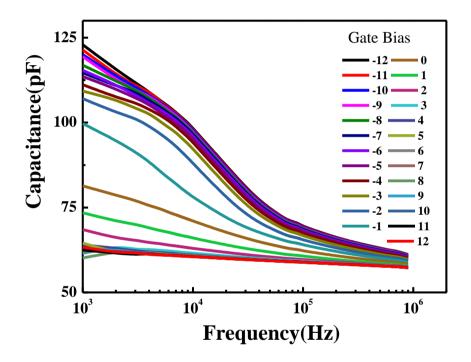

| 4.6  | Capacitance versus frequency characteristics of Al/PMMA/pentacene/Au structure at different bias voltages                                                                                            |

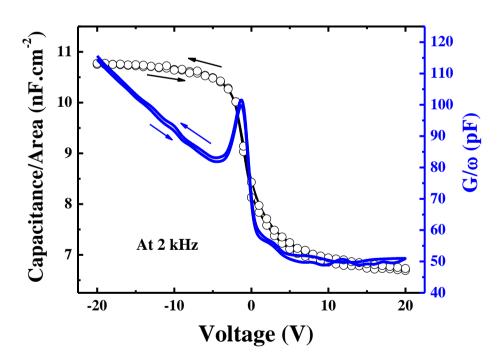

| 4.7  | C-V and G/ $\omega$ -V curves for Al/PMMA/pentacene/PEDOT:PSS structure100                                                                                                                                |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

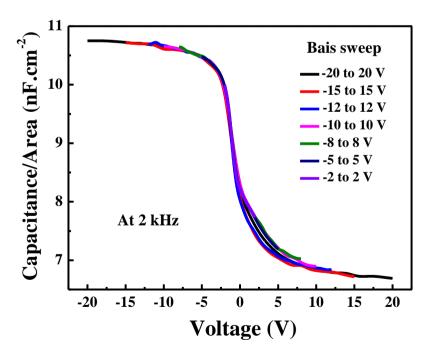

| 4.8  | Capacitance per unit area versus voltage for Al/PMMA/pentacene/PEDOT: PSS structure                                                                                                                       |

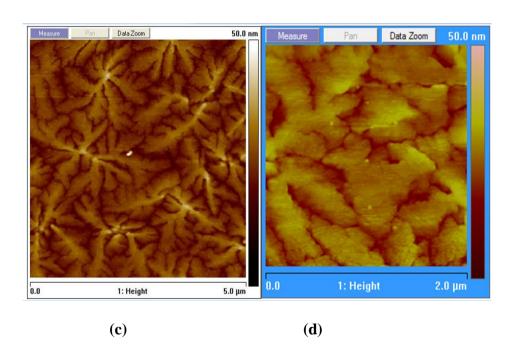

| 4.9  | AFM images of (a) PVP layer on Al gate layer with area scan size 2 $\mu$ m, (b) 3D surface plot for PVP on Al, and deposited pentacene film on PVP with scan area size of (c) 5 $\mu$ m and (d) 2 $\mu$ m |

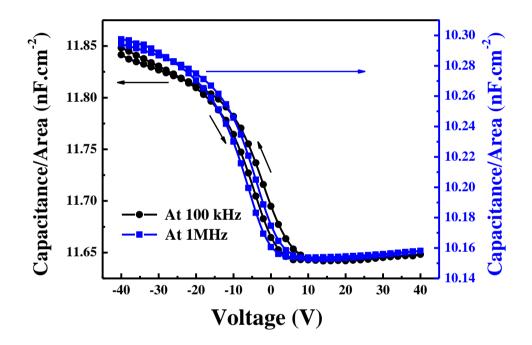

| 4.10 | C-V characteristic curves for Al/PVP/pentacene/Au structure at frequencies of 100 kHz and 1 MHz                                                                                                           |

| 4.11 | Schematic diagram of Al/PMMA/Au/PMMA/pentacene/Au memory structure                                                                                                                                        |

| 4.12 | 2 C-V characteristics at 1MHz for the MIS memory and control structures107                                                                                                                                |

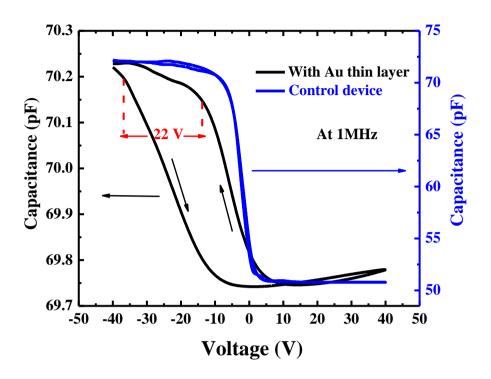

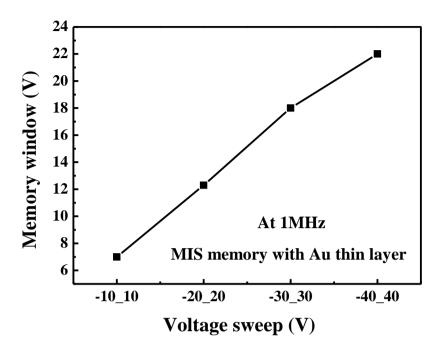

| 4.13 | The memory window (flat-band voltage shift) versus the voltage sweep range for MIS memory device with Au thin layer floating gate                                                                         |

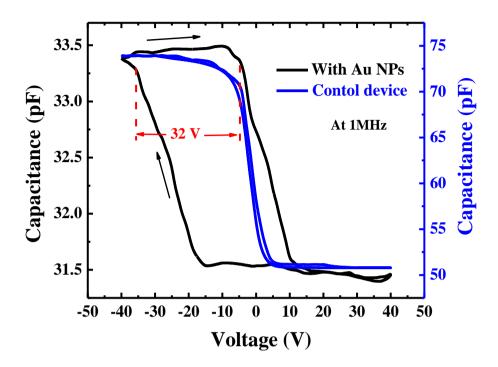

| 4.14 | 4 C-V characteristics at 1MHz for the MIS memory and control structure devices (with and without AuNPs floating gate)                                                                                     |

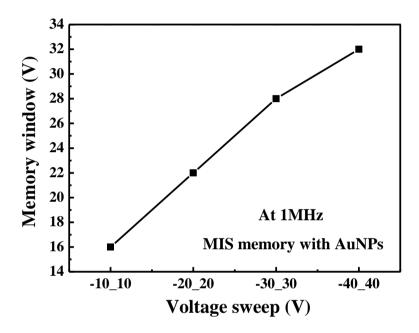

| 4.15 | The memory window versus the voltage sweep range for MIS memory device with AuNPs floating gate                                                                                                           |

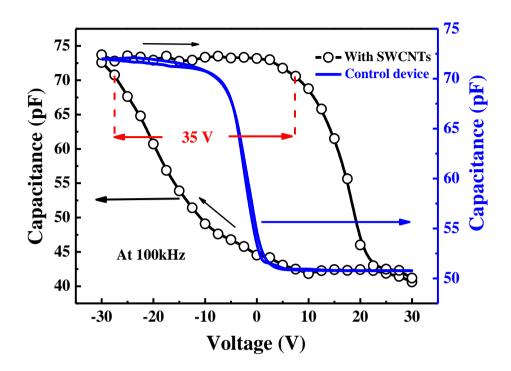

| 4.16 | 6 C-V characteristics for the SWCNTs-based MIS memory and control devices 114                                                                                                                             |

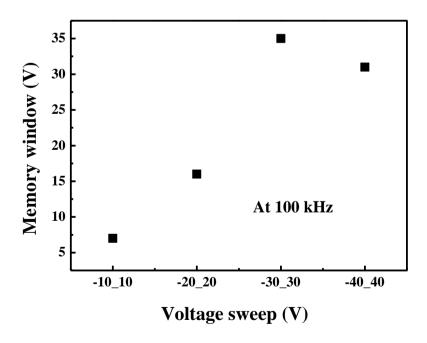

| 4.17 | 7 The memory window (flat-band voltage shift) versus voltage sweep range for SWCNT-based MIS memory devices                                                                                               |

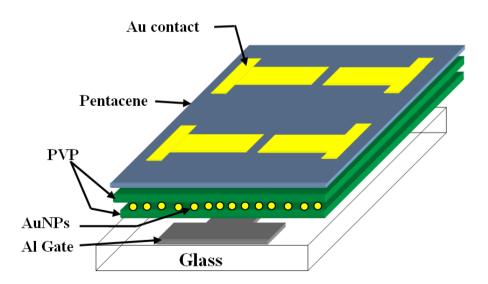

| 4.18 | Schematic diagram of Al/PVP/AuNPs/PVP/pentacene/Au MIS memory structure                                                                                                                                   |

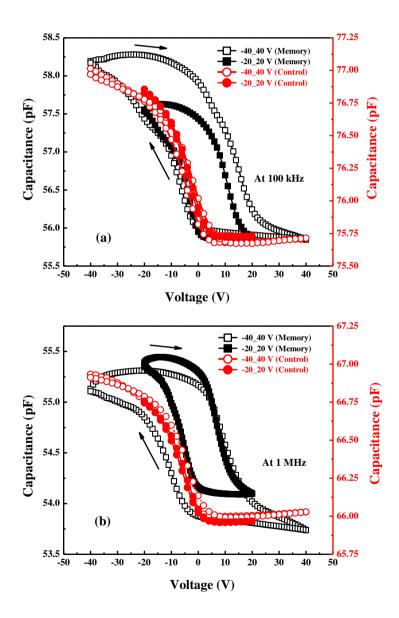

| 4.19 | C-V characteristic curves of double voltage sweep ± 20 V and ± 40 V for Al/PVP/AuNPs/PVP/Pentacene/Au MIS memory structures                                                                               |

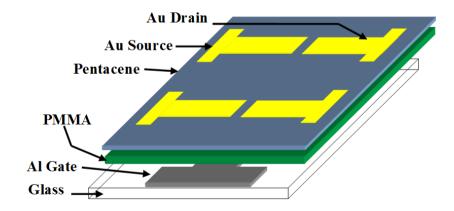

| 5.1  | Schematic diagram of PMMA-based OTFT structure                                                                                                                                                            |

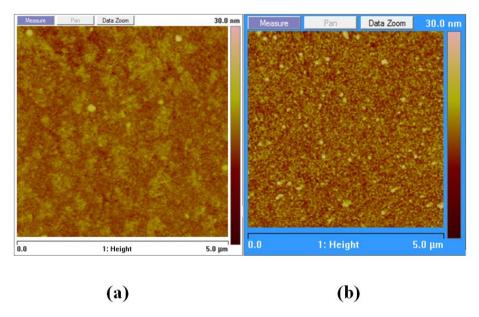

| 5.2  | AFM images of 50 nm gold contacts grown on 50 nm pentacene, (a) deposited after 7 days of the deposition of pentacene, and (b) directly evaporated after the evaporation of pentacene                     |

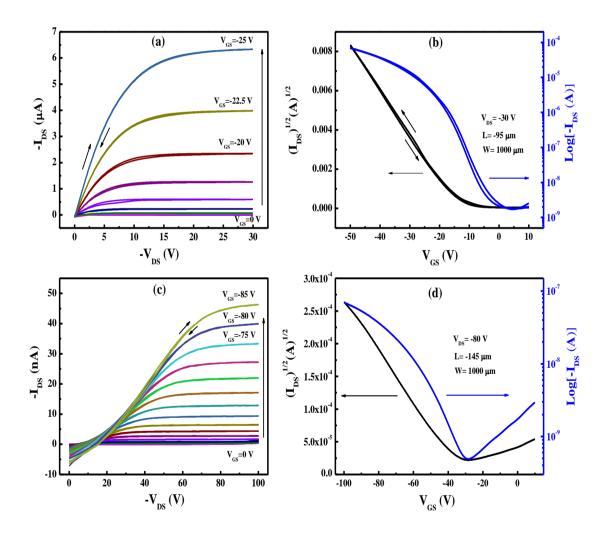

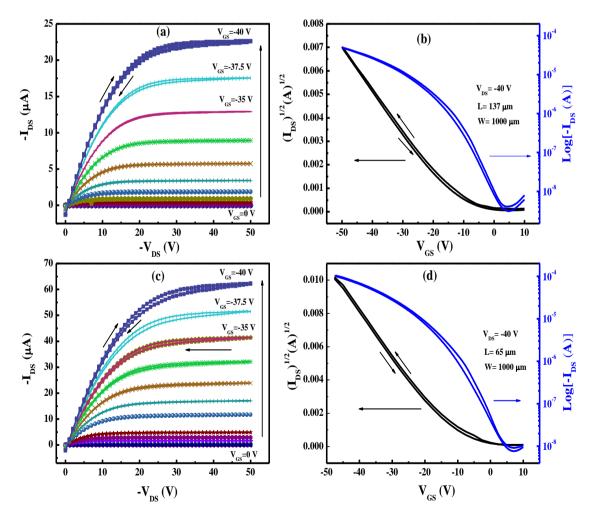

| 5.3  | The output and transfer characteristics of PMMA- based OTFTs, (a) and (b) for optimized devices and, (c) and (d) for devices with Au contacts evaporated directly after the evaporation of pentacene      |

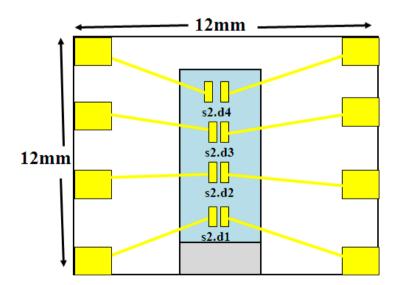

| 5.4  | The top view of the slide samples OTFT devices                                                                                                                                                            |

| 5.5  | Electrical characteristics of a fabricated OTFT. (a) The output characteristics and (b) transfer characteristics                                                                                          |

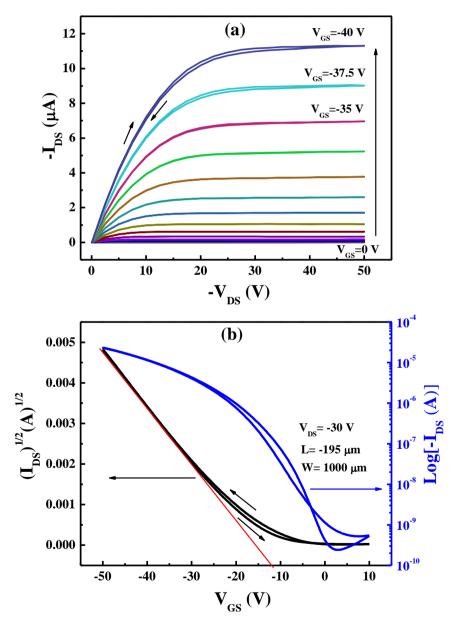

| 5.6 The output and transfer characteristics of OTFT measured (a) and (b) just after fabrication, (c) and (d) after two months of fabrication                                                                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

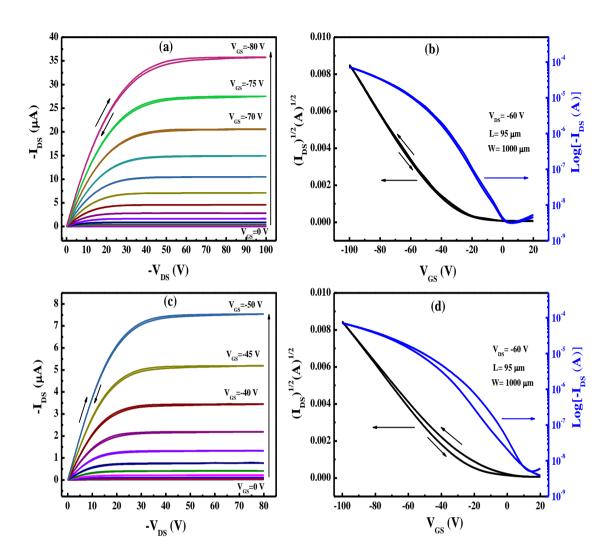

| 5.7 The output and transfer characteristics of an OTFT operated at high voltages136                                                                                                                                                                         |

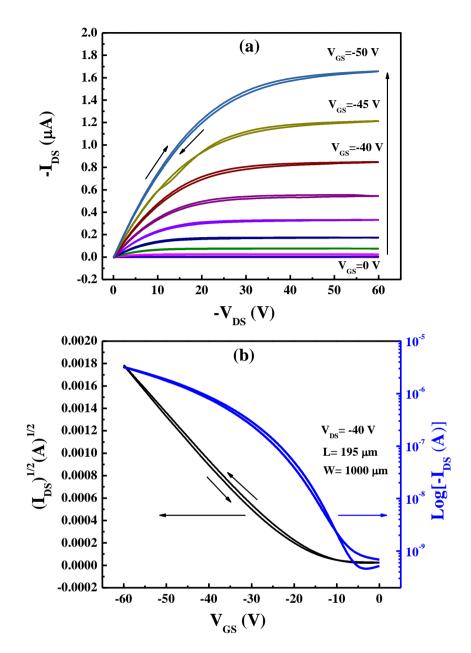

| 5.8 OFET characteristics measured after one year of fabrication. (a) The output characteristics and (b) transfer characteristics for device S1-d4                                                                                                           |

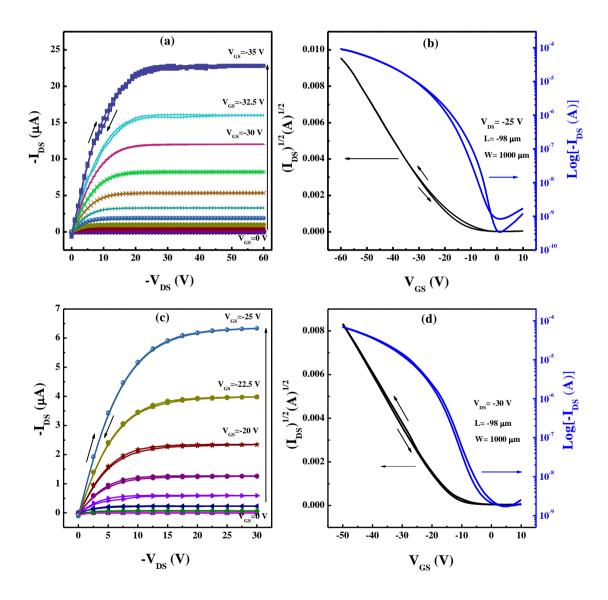

| 5.9 The output and transfer characteristics of OTFTs. (a) and (b) for device S1-d3 and (c) and (d) for device S2-d2                                                                                                                                         |

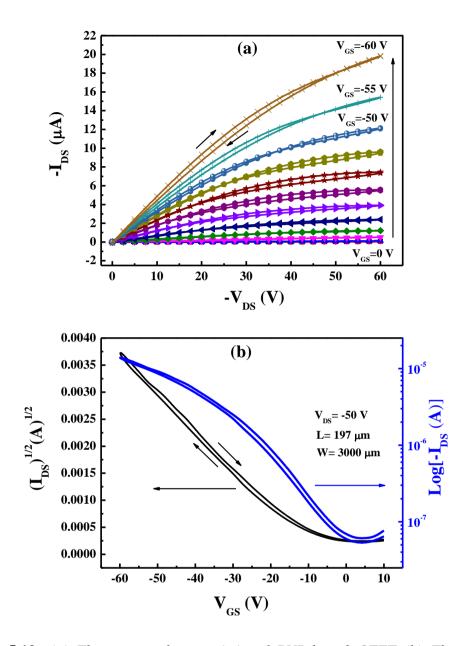

| 5.10 (a) The output characteristic of PVP-based OTFT (b) The transfer characteristics of the OTFT                                                                                                                                                           |

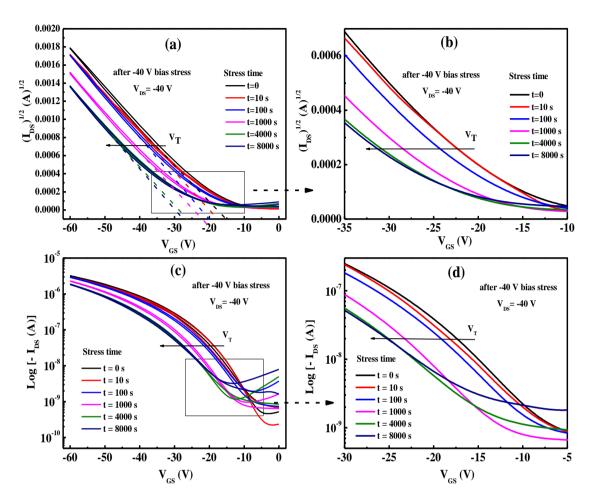

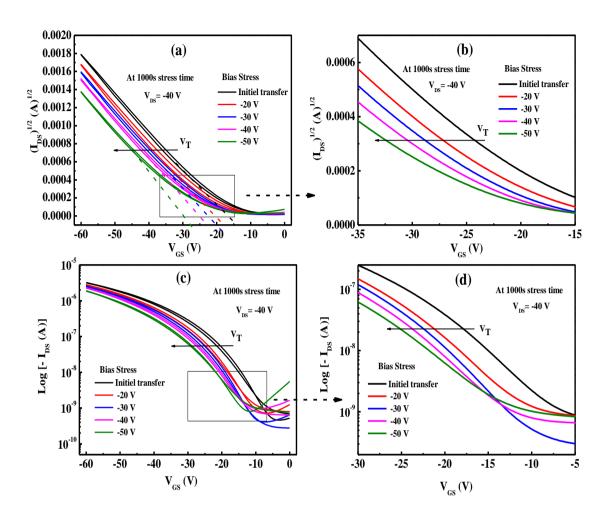

| 5.11 Transfer characteristics after bias stress at $V_{GS}$ = -40 V at different stress time (t). (a) and (b) for $(I_{DS})^{1/2}$ versus $V_{GS}$ , (c) and (d) for Log(- $I_{DS}$ ) versus $V_{GS}$ . (b) and (d) for the enlarged plots of the same data |

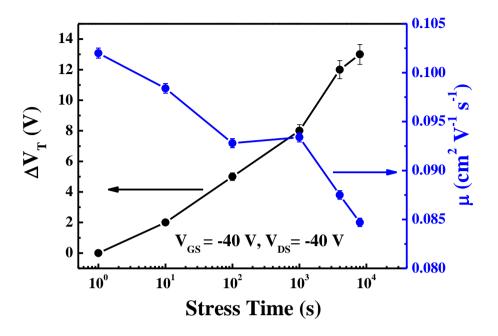

| 5.12 The threshold voltage shift $\Delta V_T$ and saturation field-effect mobility $\mu$ versus stress time at $V_{GS}$ = -40 V                                                                                                                             |

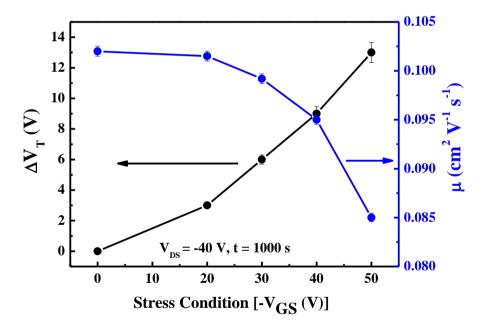

| 5.13 Transfer characteristics as a function of gate bias stress at stress time $t = 1000$ s. (b) and (d) represent enlarged plots of (a) and (c) respectively148                                                                                            |

| 5.14 Threshold voltage shift $\Delta V_T$ and saturation field-effect mobility $\mu$ versus gate bias stress at $t=1000~s$                                                                                                                                  |

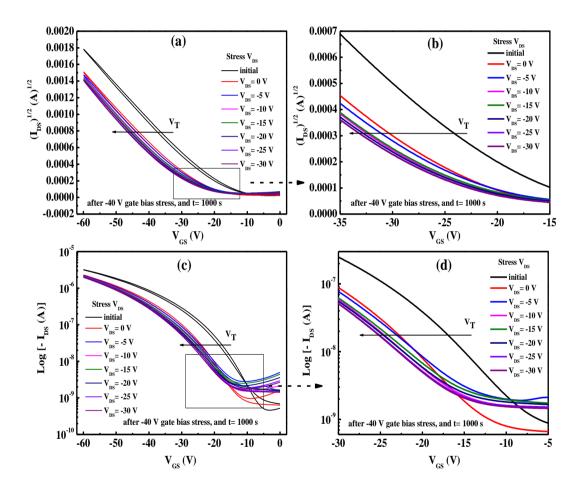

| 5.15 Transfer characteristics after varying stress drain-sours voltages at $V_{GS} = -40 \text{ V}$ and $t = 1000 \text{ s}$ . (b) and (d) represent the enlarged plots of (a) and (c)                                                                      |

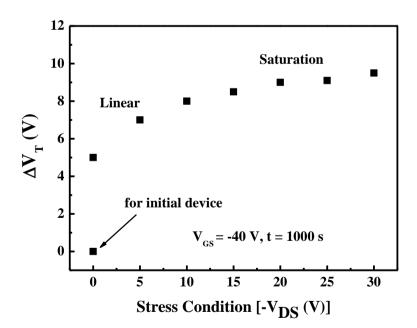

| 5.16 Threshold voltage shift $\Delta V_T$ versus drain-sours stress voltage at $V_{GS}$ = -40 V and t = 1000 s                                                                                                                                              |

| 6.1 Schematic diagrams of PMMA-based OTFMTs (a) with thin layer of gold (device A) and (b) gold nanoparticles (device B) as memory stack                                                                                                                    |

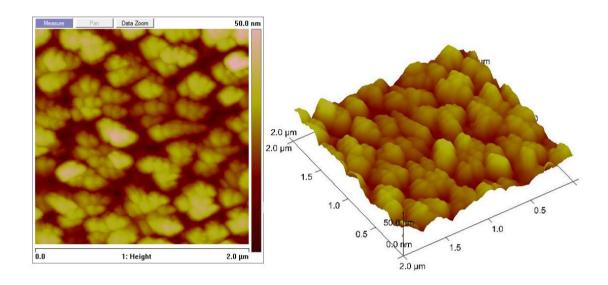

| 6.2 AFM images of the self-assembled AuNPs deposited on 300 nm PMMA161                                                                                                                                                                                      |

| 6.3 (a) Output characteristics and (b) transfer characteristics of the OTFT fabricated as the control device                                                                                                                                                |

| 6.4 (a) Output and (b) transfer characteristics of OTFMT of device A with and without the floating gate, thin layer of gold                                                                                                                                 |

| 6.5 (a) Output and (b) transfer characteristics of the OTFMT of device B with and without the floating gate, AuNPs                                                                                                                                          |

| 6.6 Output and transfer characteristics for another OTFMTs based on (a) and (b) thin film of gold (Device A) and (c) and (d) AuNPs (Device B) as floating gates166                                                                                          |

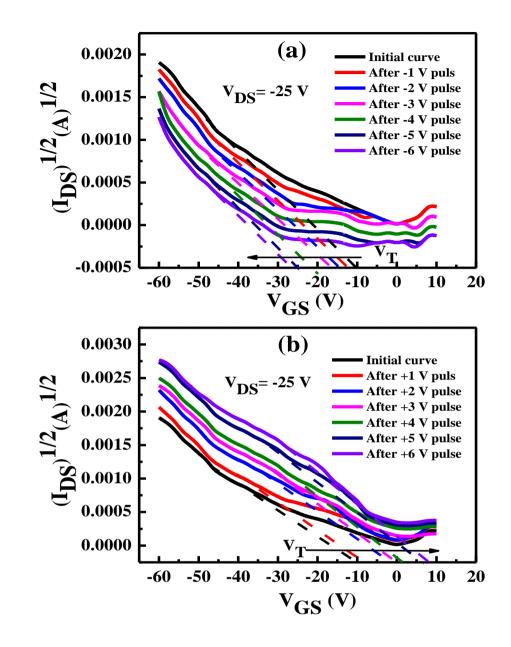

| 6.7 The effect of (a) negative and (b) positive pulses on transfer characteristics of Device A                                                                                                                                                              |

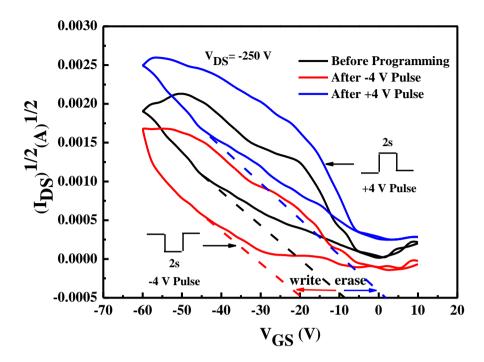

| 6.8 Transfer characteristics of the OTFMT of Device A after the application of positive and negative pulses of 3 V for 2 s                                                                                                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.9 The effect of (a) negative and (b) positive pulses on transfer characteristics of Device B                                                                                                                                                    |

| 6.10 Transfer characteristics of the OTFMT of Device B after the application of positive and negative pulses of 4 V for 2 s                                                                                                                       |

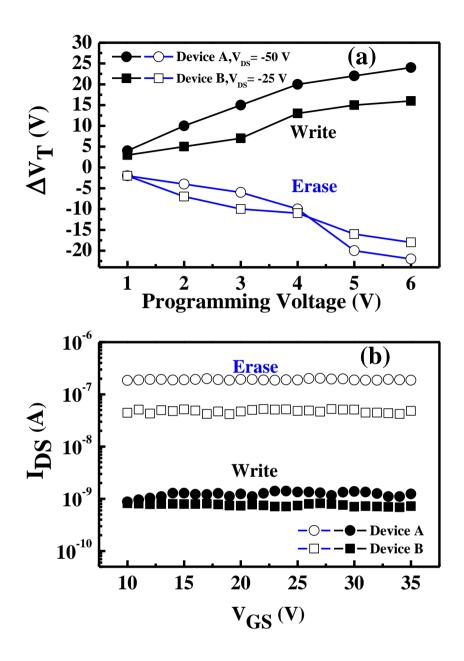

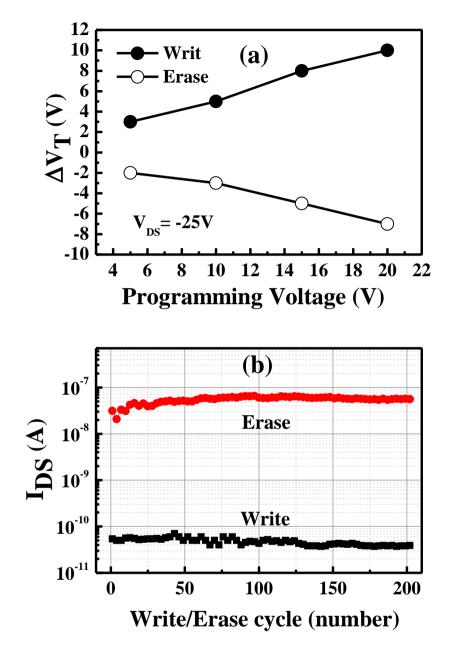

| 6.11 Programming characteristics of OTFMT. (a) The effect of the programming voltage (2 s pulses) on the threshold voltage shift, $\Delta V_T$ . (b) Write and erase processes by applying a negative and positive pulse voltage, respectively171 |

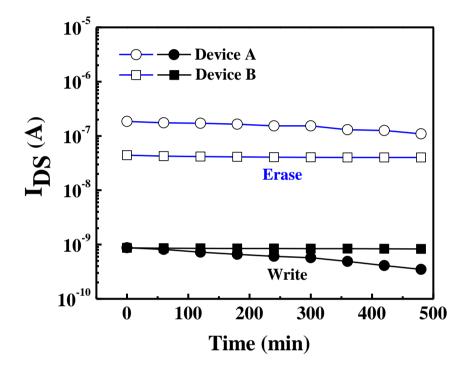

| 6.12 Charge retention characteristics of the OTFMTs Devices A and B172                                                                                                                                                                            |

| 6.13 Energy band diagram of the OTFMT in Figure 6.1174                                                                                                                                                                                            |

| 6.14 Transfer characteristics of OTFMT measured after 12 months of the fabrication                                                                                                                                                                |

| 6.15 (a) The output and (b) transfer characteristics of the OTFMT device with and without the SWCNTs floating gate                                                                                                                                |

| 6.16 The effect of (a) negative and (b) positive pulses on transfer characteristics for SWCNT-based OTFMT                                                                                                                                         |

| 6.17 Transfer characteristics of the SWCNT-based OTFMT after the application of positive and negative pulses of 15 V for 1 s                                                                                                                      |

| 6.18 (a) Programming characteristics, (b) pulses sequence and (c) retention current for the SWCNT-based OTFMT                                                                                                                                     |

| 6.19 (a) The output and (b) transfer characteristics of the PVP-based OTFT (control device) and OTFMT device                                                                                                                                      |

| 6.20 The effect of (a) negative and (b) positive pulses on transfer characteristics for PVP-based OTFMT                                                                                                                                           |

| 6.21 (a) Programming characteristics and (b) retention current for the PVP-based OTFMT                                                                                                                                                            |

## List of Tables

| 2.1 | Overview of inorganic dielectric materials                                                        | 4 |

|-----|---------------------------------------------------------------------------------------------------|---|

| 2.2 | Overview of the organic dielectric materials measured at 10 kHz2                                  | 5 |

| 3.1 | Cleaning process for glass substrates                                                             | 1 |

| 4.1 | The effect of pentacene evaporation rates and insulator thickness on pentacen surface morphology9 |   |

| 4.2 | The electrical parameters of the OMIS memory devices                                              | 0 |

| 5.1 | The electrical parameters for set of OTFTs measured directly after fabrication 13:                | 2 |

| 5.2 | The electrical parameters for the set of OTFTs measured after two months of fabrication           |   |

| 5.3 | The electrical parameters for a new set of OTFTs (second fabrication)13                           | 8 |

| 6.1 | Electrical parameters of devices A and B                                                          | 5 |

| 6.2 | The electrical parameters of the OTFMTs devices                                                   | 9 |

## Abstract

A systematic approach has been used to optimise the fabrication process of pentacenebased nonvolatile organic thin film memory transistors (OTFMTs) operating at low programming voltages. In the first part of this work, reliable, reproducible and hysteresis free organic metal-insulator-semiconductor (OMIS) devices and organic thin film transistors (OTFTs) were fabricated and characterised. All devices were based on poly(methyl methacrylate) (PMMA) and poly(vinyl phenol) (PVP) as the organic insulators. The second part of this work focused on optimising the evaporation parameters to fabricate high-performance pentacene-based devices. About 50 nm thickness of pentacene film with a deposition rate of 0.03  $nm \ s^{-1}$  on ~ 300 nm of PMMA was found to produce large, uniform and condense grains leading to high quality devices. OTFTs with high mobility of 1.32  $cm^2 V^{-1} s^{-1}$ , on/off current ratio of 10<sup>6</sup>, and negligible hysteresis and leakage current were demonstrated. The effect of the environment on the OTFTs obehaviour was also investigated. The bias stress effect was also investigated in terms of threshold voltage shift  $\Delta V_T$  at various conditions and times. The results show  $\Delta V_T$  increases with the increase of stress voltage. A negligible hysteresis is evident between the forward and reverse direction of the transfer characteristics and the shape of the transfer characteristics does not change with the bias stress.

Floating gate memory structures with thin layer of gold, gold nanoparticles (AuNPs) and single walled carbon nanotubes (SWCNTs) were fabricated and characterised during this investigation. Hysteresis in memory structures was a clear indication of the memory effect and charge storage in these devices. Also, the hysteresis was centred close to 0 V for SWCNTs-based structures, which indicate that a low operation voltage is needed to charge the devices. A memory window of about 40 V was observed for AuNPs-based memory devices based on PVP; while the memory windows for devices based on PMMA with thin layer of Au and AuNPs floating gates were 22 V and 32 V, respectively.

The electrical properties of the OTFMTs were improved by the use of the Au nanoparticles as the floating gate compared with that of an Au thin film. Using appropriate negative or positive voltages, the floating gate was charged and discharged, resulting in a clear shift in the threshold voltage of the memory transistors. Negative and positive pulses of 1 V resulted in clear write and erase states, respectively. Additionally, these organic memory transistors exhibited rather high carrier mobility of about  $\mu = 0.319 \ cm^2 \ V^1 \ s^{-1}$ . Furthermore the data retention and endurance measurements confirmed the non-volatile memory properties of the memory devices fabricated in this study.

| Dedicated to my parents and my husband, my daughter and son | n, |

|-------------------------------------------------------------|----|

| my brothers and sisters.                                    |    |

|                                                             |    |

|                                                             |    |

|                                                             |    |

|                                                             |    |

|                                                             |    |

|                                                             |    |

|                                                             |    |

|                                                             |    |

|                                                             |    |

|                                                             |    |

|                                                             |    |

|                                                             |    |

## Acknowledgements

All praises go to Allah for his blessing and reconcile me in completing this thesis. I would like to extend a special thanks to my supervisor, Dr. Mohammed Mabrook for his support and encouragement over the last few years. I would like to thank him for the rich information that he provided to me through this thesis.

Many thanks to Professor Martin Taylor and Dr. Paul Sayers for the help, and advice. I would also like to thank all members of Plastic Electronics Research group, thanks to Colin, Dan, Eifion, Adam and Thamra for their discussions and encouragement.

I would like to thank the School of Engineering at Durham University, particularly Dr. Dagou Zeze for preparation and deposition of SWCNTs that we used in our study.

I am also very much grateful to the Higher Education in Iraq for the provision of a studentship and to Iraqi cultural attaché in UK for help and support.

Last but not least, a big thanks to all my family, especially my mother, my husband (Ali), my children (Fatimah and Mohammed), my brothers and sisters. Thanks you for standing by my side, giving me the required strength to overcome all my obstacles and reach to my goals.

## **Chapter 1**

## Introduction

## 1.1 Introduction

During the last few years, the performance of electronic devices and circuits that based on organic compounds witnessed significant development. In addition to other properties characterise organic materials compared with inorganic materials such as low-temperature processing and low-cost manufacture, the ability to deposit these materials from solution provides the basis for applications requiring mechanical flexibility, and large-area coverage. Among the most important organic electronic devices that attracted a lot of attention from researchers are organic thin-film transistors (OTFTs) [1], organic memory devices [2], organic solar cells [3], and sensors [4]. Furthermore, in the field of organic light emitting diodes (OLEDs), the use of organic materials became of more interest in display panels' applications for different devices such as mobile phones and televisions.

One of the main advantages in organic materials is the possibility to change many of the electronic and chemical properties of polymers and small molecule materials by chemical modification. The morphology of thin films based on such materials can also be controlled using chemical modification. For example, the energy band gap in materials used in OLEDs can be adjusted to certain wavelengths of light [5].

Although in inorganic-based devices silicon is used significantly in early work as the base of the device structure beside the silicon dioxide (SiO<sub>2</sub>) as the insulator, some organic small molecules, such as pentacene, produced rather good organic transistors.

These kind of devices resulted in field effect mobilities of about 3  $cm^2/Vs$  [6], higher than recorded mobility for hydrogenated amorphous silicon (a-Si:H); about 1  $cm^2/Vs$  [7]. The conduction in these OTFTs based on p-type organic semiconductors was obtained in accumulation, where only holes have the ability to conduct. Philips researchers in 1995 have succeeded in integrating OTFTs into electronic circuits, bringing to light the ability of such devices to perform logic functions, by building ring oscillators and logic gates [8]. This step was then followed soon by logic gates and inverters based on p-type organic semiconductors [9, 10]. Similar success demonstrated in transistor devices based on n-type organic semiconductors based on Buckminsterfullerene ( $C_{60}$ ) as the active layer [11].

Designing of more complex circuits was successfully initiated by Crone et al. [12, 13]. As example for such devices are shift registers with 864 transistors [13] and decoders with operating voltages up to  $100 \ V$  [12]. Recently, Klauk et al. were able to fabricate inverters operate at low applied voltages of 1.5 to  $3 \ V$  [14]. These state of the art circuits based on NAND gates and ring oscillators with two different semiconductors; pentacene (p-channel device) and hexadecafluorocopperphthalocyanine ( $F_{16}$ CuPC, n-channel device) as the active layers as well as self-assembled monolayer (SAM) act as the gate dielectric.

It is important to mention the importance of bias stressing in OTFTs (which is studied in this thesis with different conditions), as it has critical effect on practical circuit applications. Bias-stressing is the shift of the current-voltage (*I*–*V*) characteristics with the application of continued voltages [15–17]. Structural disorder, at the semiconductor/dielectric interface or in the bulk of the semiconductor, as well as existed impurities act as traps leading to changes in threshold voltage [18]. In the "on state" of OTFTs devices, bias stress cause to some of the majority carriers becoming trapped in semiconductor/dielectric interface, so no longer contribute to the device conductivity. However, in the "off state" the bias stress results in minority carrier been trapped at the interface [19].

Recently, considerable interest has been focused on the development of new types of organic memory devices that can combine the properties of high speed, high density, and low power and cost with nonvolatility. Organic memory devices based on bistable switching [20], charge storage in MIS [21], and organic thin film memory transistors

(OTFMTs) [22–24] have been widely reported. The subject of memory devices is the main field of this thesis and will be reviewed in some details in Section 1.4 of this chapter.

## 1.2 Historical background

Historically, the beginning of organic electronics started with the identifying of organic semiconductors in the late 1940s [25]. Research on the electrical behaviour of organic materials were accumulated in the 1960s [26], while the discovery of photoconductive organic materials were in the 1970s, and late in that decade the conductive polymers were discovered [25]. The new impulse to the activity in the field of organic electronics was emerged after work in semiconductors and photoemission polymers established in the 1980s [27], for example, work on organic field-effect transistors (OFETs) [28], organic photovoltaic cells (OPVCs) [29], and organic light-emitting diodes (OLEDs) [30, 31]. The initial organic devices were based on either conjugated polymers such as polythiophene (PT) [28] and poly(p-phenylenevinylene) (PPV) [31] as the active layer in OFETs, or small organic molecules, such as, 8-hydroxyquinoline aluminium (Alq<sub>3</sub>) as the emitting layer in OLEDs [30].

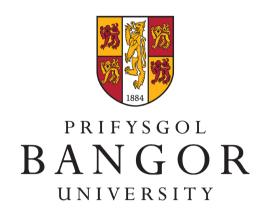

In the year 2000 the Nobel Prize in chemistry was awarded to Alan J. Heeger, Alan G. MacDiarmid, and Hideki Shirakawa for the development of highly-conductive organic polymers (iodine-doped polyacetylene), which is discovered in 1977 [32]. Since that date (2000s), the performance of organic electronic devices has continuously improved; the power conversion efficiencies of OPVCs have reached over 5 % [33], OLEDs have now been launched onto the display market, and the performance of organic thin-film transistors (OTFTs) now competes with amorphous silicon TFTs, as shown in Figure 1.1 [34].

**Figure 1.1:** Evolution of carrier mobility in organic field-effect transistor (OFET) [34].

## 1.3 Organic electronic applications

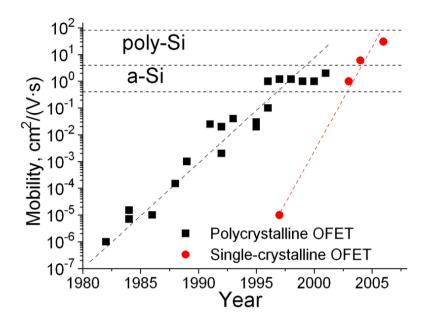

Organic electronics has attracted considerable applications owing to their process ability advantages; they can be used for existing applications requiring mechanical flexibility, large-area coverage, low cost, and low-temperature processing. Figure 1.2 shows a number of application fields that can benefit from the ingenuity of organic electronics technology.

The applications of organic electronics include broad range of products and technologies, for example: sensors, active-matrix (AM), flat panel displays (FPDs) based on liquid crystal pixels, low-end smart cards, organic light emitting diodes, electronic ink, electronic identification tags, and perhaps all-flexible electronics. In this section we will review some of these applications.

**Figure 1.2:** A typical applications of organic electronic technology.

Organic-based sensors used for environmental monitoring, home security, food safety and medical diagnostics have been intensely studied [35]. Organic sensors can be fabricated on flexible substrates with large-area coverage at room temperature using low-cost processes. Organic semiconductor materials have the possibility to lead to the manufacturing of sensors with selectivity and high sensitivity, where the important property for sensors is the ability to covalently attach biologically relevant moieties to organic semiconductor molecules [35].

In the field of flat panel displays, OTFTs are playing a key role in nowadays technology. In most applications the backplanes of AM OLED and AM liquid crystal displays (LCDs) are based on TFTs comprising low temperature poly silicon (LTPS) or hydrogenated amorphous silicon (a-Si:H) as the active layer. However, several advantages that OTFTs are possess such as: large-area coverage, low-cost manufacture and flexibility, make OTFTs a promising candidate for these backplanes. For example, it is impossible to make AM LCDs based on a-Si:H TFTs on a plastic substrate because of the high processing temperature needed for a-Si:H deposition.

In the year 2000, Philips Research [36] reported the first AM display based on organic semiconductors, while the electrophoretic flexible display using a backplane based on

OTFTs was shown in 2001 by Rogers et al. [37]. Hong et al. in 2005 [38] have reported high resolution for AM LCDs and the possibility to produce OTFT-based backplane with reasonably large size.

The performance of organic semiconductor technology has became sufficient to develop low-end smart cards and electronic identification tags applications that require low-cost circuits and modest speeds such as an integrated radio frequency identification (RFID) tag (operates at high-frequency, 13.56 MHz), intelligent electronic tickets, product packaging, card games and many other applications. Organic RFID tags can be produced with low cost and more flexible than those based on silicon by using solution processing and made of plastics. Pentacene based RFID circuits was demonstrated in 2003 by Baude et al. [39]. Following this in 2005, an organic RFID tag using novel pentacene and oligothiophene precursors was described by Subramanian et al [40]. Blache et al. reported the first working 4 bit transponder operating at a frequency of 13.56 MHz based on organic complementary metal-oxide-semiconductor (CMOS) in 2009 [41].

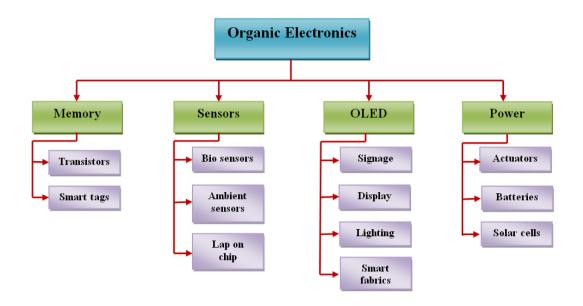

## 1.4 Memory devices

Memory device is a device that can preserve the information or data for later retrieval. Memory devices can be classified into two main types: volatile and non-volatile. Volatile memory devices lose the stored data as soon as the device is turned off and it need constant power to stay viable. There are mainly two types of volatile memory technology: Static Random Access Memory (SRAM) and Dynamic Random Access Memory (DRAM), the difference between them is the lifetime of the data they store. SRAM can keep the data reserved as long as the power is supplied but DRAM device can keep the data for a very short time, even when the power is turned on as DRAM is based on charge storage in a capacitor. DRAMs and SRAMs are extensively used in PCs mainly because DRAM's attributes of high density and low cost, and SRAM's attributes of high speed. On the other hand, non-volatile memory devices (NVMs) do not lose the data when the power supply is removed. NVM devices mainly consist of four types: flash memory, Ferroelectric Random Access Memory (FeRAM), Magnetic

Random Access Memory (MRAM) and phase change memory (PCM). The classification of memory devices technology is shown in Figure 1.3.

**Figure 1.3:** A classification of memory devices technologies.

Flash memory is the most suitable structure choice for non-volatile memory applications, since one cell consists of only one transistor. The data can be stored in a floating gate and defines the state of the memory by changing the threshold voltage of the transistor.

FeRAM is a non-volatile memory, in which a ferroelectric layer is used to store the data. Generally, there are two types of FeRAM technologies; ferroelectric field-effect transistor (FeFET) and capacitor-type. FeFET technology is a single element device uses a thin ferroelectric film as the gate dielectric in a FET [42]. Constructively, the second type, a capacitor-type, is similar to DRAM but to achieve a non-volatility property it uses a ferroelectric layer instead of the dielectric layer in DRAM for storing data.

The principle of the MRAM technology is based on storing the data as magnetic storage elements in micro-size cells not stored as current flows or electric charge. This technology needs a transistor and a magnetic tunnel junction [43], where it uses electron spin to store data (based on Spintronics).

PCM cell consists of a bipolar junction transistor and one resistor, the stored data in this non-volatile memory technology is based on the use of reversible phase change in materials. Depending on applying suitable heat pulses, the PCM materials can be switched quickly back and forth between crystalline and amorphous [44]. PCM was used in optical information technologies (CD-ROM, DVD and so on), and it is expected to be a promising non-volatile memory.

In the following section, we will limit the memory devices review to the non-volatile floating gate memory device which is related to this study.

## 1.4.1 Floating gate memory device

In widespread, the flash memory technology is built on floating gate concept. Memory operation can be achieved by charging nanoparticles, nanowires, or nanocrystals integrated into the insulating layer [21, 22]. A floating gate memory is a field-effect transistor or metal insulator semiconductor (MIS) structures with two gate electrodes, in addition to the control gate; it has a floating gate embedded in the gate dielectric.

MIS capacitors provide the foundation base for various types of electronic devices from thin-film transistors to charge-coupled devices and memory structures. The simplicity of MIS structure made it a strong tool widely used for the analysis of the interfaces and electrical properties of MIS-based system. This is similar to metal oxide semiconductor (MOS) capacitors used as analytical tools for the improvement and understanding of silicon based devices. Understanding the physics of MIS capacitors was basically used to improve the inorganic-based devices. Organic MIS structures are in fact characterised by their capacitance-voltage (C-V) characteristics which exhibit three distinct regions: accumulation, depletion and deep depletion (inversion in inorganic MOS). Memory devices based on MIS structures consist of charge traps added inside the insulator of the structure, the charge traps behave as the floating gate. The addition of the floating gate results in a clear shift in the C-V characteristics and hysteresis in the double-sweep C-V curve. The hysteresis may lead to the definition of two stable capacitance states which may be controlled and read by an external bias stimulus and thus exhibiting the expected memory behaviour.

As for organic thin film memory transistors (OTFMs) when a large enough program voltage is applied between the control gate and the source contact, electronic charge

can be brought onto the floating gate by quantum tunnelling or thermal emission [45]. Charging the floating gate changes the transistor's threshold voltage, as the charge on the floating gate partially screens the electric field between the control gate and the semiconductor. The threshold voltage shift can be detected by measuring the drain current at a certain gate—source voltage [28]. As the floating gate is completely isolated by the dielectric layer, charges stored on the floating gate remain there without the need for any applied voltage (non-volatile memory). To erase the memory, a voltage of opposite polarity should be applied to discharge the floating gate [45].

## 1.5 Outline of the Thesis

The main theme of this thesis is investigation of pentacene-based organic memory devices. During this work, four different structures of organic electronic devices are fabricated and characterised: OMIS capacitors, OMIS memory structure, OTFTs, and OTFMTs. Different materials have been used in this thesis such as poly(methyl methacrylate) (PMMA) and poly(vinyl phenol) (PVP) used as the gate dielectric, gold (Au) and Poly(3,4-ethylenedioxythiophene) poly(styrenesulfonate) (PEDOT:PSS), used as contacts, thin layer of gold, gold nanoparticles (AuNPs) and single walled carbon nanotubes (SWCNTs) were used as floating gates. The behaviour of floating gate memory devices is based on the presence of hysteresis in the *C-V* and *I-V* characteristics of OMIS and OTFMTs, respectively. Therefore, the first objective of this work was to provide high performance, hysteresis-free devices that can be used as the control structures. This is an important step to ensure that memory behaviour is actually due to the presence of floating gate rather than trapped charges in the semiconductor/insulator interface. In addition, obtaining non-volatile OTFMTs operating at low programming voltages with long retention time is also investigated.

In Chapter 1, a general introduction to organic electronics is reviewed. The historical background and various applications of organic electronics are briefly given. A brief background of the memory devices is reviewed.

Introductions to organic semiconductors and dielectric materials as well as charge transport mechanisms in organic semiconductors are reviewed in Chapter 2. This chapter also provides theoretical aspects relevant to the main theme of the thesis such as the electrical characterisation of MIS capacitors, TFTs and memory devices.

Chapter 3 provides information about the materials, experimental details and the techniques employed throughout this study.

Chapter 4 is the first results chapter, presents the fabrication and characterisation of OMIS capacitors and memory devices using different materials for gate electrode, gate dielectric and floating gates. This chapter also focused on the effect of surface morphology on device characteristics in order to establish optimal evaporation parameters for the evaporation of pentacene film.

In Chapter 5, the results are split into two parts, first part presents the result of pentacene-based OTFTs with two different types of organic gate dielectrics; PMMA and PVP. The influence of environment on device operation is also presented in this section. The second part focuse on the effect of bias stress on OTFTs with different conditions in order to measure the endurance properties of these devices.

The main objective of this study is presented in Chapter 6. This chapter presents the fabrication and characterisation of four types of pentacene based floating gate memory devices. Two different types of organic gate dielectrics are used; PMMA and PVP. Three different types of floating gates were incorporated: a thin film of gold, a layer of self-assembled metallic gold nanoparticles (AuNPs), and five layers of the Layer-by-Layer (LbL) single-walled carbon nanotubes (SWCNTs). Detailed programming and erasing procedures are also presented in this Chapter.

Finally, Chapter 7 provides the main conclusions derived from this work, together with possible further work.

## References

- [1] J. Zhou, Y. Hao, X. Yu, N. Zhou, and H. Lin, "High-performance and operationally stable organic thin-film transistors using bi-buffer layers with low-cost electrodes," *J. Phys. D: Appl. Phys*, vol. 46, pp. 382001–389501, 2013.

- [2] S. Nam, Y. Ko, S. G. Hahm, S. Park, J. Seo, H. Lee, H. Kim, M. Ree, and Y. Kim, "Organic nonvolatile memory transistors with self-doped polymer energy well structures," *NPG Asia Materials*, vol. 5, pp. 1–6, 2013.

- [3] J. R. O'Deaa, L. M. Browna, N. Hoepkera, J. A. Marohna, and S. Sadewassera, "Scanning probe microscopy of solar cells: From inorganic thin films to organic photovoltaics," *MRS Bulletin*, vol. 37, pp. 642–650, 2012.

- [4] H. Kong, T. J. Dawidczyk, R. Ozgun, A. G. Andreou, and H. E. Katz, "Printed Organic Electronic Sensors," Springer Series on Chemical Sensors and Biosensors, vol. 13, pp. 191–216, 2013.

- [5] V. Bulovic, R. Deshpande, M. E. Thompson, and S. R. Forrest, "Tuning the color emission of thin film molecular organic light emitting devices by the solid state solvation effect," *Chem. Phys. Lett.*, vol. 308, pp. 317–322, 1999.

- [6] H. Klauk, M. Halik, U. Zschieschang, G. Schmid, W. Radlik, and W.Weber, "High-mobility polymer gate dielectric pentacene thin film transistors," *J. Appl. Phys*, vol. 92, pp. 5259–5262, 2002.

- [7] E. A. Schiff, "Drift-mobility measurements and mobility edges in disordered silicons," *J. Phys.: Condens. Matter*, vol. 16, pp. S5265–S5275, 2004.

- [8] R. Brown, A. Pomp, C. M. Hart, and D. M. de Leeuw, "Logic gates made from polymer transistors and their use in ring oscillators," *Science*, vol. 270, pp. 972–974, 1995.

- [9] M. Matters, D. de Leeuw, M. Vissenberg, C. Hart, P. Herwig, T. Geuns, C. Mutsaers, and C. Drury, "Organic field-effect transistors and all-polymer integrated circuits," *Optical Materials*, vol. 12, pp. 189–197, 1999.

- [10] G. H. Gelinck, T. C. T. Geuns, and D. M. de Leeuw, "High-performance all-polymer integrated circuits," *Appl. Phys. Lett.*, vol. 77, pp. 1487–1491, 2000.

- [11] R. C. Haddon, A. S. Perel, R. C. Morris, T. T. M. Palstra, A. F. Hebard, and R. M. Fleming, "C<sub>60</sub> thin film transistors," *Appl. Phys. Lett.*, vol. 67, pp. 121–124, 1995.

- [12] Y. Lin, A. Dodabalapur, R. Sarpeshkar, Z. Bao, W. Li, K. Baldwin, V. R. Raju, and H. E. Katz, "Organic complementary ring oscillators," *Appl. Phys. Lett.*, vol. 74, p. 2714–2717, 1999.

- [13] B. Crone, A. Dodabalapur, Y. Lin, R. W. Filas, Z. Bao, A. LaDuca, R. Sarpeshkar, H. E. Katz, and W. Li, "Large-scale complementary integrated circuits based on organic transistors," *Nature*, vol. 403, pp. 521–523, 2000.

- [14] H. Klauk, U. Zschieschang, J. Pflaum, and M. Halik, "Ultralow-power organic complementary circuits," *Nature*, vol. 445, pp. 745–748, 2007.

- [15] S. J. Zilker, C. Detcheverry, E. Cantatore, and D. M. de Leeuw, "Bias stress in organic thin-film transistors and logic gates," *Appl. Phys. Lett.*, vol. 79, pp. 1124–1126, 2001.

- [16] D. Knipp, R. A. Street, A. Volkel, and J. Ho, "Pentacene thin film transistors on inorganic dielectrics: Morphology structural properties, and electronic transport," *J. Appl. Phys.*, vol. 93, pp. 347–355, 2003.

- [17] K. Suemori, S. Uemura, M. Yoshida, S. Hoshino, N. Takada, T. Kodzasa, and T. Kamata, "Influence of fine roughness of insulator surface on threshold voltage stability of organic field-effect transistors," *Appl. Phys. Lett.*, vol. 93, pp. 308–311, 2008.

- [18] H. -W. Zan and S. -C. Kao, "The effects of drain-bias on the threshold voltage instability in organ—ic TFTs," *IEEE Electron Device Lett.*, vol. 29, pp. 155–157, 2008.

- [19] H. Sirringhaus, "Reliability of organic Field-Effect transistors," *Adv. Mater.*, vol. 21, no. 38–39, pp. 3859–3873, 2009.

- [20] G. Liu, X. Zhuang, Y. Chen, B. Zhang, J. Zhu, C. Zhu, K. Neoh, and E. Tang Kang, "Bistable electrical switching and electronic memory effect in a solutionprocessable graphene oxide-donor polymer complex," *Appl. Phys. Lett.*, vol. 95, pp. 253301–253301-3, 2009.

- [21] M. F. Mabrook, Y. Yun, C. Pearson, D. A. Zeze, and M. C. Petty, "Charge storage in pentacene/polymethylmethacrylate memory devices," *IEEE Electron. Dev. Lett.*, vol. 30, pp. 632–634, 2009.

- [22] M. F. Mabrook, Y. Yun, C. Pearson, D. A. Zeze, and M. C. Petty, "A pentacene-based organic thin film memory transistor," *Appl. Phys. Lett.*, vol. 94, pp. 173302-1–173302-3, 2009.

- [23] C. A. Nguyen, S. G. Mhaisalkar, J. Ma, and P. S. Lee, "Enhanced organic ferroelectric field effect transistor characteristics with strained poly(vinylidene fluoridetrifluoroethylene) dielectric," *Org. Electron.*, vol. 9, pp. 1087–1092, 2008.

- [24] K. H. Lee, G. Lee, K. Lee, M. S. Oh, and S. Im, "The effect of moisture on the photon-enhanced negative bias thermal instability in Ga–In–Zn–O thin film transistors," *Appl. Phys. Lett.*, vol. 94, pp. 093304-1–093304-3, 2009.

- [25] H. Klauk (eds.), Organic Electronics. Weinheim: Wiley-VCH Verlag GmbH, 2006.

- [26] J. M. Shaw, and P. F. Seidler, "Organic electronics: introduction," *IBM J. Res. Dev.*, vol. 45, pp. 3–9, 2001.

- [27] G. Horowitz, "Organic field-effect transistors," *Adv. Mater.*, vol. 10, pp. 365–369, 1998.

- [28] Tsumura, K. Koezuka, and T. Ando, "Macromolecular electronic device: Field-effect transistor with a polythiophene thin film," *Appl. Phys. Lett.*, vol. 49, pp. 1210–1212, 1986.

- [29] W. Tang, "Two-layer organic photovoltaic cell," *Appl. Phys. Lett.*, vol. 48, pp. 183–185, 1986.

- [30] W. Tang, and S. A. van Slyke, "Organic electroluminescent diodes," *Appl. Phys. Lett.*, vol. 51, pp. 913–915, 1987.

- [31] J. H. Burroughes, D. D. C. Bradley, A. R. Brown, R. N. Marks, K. Mackay, R. H. Friend, P. L. Burns, and A. B. Holmes, "Light-emitting diodes based on conjugated polymers," *Nature*, vol. 347, pp. 539–541, 1990.

- [32] C. K. Chiang, C. R. Fincher, Y. W. Park, A. J. Heeger, H. Shirakawa, E. J. Louis, S. C. Gau, and A. G. MacDiarmid, "Electrical conductivity in doped polyacetylene," *Phys. Rev. Lett.*, vol. 39, pp. 1098–1100, 1977.

- [33] S. R. Forrest, "The Limits to Organic Photovoltaic Cell Efficiency," *MRS Bulletin*, vol. 30, pp. 28–32, 2011.

- [34] T. Hasegawa, and J. Takeya, "Organic field-effect transistors using single crystals," *Sci. Technol. Adv. Mater.*, vol. 10, pp. 024314-1–024314-16, 2009.

- [35] D. A. Bernards, R. M. Owens, G. G. Malliaras (eds.), Organic Semiconductors in Sensor Application, Springer. Heidelberg, 2008.

- [36] C. D. Sheraw, L. Zhou, J. R. Huang, D. J. Gundlach, T. N. Jackson, M. G. Kane, I. G. Hill, M. S. Hammond, J. Campi, B. K. Greening, J. Francl, and J. West, "Organic thin-film transistor-driven polymer-dispersed liquid crystal displays on flexible polymeric substrates," *Appl. Phys. Lett.*, vol. 80, pp. 1088–1090, 2002.

- [37] J. A. Rogers, Z. Bao, K. Baldwin, A. Dodabalapur, B. Crone, V. R. Raju, V. Kuck, H. Katz, K. Amundson, J. Ewing, and P. Drzaic, "Paper-like electronic displays: Large-area rubber-stamped plastic sheets of electronics and microencapsulated electrophoretic inks," *Proc. Natl. Acad. Sci. USA*, vol. 98, pp. 4835–4840, 2001.

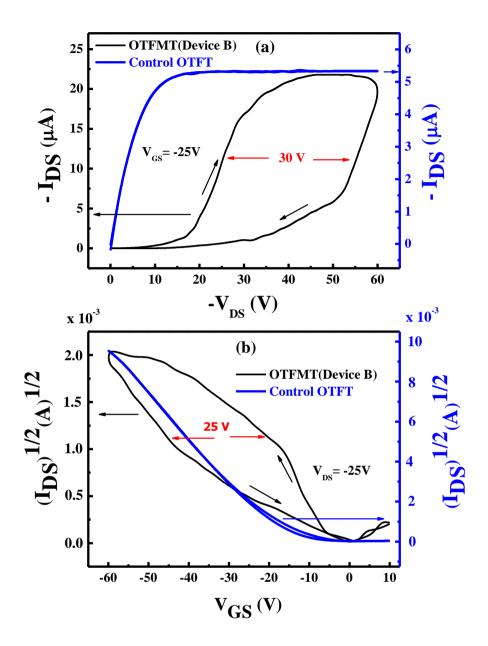

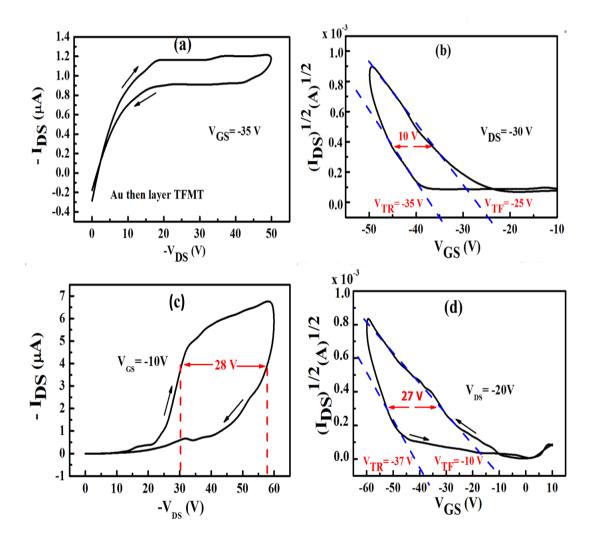

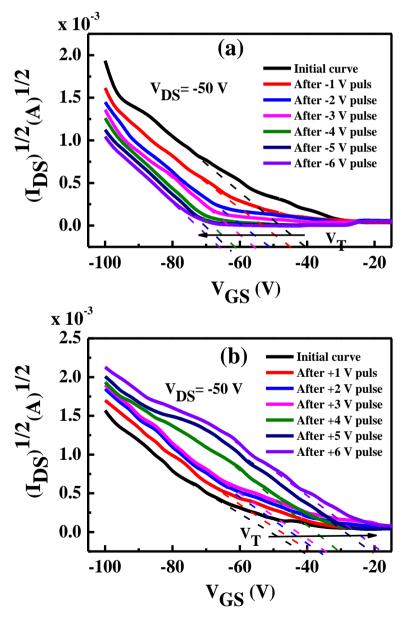

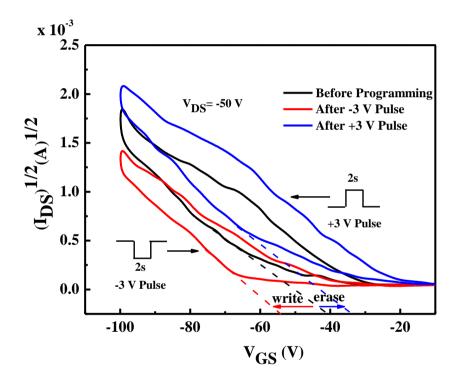

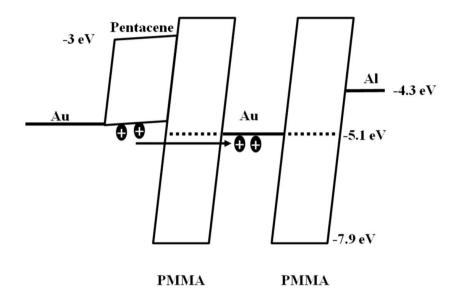

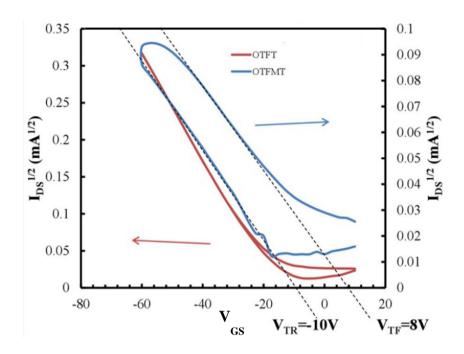

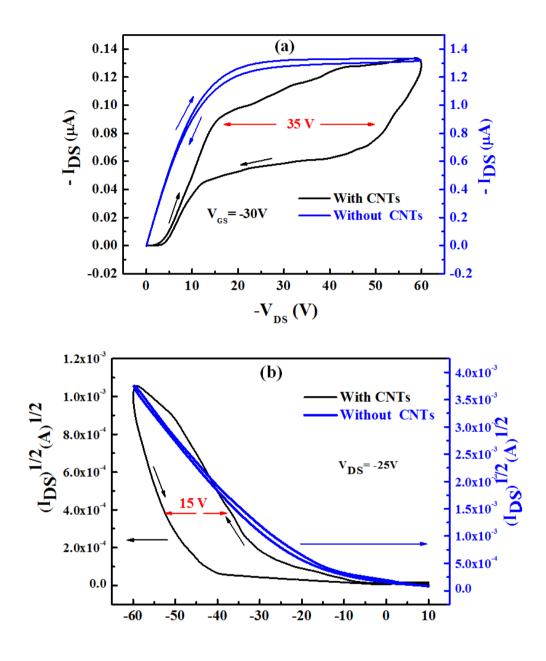

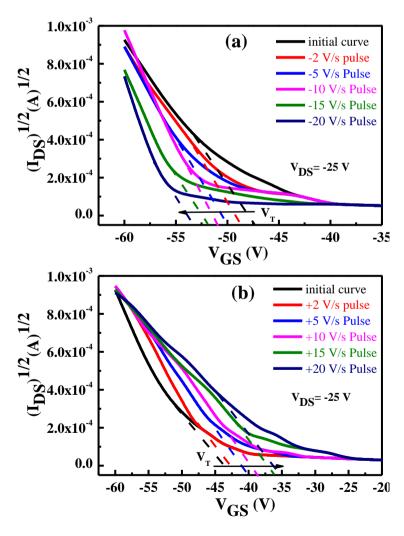

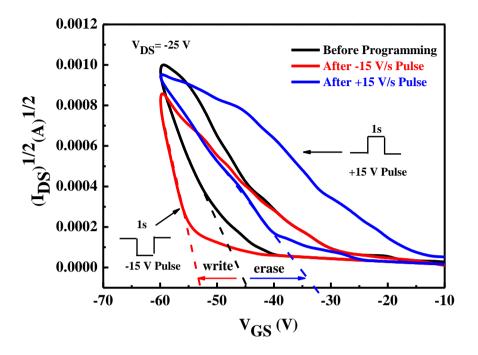

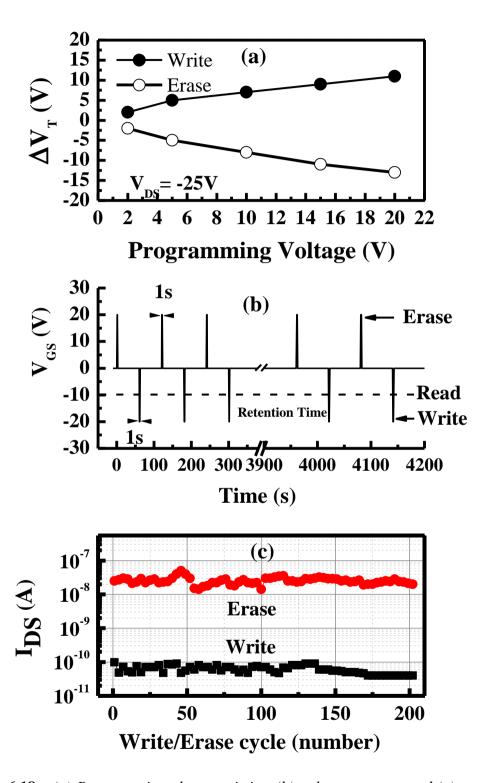

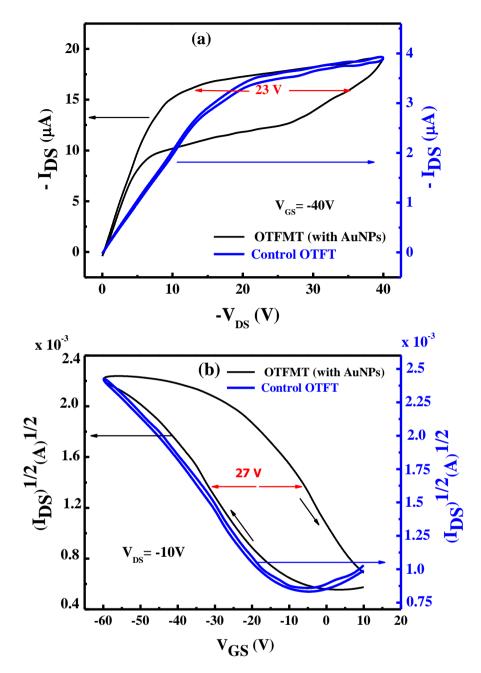

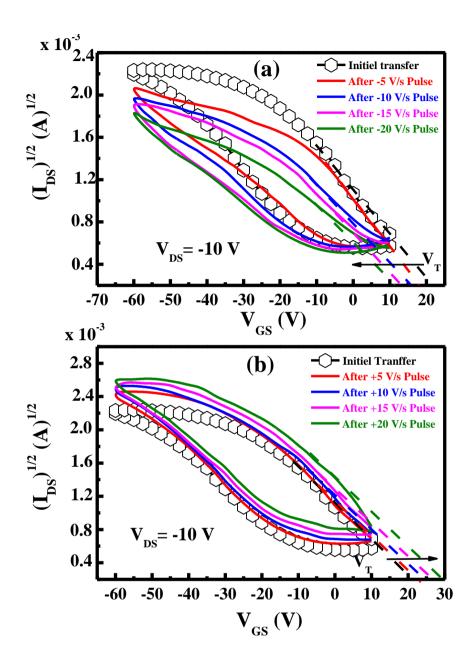

- [38] M. P. Hong, B. S. Kim, Y. U. Lee, K. K. Song, J. H. Oh, J. H. Kim, T. Y. Choi, M. S. Ryu, K. Chung, S. Y. Lee, B. W. Koo, J. H. Shin, E. J. Jeong and L. S. Pu, "Recent progress in large sized & high performance organic TFT array," Soc. Inf. Display Symp. Dig., vol. 36, pp. 23–26, 2005.