**Bangor University**

DOCTOR OF PHILOSOPHY

Electrical, Environmental and Optical Stress Effects on PS-DNTT OTFTs

Za'aba, Nor

Award date: 2018

Awarding institution: Bangor University

Link to publication

General rights Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal ?

Take down policy If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

**Bangor University**

# Electrical, Environmental and Optical Stress Effects on PS-DNTT OTFTs

by

## Nor Khairiah Za'aba

A thesis submitted for the degree of Doctor of Philosophy College of Physical and Applied Sciences School of Electronics Engineering

## TABLE OF CONTENTS

| Dec | laratio | n of Authorship                                                      | i  |

|-----|---------|----------------------------------------------------------------------|----|

|     |         | ontents                                                              |    |

|     | -       | ures                                                                 |    |

|     |         | oles<br>Conference Presentations                                     |    |

| -   |         | Igements                                                             |    |

| 1   |         | roduction                                                            |    |

|     | 1.1     | Introduction                                                         | 1  |

|     | 1.2     | Thesis Outline                                                       | 2  |

| 2   | Ba      | ckground Theory and Literature Review                                | 4  |

|     | 2.1     | Introduction                                                         | 4  |

|     | 2.2     | Basic Properties of Organic Semiconductor                            | 4  |

|     | 2.3     | Organic Semiconductors                                               | 6  |

|     | 2.4     | Charge Transport in Organic Semiconductor                            | 6  |

|     | 2.4     | .1 Multiple Trapping and Release Transport (MTR)                     | 7  |

|     | 2.4     | .2 Hopping Transport                                                 | 7  |

|     | 2.5     | Trap Density of States (DoS) in Organic Semiconductor                | 8  |

|     | 2.6     | OTFT Operation and Characteristics                                   | 9  |

|     | 2.6     | .1 OTFT Device Architecture                                          | 9  |

|     | 2.6     | .2 OTFT Operation Principle                                          | 10 |

|     | 2.6     | .3 OTFT Characteristics and Parameter Extraction                     | 13 |

|     | 2.6     | .4 Extraction of the Density of Trap State Using the Grünewald Model | 16 |

|     | 2.7     | Environmental and Electrical Stability in OTFT                       | 18 |

|     | 1.2     | .1 Effect of RH and Temperature                                      | 18 |

|     | 2.7     | .1 Effect of Bias Stress                                             | 19 |

|     | 2.7     | .2 Effect of Illumination                                            | 21 |

|     | 2.8     | Summary                                                              | 22 |

| 3   | Ex      | perimental Details                                                   | 24 |

|     | 3.1     | Introduction                                                         | 24 |

|     | 3.2     | Materials                                                            | 24 |

|     | 3.2     | .1 Preparation of the PS Solution                                    | 24 |

|     | 3.2     | .2 Substrate Cleaning Procedure                                      | 25 |

|     | 3.3     | Device Fabrication                                                   | 25 |

|   | 3.4       | Transistor Characterization                                             | 27        |

|---|-----------|-------------------------------------------------------------------------|-----------|

|   | 3.5       | Bias Stress Characterization                                            |           |

|   | 3.6       | Phototransistor Measurement                                             |           |

|   | 3.7       | Summary                                                                 |           |

| 4 | Env<br>33 | vironmental Stability in PS-DNTT Thin Films Transistors: The DoS Inve   | stigation |

|   | 4.1       | Introduction                                                            |           |

|   | 4.2       | Humidity Effect on Electrical Performance                               |           |

|   | 4.3       | Temperature Effect on Electrical Performance                            |           |

|   | 4.4       | Environmental Effects on Density of States (DoS)                        |           |

|   | 4.5       | Summary                                                                 | 42        |

| 5 | Eff       | Fect of Bias Stress on PS-DNTT Thin Film Transistor Stability           | 43        |

|   | 5.1       | Introduction                                                            |           |

|   | 5.2       | Negative bias stress instability in PS-DNTT TFTs                        | 43        |

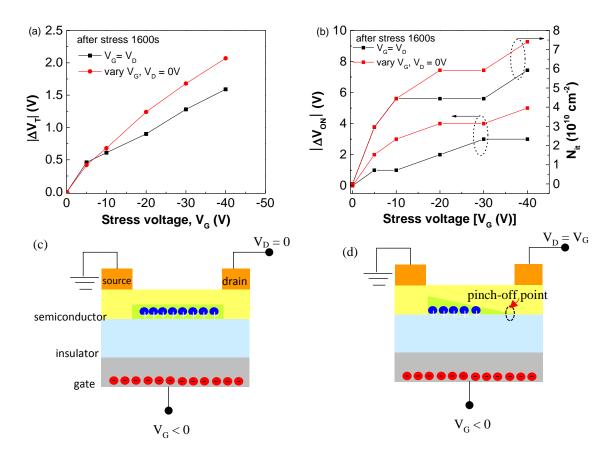

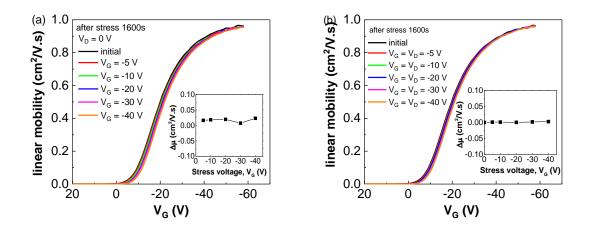

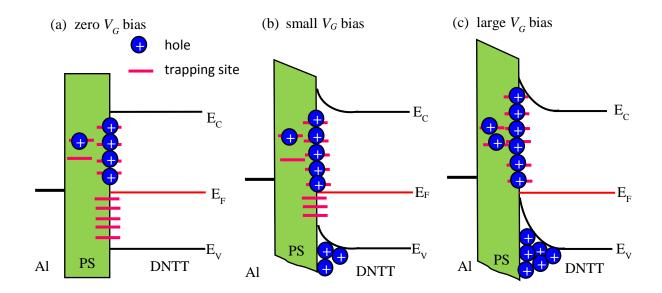

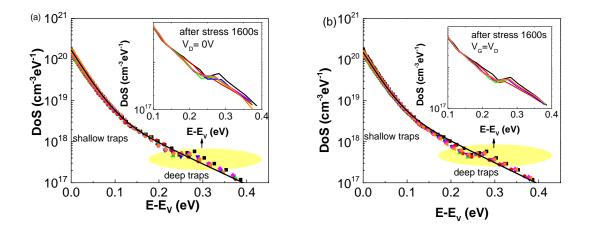

|   | 5.2       | C.1 Gate Bias Stress                                                    | 43        |

|   | 5.2       | 2.2 Recovery                                                            | 49        |

|   | 5.2       | 2.3 Effect of Stress Time                                               | 51        |

|   | 5.2       | 2.4 Effect of Long Term Stress                                          | 67        |

|   | 5.2       | 1.5 Influence of the Relative Humidity on Negative Bias-Stress Instabil | lity68    |

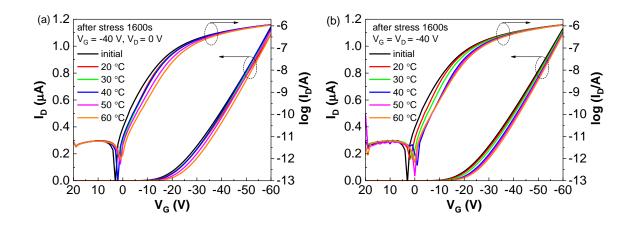

|   | 5.2       | Effect of Temperature on Bias Stress Induced Instability                | 72        |

|   | 5.3       | Positive Bias Stress Instability in PS-DNTT                             | 79        |

|   | 5.4       | Summary                                                                 | 81        |

| 6 | Pho       | oto-induced Effects in PS-DNTT Thin Films Transistors                   | 83        |

|   | 6.1       | Introduction                                                            | 83        |

|   | 6.2       | Results                                                                 |           |

|   | 6.2       | Effect of Monochromatic Wavelength                                      | 83        |

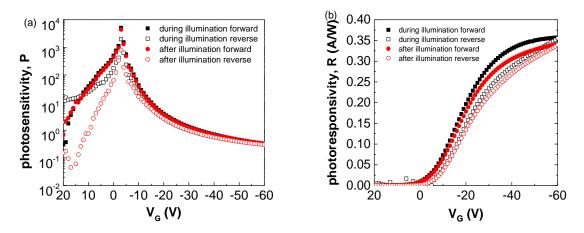

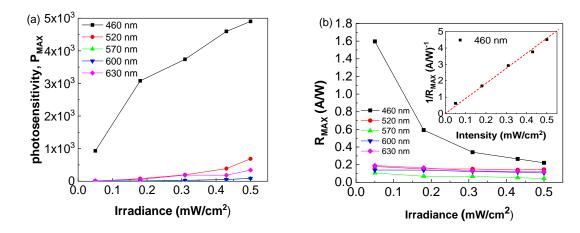

|   | e         | 6.2.1.1 Photosensitivity and photoresponsivity                          |           |

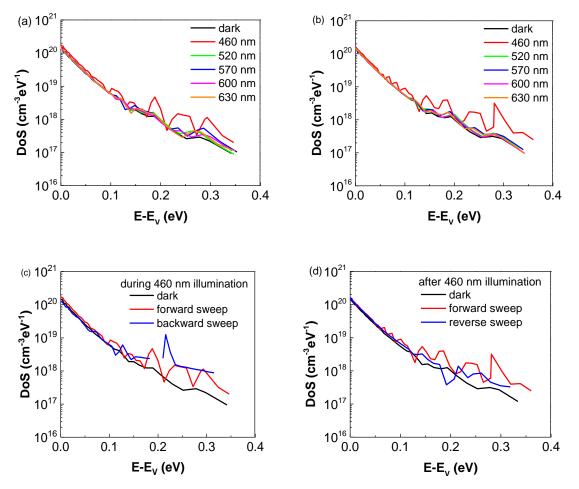

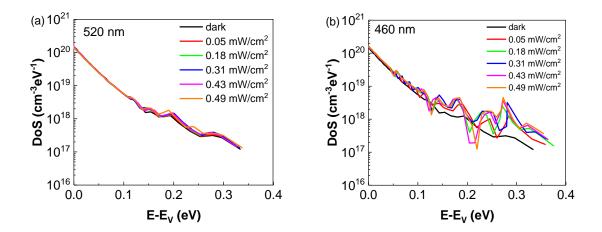

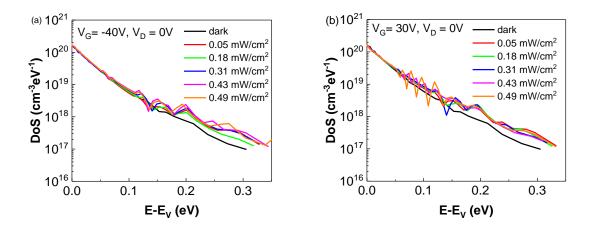

|   | e         | 6.2.1.2 Density of States                                               |           |

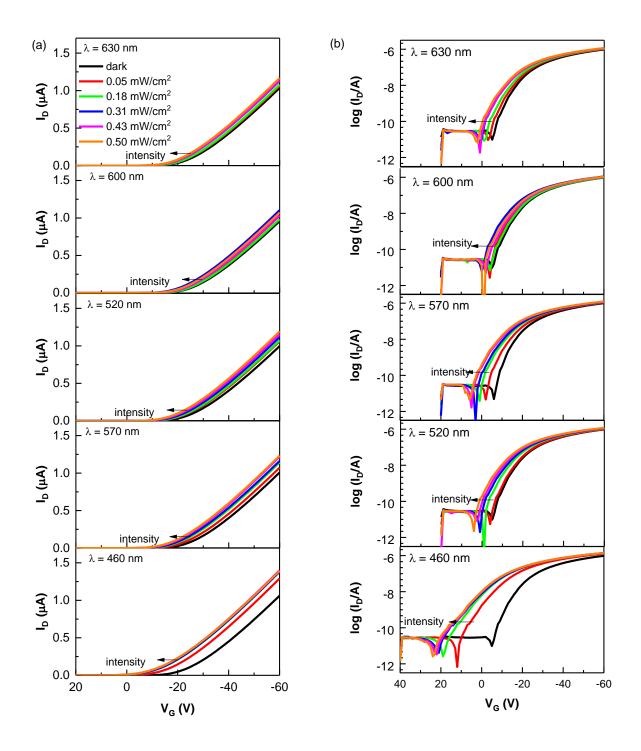

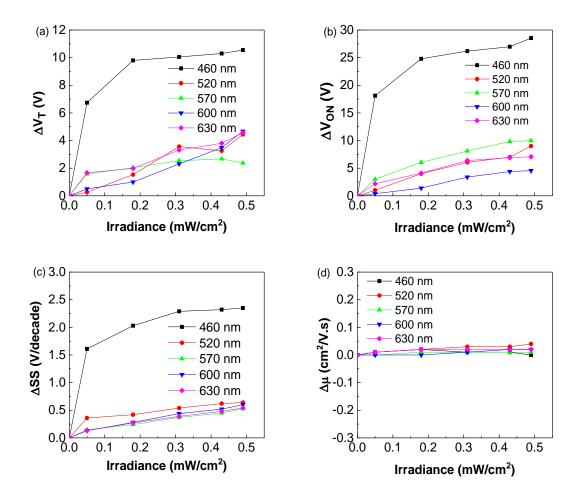

|   | 6.2       | 2.2 Effect of Monochromatic Light Intensity                             | 91        |

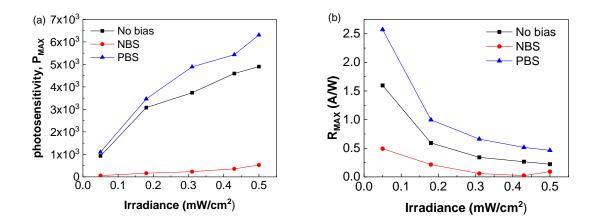

|   | 6         | 6.2.2.1 Photosensitivity and photoresponsivity                          |           |

|   | e         | 6.2.2.2 Density of States                                               | 94        |

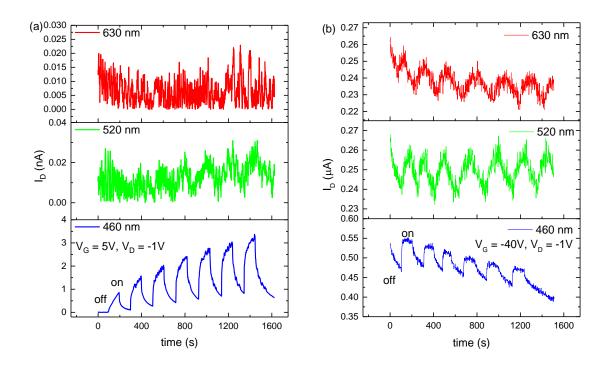

|   | 6.2       | 2.3 Dynamic Photoresponse to Light Pulses                               |           |

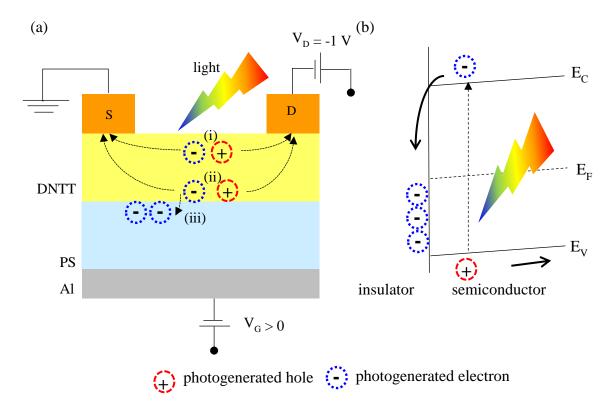

|   | 6.3       | Discussion                                                              | 96        |

|   | 6.4       | Summary                                                                 |           |

| 7 | Eff       | fect of Illumination and Bias Stress PS-DNTT Thin Films Transistors     |           |

| 7.1 Introduction104                                                     |

|-------------------------------------------------------------------------|

| 7.2 Results                                                             |

| 7.2.1 Effect of Bias Stress Under Ambient Light104                      |

| 7.2.2 Gate Bias Stress in the Presence of Monochromatic Illumination107 |

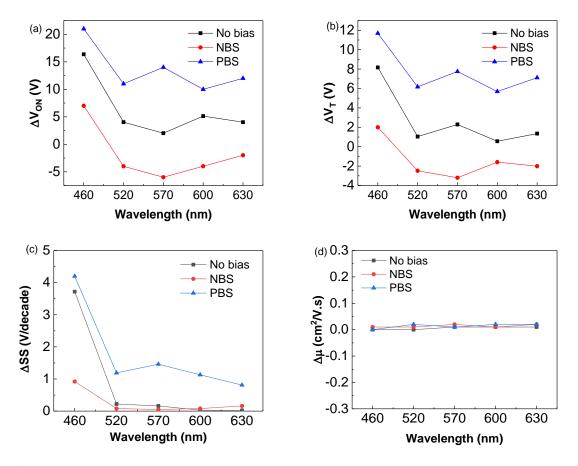

| 7.2.2.1 Effect of Wavelength107                                         |

| 7.2.2.2 Effect of stress time                                           |

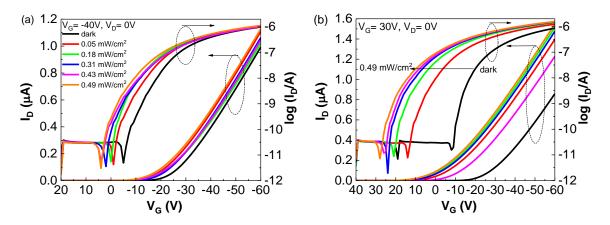

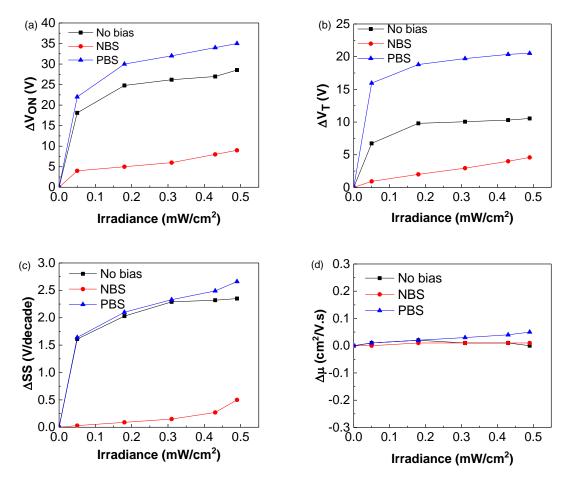

| 7.2.2.3 Effect of intensity116                                          |

| 7.3 Discussion119                                                       |

| 7.4 Summary120                                                          |

| 8 Conclusion121                                                         |

| 8.1 Conclusion121                                                       |

| 8.2 Future work                                                         |

| Appendix A                                                              |

| Appendix B                                                              |

| Appendix C                                                              |

| References                                                              |

#### LIST OF FIGURES

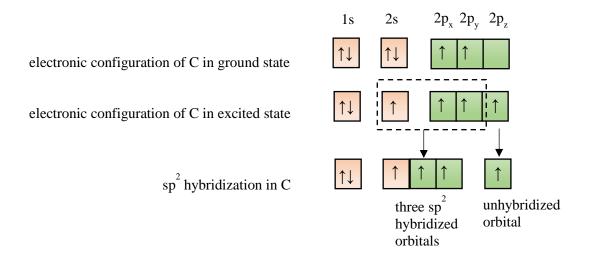

| <b>Figure 2.1</b> Electronic configuration of a carbon atom in the ground and excited states and after hybridisation                                                                                                                                                                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

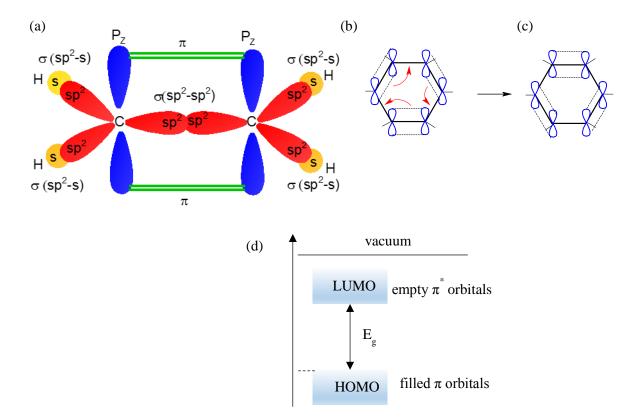

| <b>Figure 2.2</b> (a) Hybridisation of the ethylene molecule structure, (b) electron delocalization in benzene to form the structures seen in (c), and (d) schematic of energy level splitting between HOMO and LUMO                                                                          |

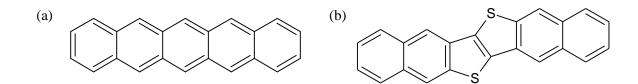

| Figure 2.3 Molecular structures of (a) pentacene and (b) DNTT                                                                                                                                                                                                                                 |

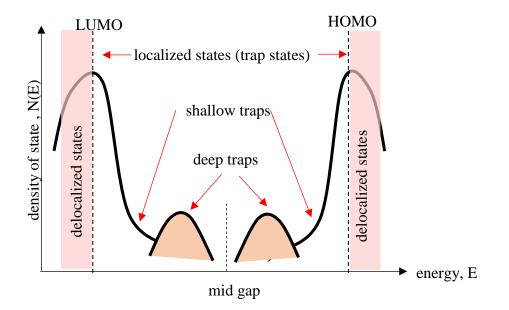

| <b>Figure 2.4</b> Schematic of density of states in an organic semiconductor adapted from [27]8                                                                                                                                                                                               |

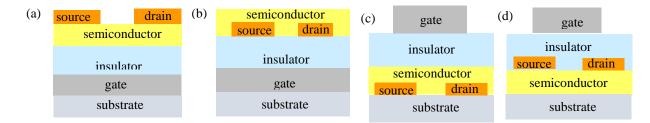

| <b>Figure 2.5</b> Cross-sections of simplified OTFT device configurations: (a) top-contact-bottom-<br>gate (staggered), (b) bottom-contact-bottom-gate (coplanar), (c) top-gate-bottom-contact<br>(staggered) and (d) top-gate-top-contact (coplanar)                                         |

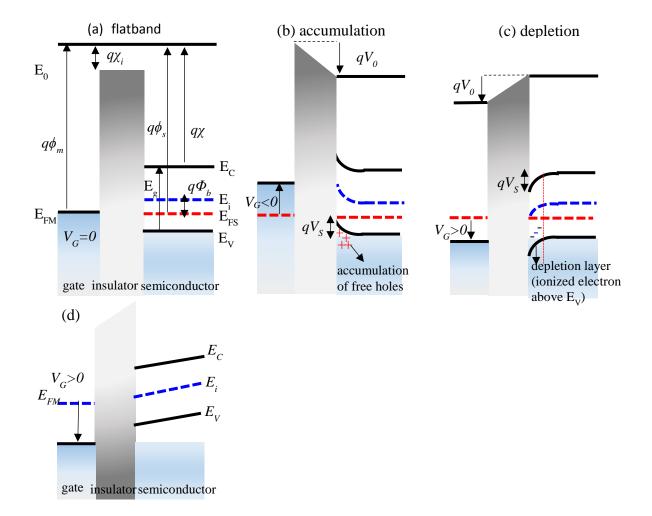

| <b>Figure 2.6</b> Band diagram of and ideal metal-insulator-semiconductor (p-type) structure showing (a) flatband conditions, $V_G = 0$ V (b) accumulation, negative $V_G$ and (c) depletion positive gate $V_G$ . Band diagram of intrinsic semiconductor with (d) positive gate voltage. 11 |

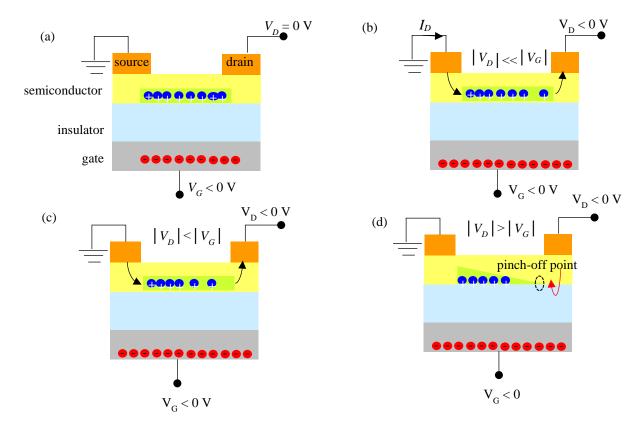

| <b>Figure 2.7</b> Operating stages of an OTFT, (a) $-V_G$ , $V_D = 0V$ , (b) $-V_G$ , $-V_D$ (slow), (c) $-V_G$ , $-V_D$ (medium) and (d) $-V_G$ , $-V_D$ (high)                                                                                                                              |

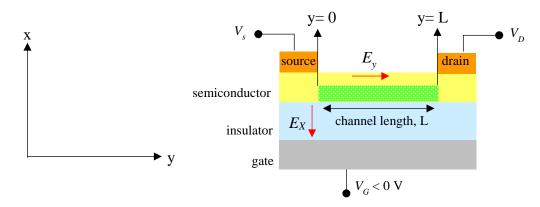

| <b>Figure 2.8</b> Cross-sectional view of the channel region of TFT used to derive the gradual channel approximation with x direction is perpendicular to the channel and y is parallel to the channel                                                                                        |

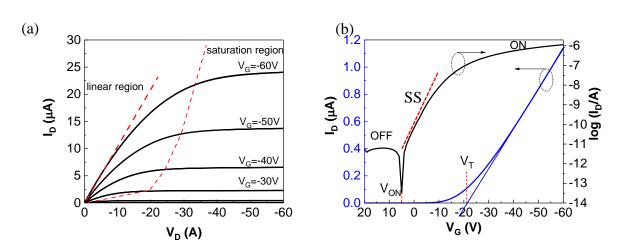

| <b>Figure 2.9</b> (a) Output characteristics and (b) The transfer characteristic of a PS-DNTT TFT measured in the dark at a drain voltage, $V_D = -1$ V plotted in linear and semilog scale16                                                                                                 |

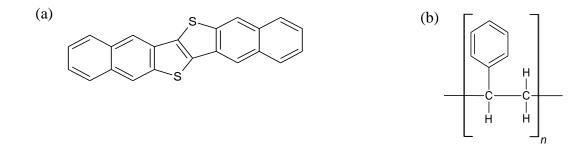

| Figure 3.1 Molecular structures of (a) DNTT and (b) PS24                                                                                                                                                                                                                                      |

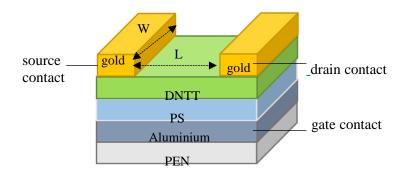

| <b>Figure 3.2</b> Structure of bottom-gate top-contact of PS-DNTT OTFT fabricated on PEN substrate where <i>L</i> and <i>W</i> are the channel length and width respectively                                                                                                                  |

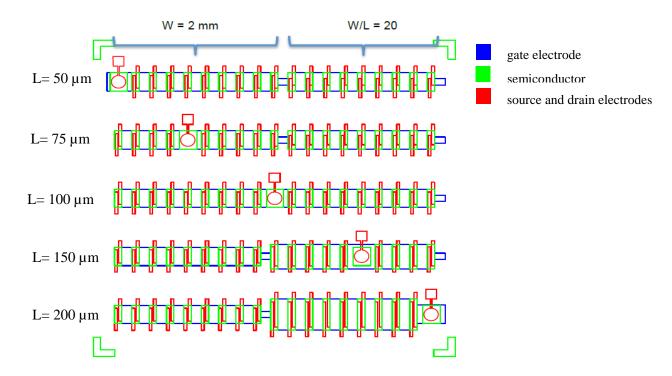

| <b>Figure 3.3</b> Mask features 18 x5 arrays of 90 transistors with 5 circular capacitors of 2mm diameter arranged diagonally across the substrate. Source and drain contacts are depicted in red, gate contacts in blue and semiconductor in green (adapted from [100])26                    |

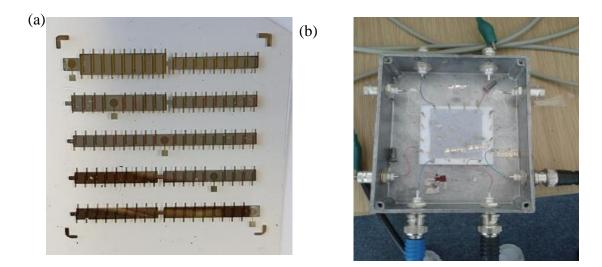

Figure 3.4 Photograph of the (a) actual PS-DNTT OTFTs and (b) aluminium test box. ....27

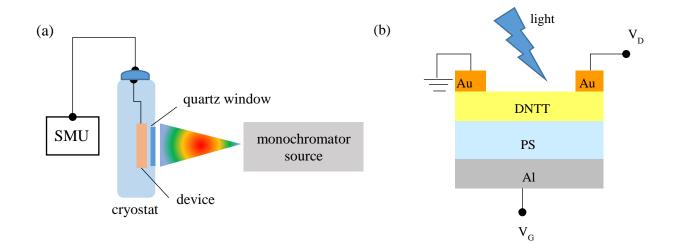

**Figure 3.7** (a) Schematic diagram of the phototransistor measurement setup and (b) crosssection of a PS-DNTT device structure under illumination through the top of the DNTT film.

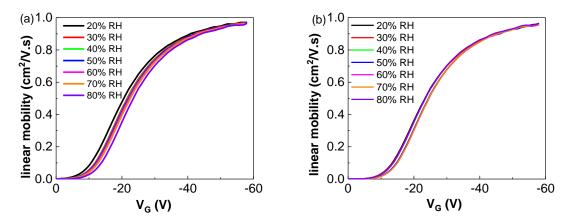

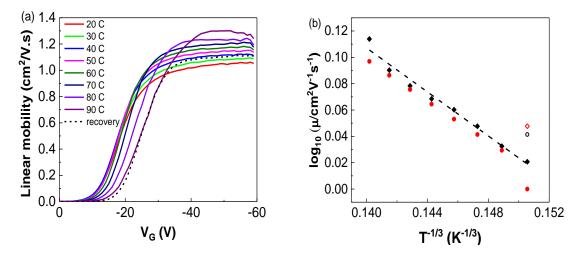

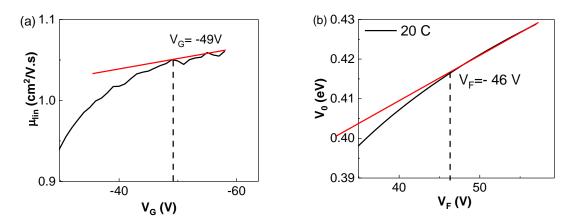

**Figure 4.3** Gate-voltage-dependent mobility extracted by applying equation (2.11) to transfer characteristics obtained in the linear regime with (a) increasing RH and (b) decreasing RH.

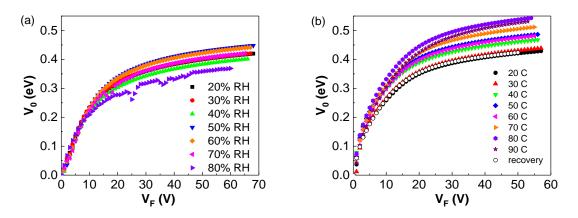

| Figure 4.6 Plots of $V_0$ versus $V_F$ showing the effect of (a) relative humidity and (b) | ) |

|--------------------------------------------------------------------------------------------|---|

| emperature                                                                                 | ) |

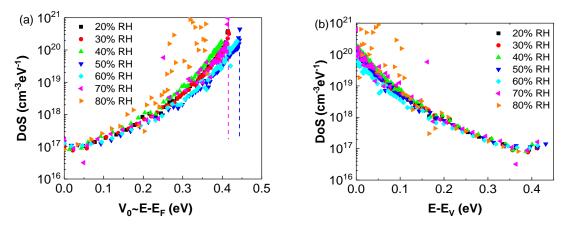

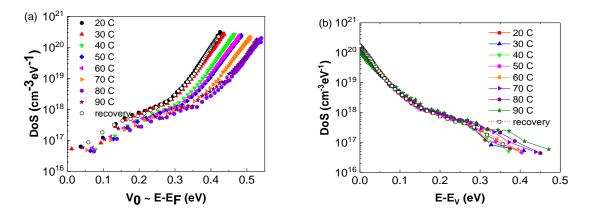

| Figure 4.7 Density of states for different values of RH plotted relative to (a) $V_0$ (= <i>E</i> - <i>E</i> <sub><i>F</i></sub> ) and | l |

|----------------------------------------------------------------------------------------------------------------------------------------|---|

| (b) the mobility edge assumed to coincide with $\sim E_V$                                                                              | ) |

**Figure 4.8** Density of states for different values of temperature plotted relative to (a)  $V_0$  (=*E*- $E_F$ ) and (b) the mobility edge assumed to coincide with  $E_V$ ......40

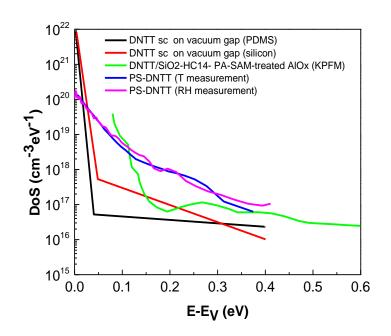

**Figure 4.9** Comparison of DoS spectra obtained in the present work using the Grünewald et al model with those obtained by applying the Oberhoff et al model to single-crystal DNTT [104] and from evaporated films using Scanning Kelvin Probe Microscopy [105]......41

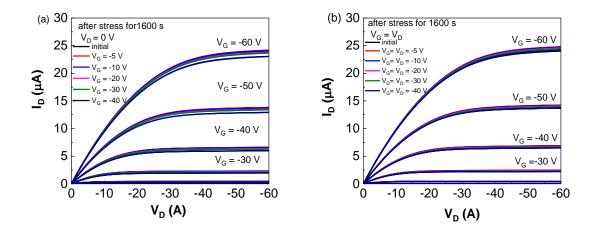

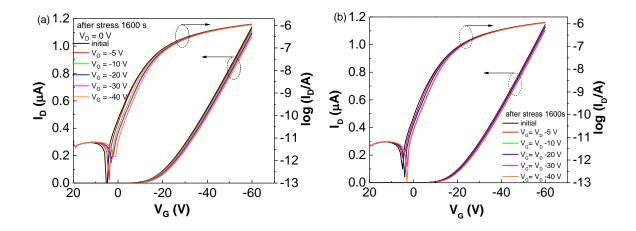

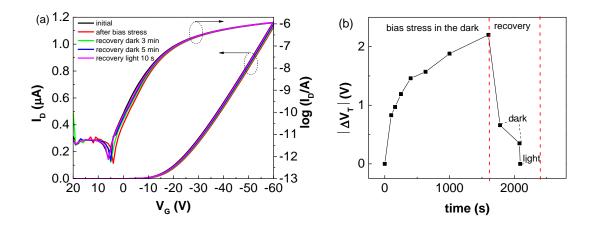

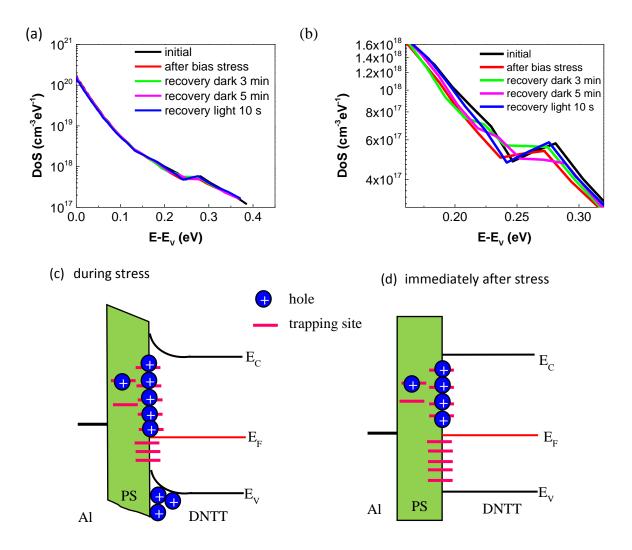

**Figure 5.8** (a) The DoS distribution as a function of as a function of E- $E_V$  after stress and during recovery time. (b) An expended view of changes in the deep states. Proposed

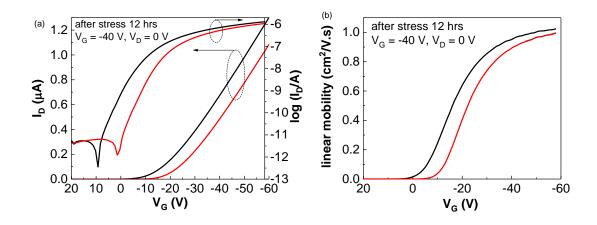

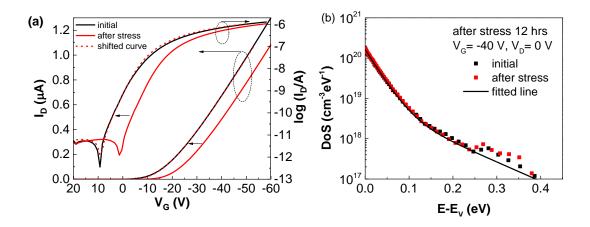

**Figure 5.19** (a) Transfer characteristics in forward sweep obtained at  $V_D = -1$  V and (b) Gate-voltage-dependent mobility after 12 hrs stress at  $V_G = -40$  V and  $V_D = 0$  V......67

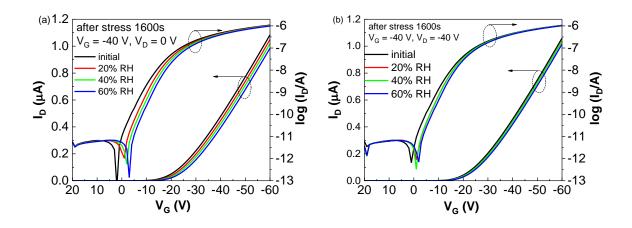

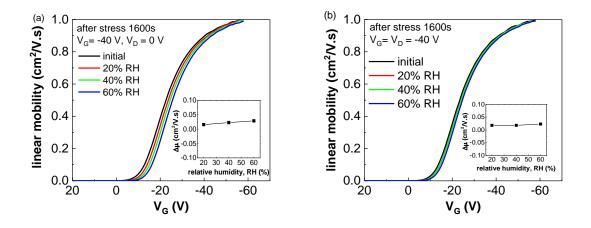

**Figure 5.22** Gate-voltage-dependent mobility for stress conditions of (a)  $V_G = -40$ V,  $V_D = 0$  V and (b)  $V_D = V_G = -40$ V obtained at relative humidity 20%, 40% and 60%......69

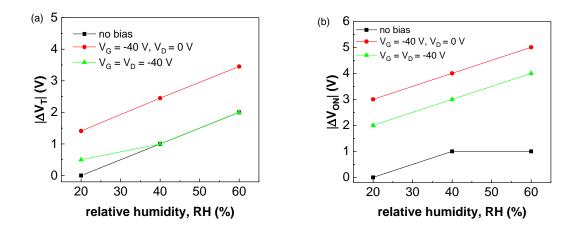

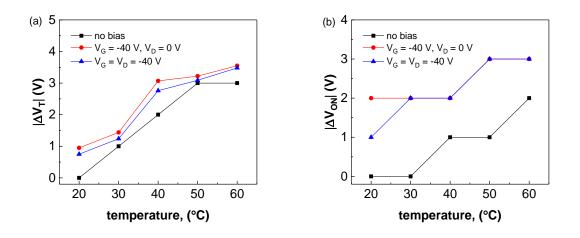

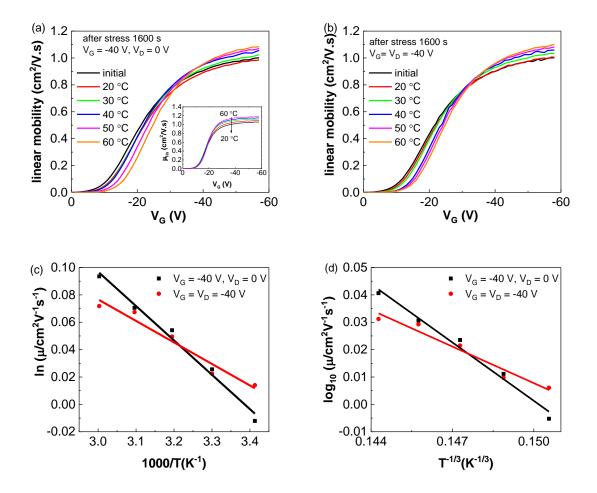

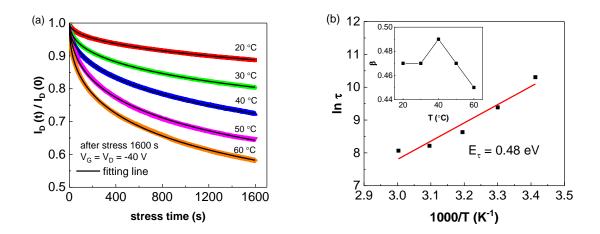

**Figure 5.23** Dependence of (a)  $\Delta V_T$  and (b)  $\Delta V_{ON}$  on RH% without bias and with bias stress of  $V_G = V_D = -40$  V and  $V_G = -40$  V,  $V_D = 0$  V over 1600s......70

**Figure 5.24** (a) Evolution of the drain current during bias stress at  $V_D = V_G = -40$  V over 1600 s for different relative humidity. The solid lines in (a) represent the fits made to the data using equation (5.10) with the parameters listed in Table 5.4. (b) Plots of  $\tau$  and  $\beta$  as a function of RH%.

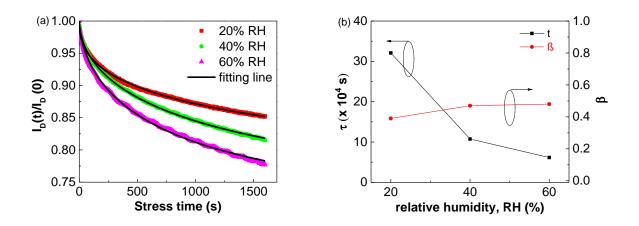

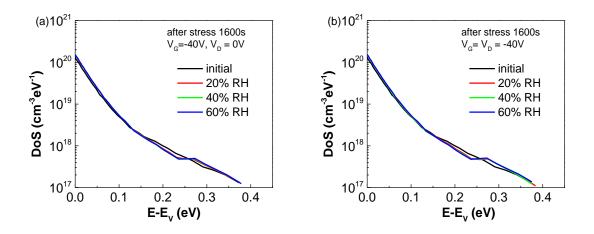

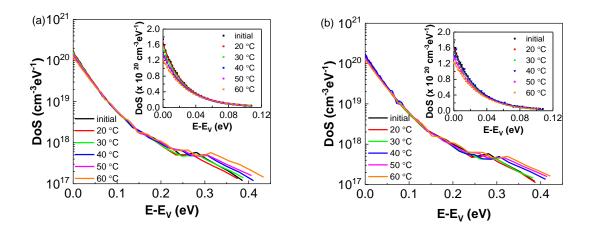

**Figure 5.25** DoS as a function of  $E \cdot E_V$  before and after stress conditions of (a)  $V_G = -40$ V,  $V_D = 0$  V and (b)  $V_D = V_G = -40$ V obtained at relative humidity 20%, 40% and 60%.......72

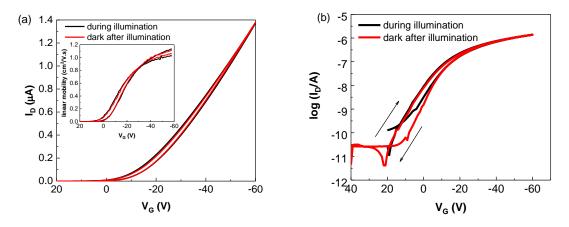

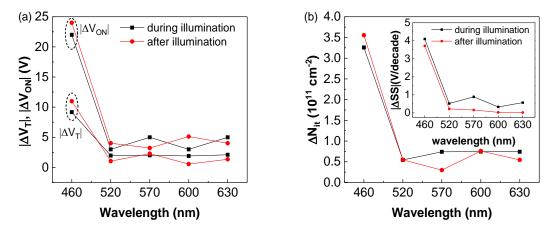

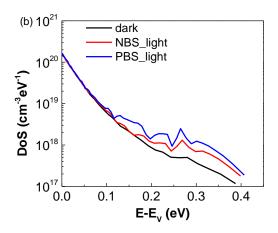

**Figure 6.7** DoS distribution obtained (a) during illumination and (b) in the dark after a 10 min illumination. Comparison of DoS in the forward and reverse gate voltage sweeps obtained (c) during illumination and (d) after illumination.....90

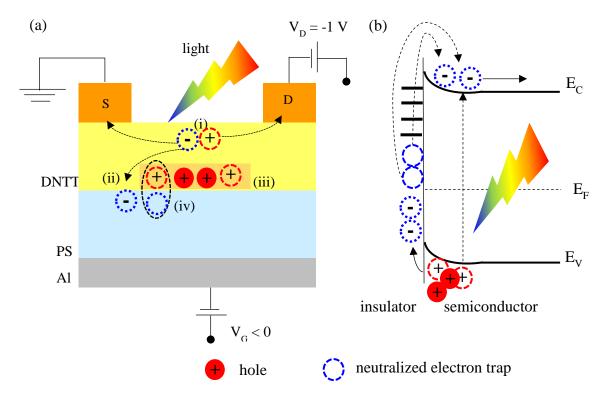

**Figure 6.13** (a) Cross-section diagram PS-DNTT TFT illustrates three possible mechanisms of photogenerated carrier under illumination in the off-state including; (i) electrons move towards source while holes move towards the drain via the bulk or (ii) near DNTT-PS surface

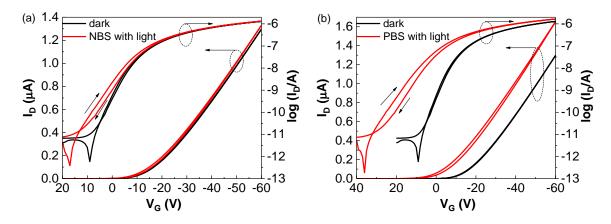

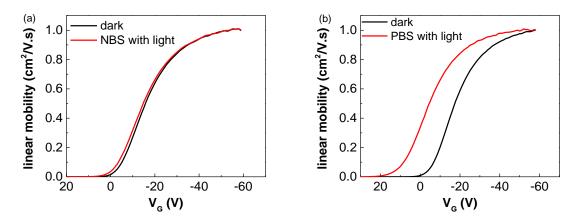

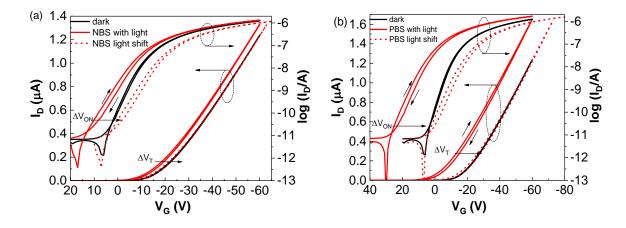

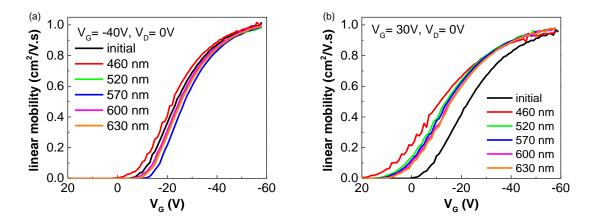

**Figure 7.2** Gate-voltage dependent mobility in the forward sweep, in the dark and after illumination under (a) NBS of  $V_G = -40$  V,  $V_D = 0$  V and (b) PBS of  $V_G = 30$  V,  $V_D = 0$  V for 2500 s in both cases.

**Figure 7.3** Transfer characteristics recorded in the dark and after ambient illumination, (a) under NBS and (b) under PBS for 2500 s. The dashed lines correspond to the illuminated characteristics shifted by an amount equal to the difference  $\Delta V_{ON}$  and  $\Delta V_T$  from the dark.

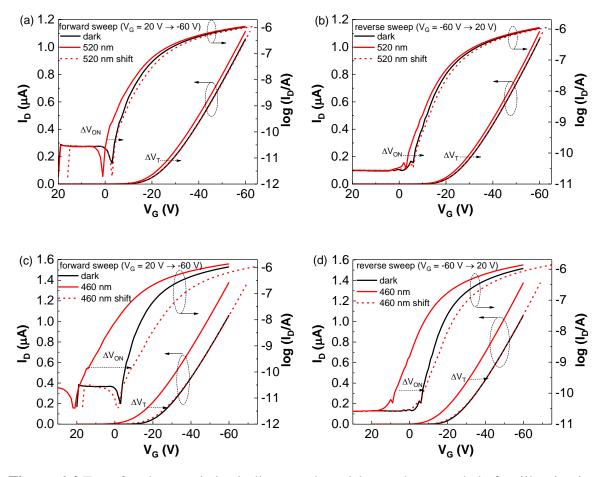

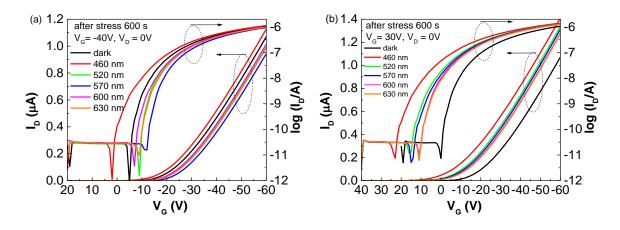

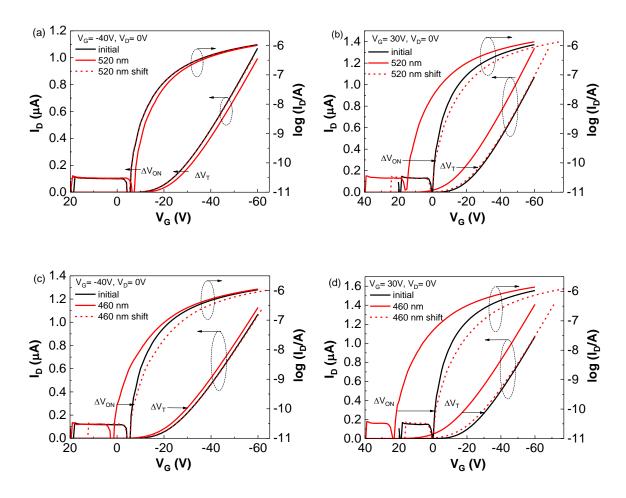

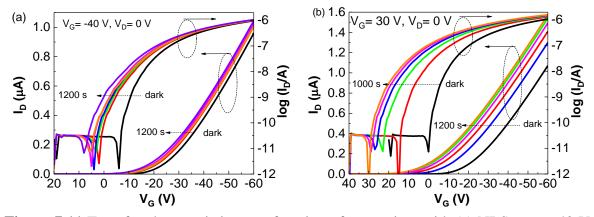

**Figure 7.7** Transfer characteristics on linear and semi-log scales recorded during forward gate voltage sweeps ( $V_G = 20 \text{ V}$  to -60 V) in the dark and after illumination at 520 nm, under

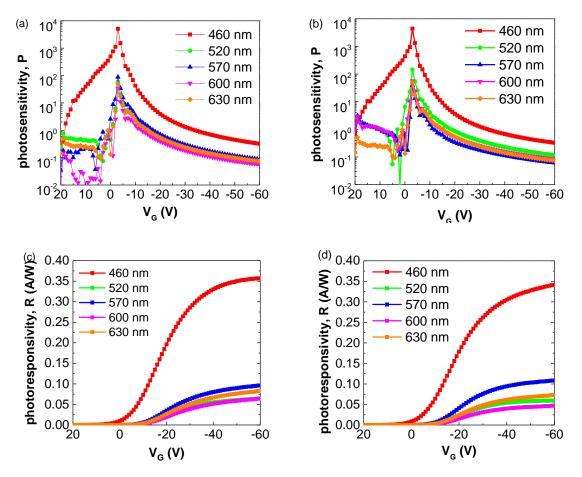

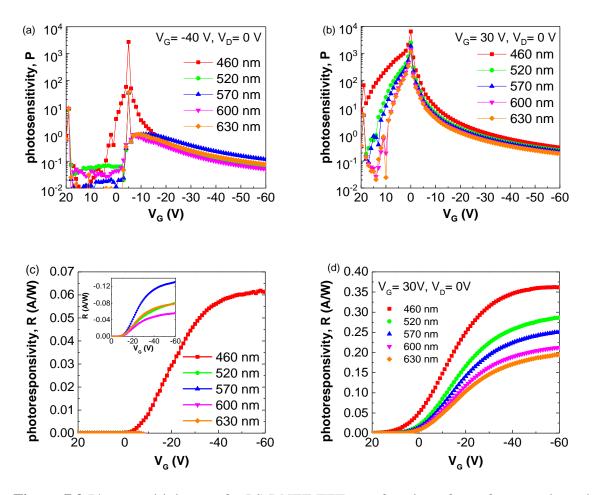

**Figure 7.9** Photosensitivity, *P* of a PS-DNTT TFT as a function of  $V_G$  after stressing with light of various wavelengths with (a) NBS  $V_G = -40 \text{ V}, V_D = 0 \text{ V}$  and (b) PBS  $V_G = 30 \text{ V}, V_D = 0 \text{ V}$ . Also shown is the photoresponsivity, *R* following illumination with (c) NBS  $V_G = -40 \text{ V}, V_D = 0 \text{ V}$  and (d) PBS,  $V_G = 30 \text{ V}, V_D = 0 \text{ V}$ . The inset in (c) shows photoresponsivity, *R* for  $\lambda > 460 \text{ nm}$ .

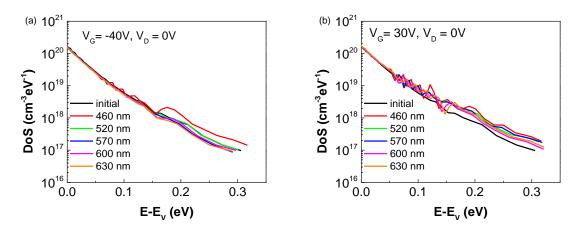

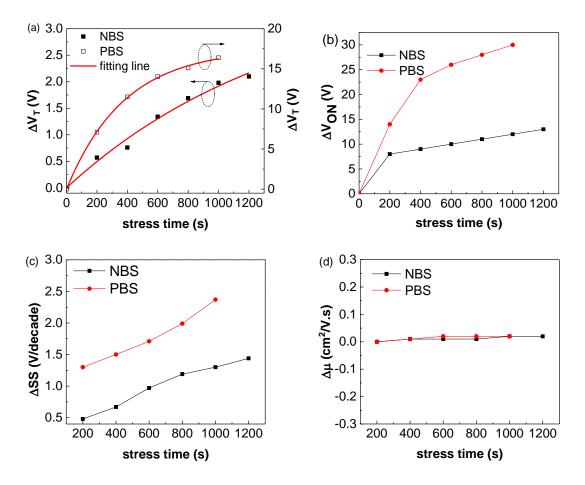

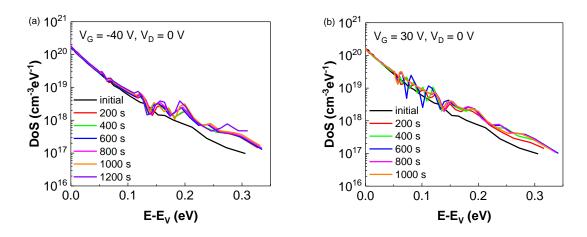

| <b>Figure 7.17</b> The distribution of density of state as a function of $E$ - $E_V$ with a stress conditions of (a) NBS $V_G = -40$ V, $V_D = 0$ V and (b) PBS $V_G = 30$ V, $V_D = 0$ V illuminated at different intensities. |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

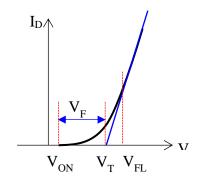

| Figure A.1 Transfer characteristics showing V <sub>ON</sub> , V <sub>T</sub> , V <sub>F</sub> and V <sub>FL</sub> 127                                                                                                           |

| Figure B.1 Constructions used to estimate onset of mobility edge128                                                                                                                                                             |

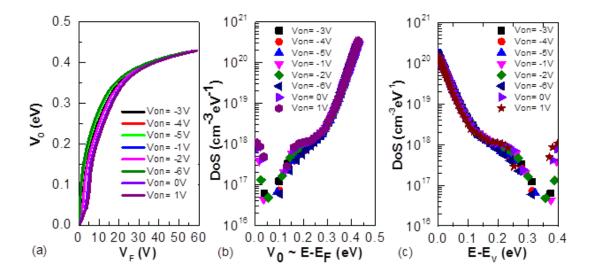

| <b>Figure C.1</b> Effect of $V_{ON}$ on (a) $V_0$ vs $V_F$ and DoS as a function of (b) $V_0$ and (c) $E$ - $E_V$ 129                                                                                                           |

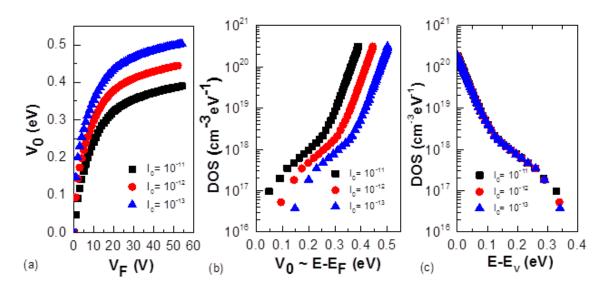

| <b>Figure C.2</b> Effect of $I_{0FF}$ on (a) the plot of $V_0$ vs $V_F$ and on the DOS as a function of (b) $V_0$ and (c) $E$ - $E_V$                                                                                           |

### LIST OF TABLES

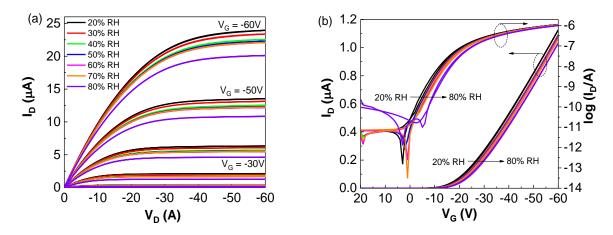

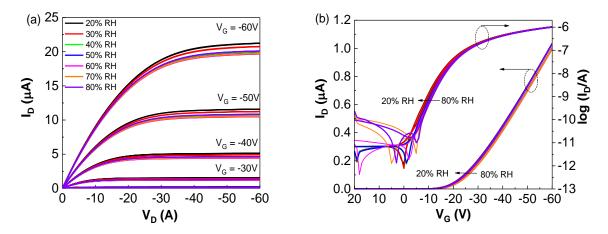

| <b>Table 4.1</b> Device parameters extracted from the transfer characteristics measured in the forward voltage sweep with $V_D = -1$ V, $T = 20$ °C and RH increasing from 20% to 80%. The values in brackets are for decreasing RH                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Table 4.2</b> Device parameters extracted from the transfer characteristics in Figure 4.4(b) obtained during the forward voltage sweep with temperature increasing from 20°C to 90°C, RH = 10% and $V_D$ = -1V. Values in the final column were obtained subsequently at 20°C after holding the device overnight at 20°C and 10% RH |

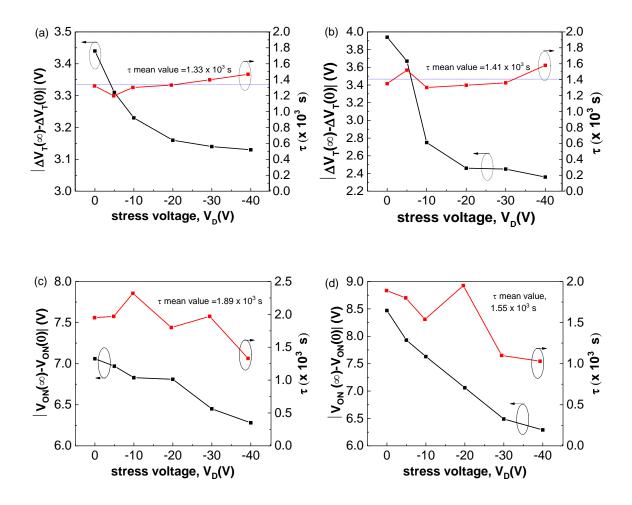

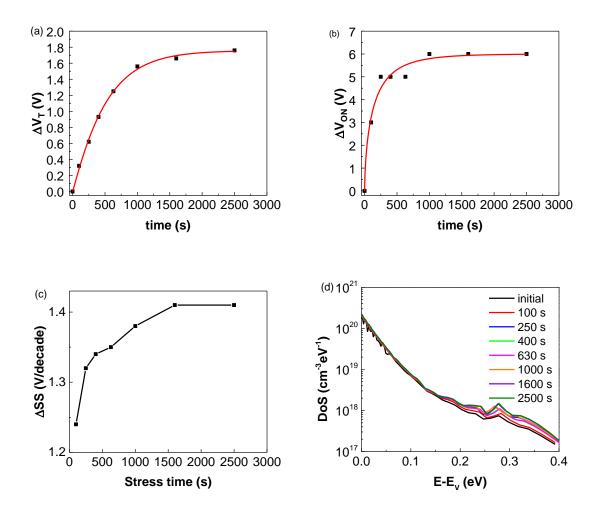

| <b>Table 5.1</b> Parameters obtained by fitting equation (5.2) to the measured bias stress-induced $\Delta V_T$ in Figures 5.15(a) and 5.15(b)                                                                                                                                                                                         |

| <b>Table 5.2</b> Parameters obtained by fitting equation (5.2) to the measured bias stress-induced $\Delta V_{ON}$ in Figures 5.15(c) and 5.15(d)                                                                                                                                                                                      |

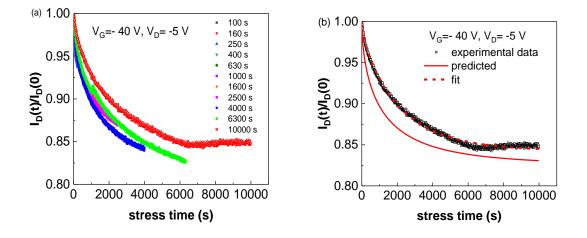

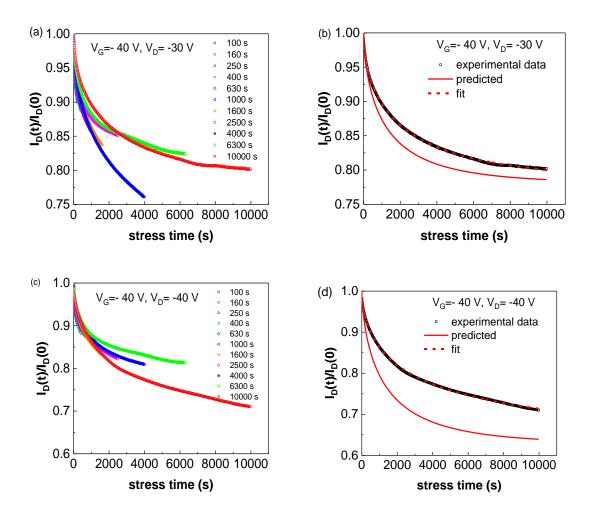

| <b>Table 5.3</b> Parameters for the fits of equation (5.6) in the linear and equation (5.10) in saturation regimes to the normalized current decay $I_D(t)/I_D(0)$ data in Figure 5.17(b), 5.18(b) and 5.18(d)                                                                                                                         |

| <b>Table 5.4</b> Parameters fits of equation (5.10) to the normalized current decay $I_D(t)/I_D(0)$ data in Figure 5.25(a) under bias stress of $V_G = V_D = -40$ V and with $\Delta V_T(\infty)$ assumed equal to 4.09 V                                                                                                              |

| <b>Table 5.5</b> Parameters fits of equation (5.10) to the normalized current decay $I_D(t)/I_D(0)$ data in Figure 5.30(a) under bias stress of $V_G = V_D = -40$ V                                                                                                                                                                    |

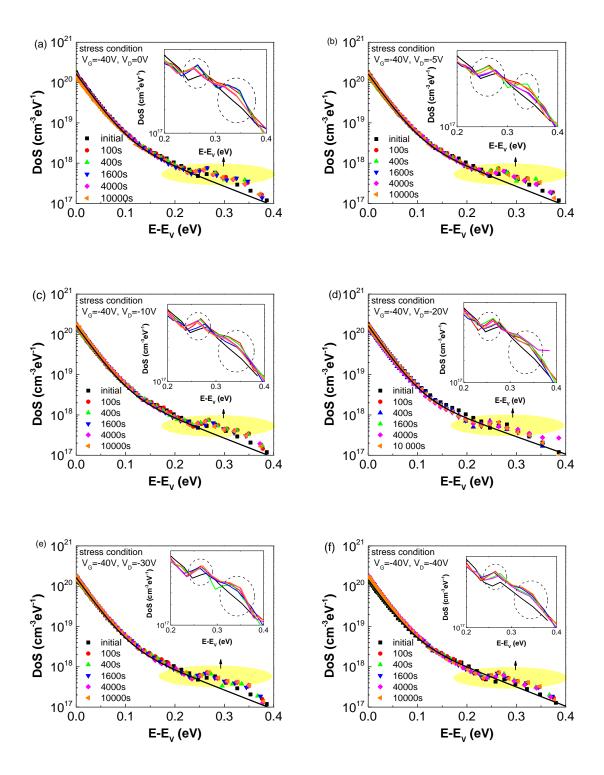

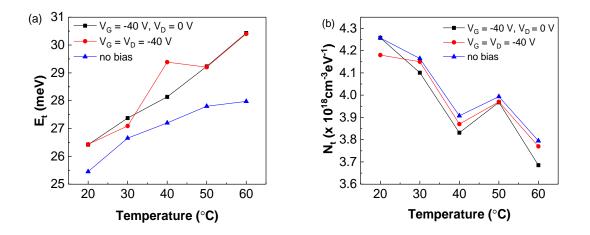

| <b>Table 5.6</b> Extracted total trap density, $N_t$ and characteristic energy decay of the distribution, $E_t$                                                                                                                                                                                                                        |

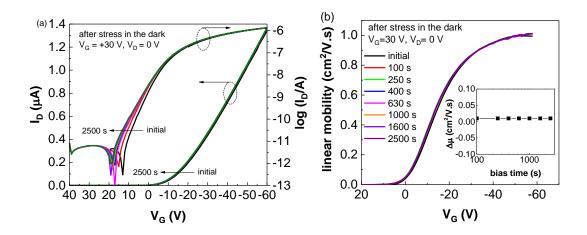

| <b>Table 5.7</b> Device parameters extracted from the transfer characteristics after stress conditions of $V_G = +30$ V and $V_D = 0$ V in the dark. Characteristics were obtained with $V_D = -1$ V, at $T = 20^{\circ}$ C and 10% RH                                                                                                 |

| <b>Table 7.1</b> Parameters obtained by fitting equation (7.1) to the measured $\Delta V_T$ in Figure 17.13(a).                                                                                                                                                                                                                        |

#### PAPERS AND CONFERENCE PRESENTATIONS

#### **Papers:**

- 1. N.K. Za'aba, JJ Morrison, DM Taylor (2017) "Effect of relative humidity and temperature on the stability of DNTT transistors: A density of states investigation" Organic Electronics 45 (2017) 174-181.

- 2. **N.K. Za'aba** and DM Taylor (2018) "Bias and Related Stress Effects in Organic Thin Film Transistors Based on dinaphtho [2,3-b:2',3'-f] thieno[3,2-b] thiophene (DNTT)" Organic Electronics 62 (2018) 382-393.

- 3. **N.K. Za'aba** and DM Taylor (2018) "Photo-induced Effects in Organic Thin Film Transistors based on DNTT " in preparation

#### **Conference Presentations:**

- 1. N.K. Za'aba and DM Taylor. (2016, July). Environmental Effects on the Operation of DNTT-based Thin Film Transistors. **International Conference on Electronic Materials (IUMRS-ICEM 2016)** at Suntec, Singapore. (oral presentation)

- N.K. Za'aba and DM Taylor. (2017, January). Environmental Stability of the Density of States in Evaporated DNTT Films. 3rd Innovation in Large-Area Electronics Conference (innoLAE 2017) at Genome Campus Conference Centre in Cambridge, United Kingdom. (poster presentation)

#### ABSTRACT

Exposure to moisture and elevated temperatures in organic thin film transistor (OTFT) usually results in significant degradation in the electrical performance. In this thesis the effects of temperature, *T*, and relative humidity, RH, on PS-DNTT OTFTs are investigated. Device characteristics were measured after 30-min exposure to RH that was gradually increased from 20% to 80% with *T* fixed at 20 °C and also for *T* increasing from 20 °C to 90 °C with RH held at 10%. The turn-on and threshold voltages show a negative shift with minimal change in mobility upon exposure to higher RH and T. A very minimal change was observed in the deeper states in the density of states (DoS) that was extracted from transfer characteristics in the linear regime using the Grünewald approach. These results suggest that OTFT instability is due to the flatband voltage shift caused by hole trapping/detrapping in the polystyrene gate dielectric or at the polystyrene/DNTT interface.

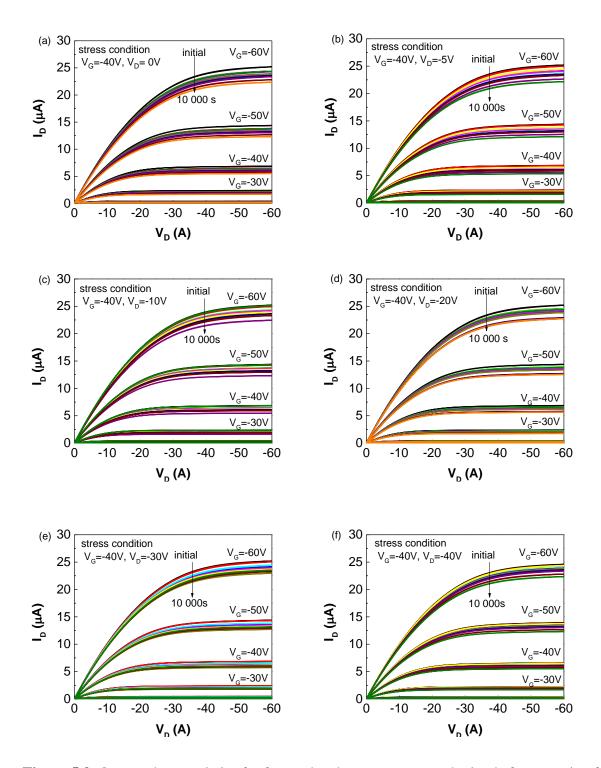

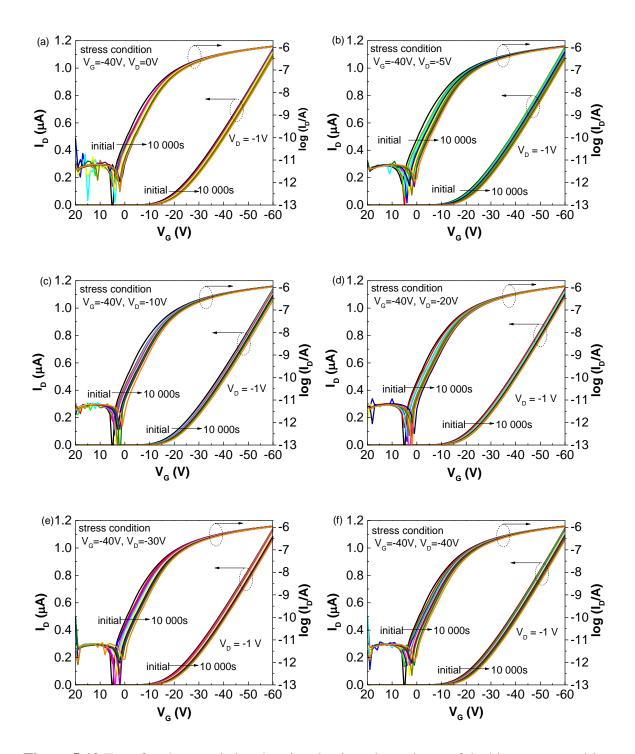

Understanding the origin of electrical instability in OTFTs over long periods of time is also essential to realize high performance circuits. In this thesis, the effects of bias stress on PS-DNTT OTFTs is investigated over a range of temperature and relative humidity. It was found that the threshold voltage,  $V_T$ , always shifted in the direction of the applied gate voltage. It was also observed that the threshold voltage shift,  $\Delta V_T$ , reduced as the drain voltage increased. The time-dependences of  $\Delta V_T$  in both linear and saturation regimes are well described by the stretched exponential function. Contrary to most previous reports, the threshold voltage at long times,  $V_T(\infty)$ , asymptotes to a value well below the applied gate voltage. The  $V_T$  change is minimal with increasing humidity under saturation bias and temperature. In all cases, the DoS exhibits similar behavior with weak features appearing at the deeper states. This is unlikely to be related to DNTT as there is no change in the gatevoltage dependence of mobility, but rather due to a changing flat-band voltage when electron/hole occupancy of interface states changes as the device turns on.

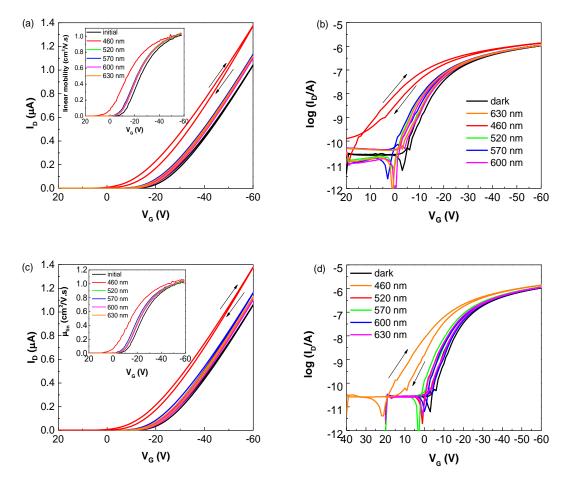

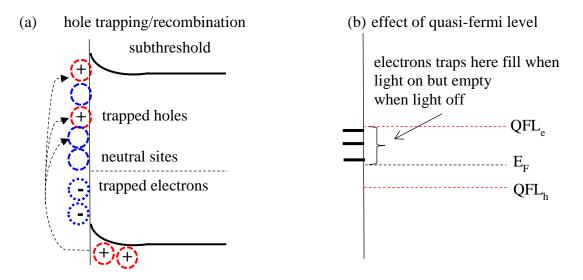

Effect of illumination on the electrical performance as well the underlying physics of these effects are important for the development of several applications such as the backplane for display technology and photosensors. In this thesis the effect of illumination on PS-DNTT OTFTs has been investigated with light of different wavelengths and intensities. The greatest effect was observed at 460 nm with significant changes occuring in the subthreshold slope. Interestingly the profile of the deeper states in the DoS spectrum did apparently change. It was also found that changes in threshold voltage, turn-on voltage, subthreshold slope and responsivity all appear to saturate at higher light intensity due to a trap limited effect. Since there is no significant change observed in mobility, the DoS changes can be explained by (i) trapping of photogenerated electrons, (ii) an unstable shift in the light-induced flat-band  $\Delta V_{FB}$ , caused by detrapping or neutralization of electrons as the transistor is turned on so that  $\Delta V_T(\infty) \leq \Delta V_{ON}(\infty)$ , (iii) accumulation of electrons in DNTT near to source contact or (iv) the effect of the electron quasi Fermi level, QFL. The effect of bias stress and illumination on PS-DNTT has also been investigated with different wavelengths, time and intensity. It was observed that the transfer characteristic shows a parallel shift toward more positive voltages under positive bias stress (PBS) regardless of the wavelength. However under negative bias stress (NBS) at  $\lambda \ge 520$  mm, the transfer characteristic shifts negatively due to the dominant effect of hole trapping at the PS-DNTT interface.

#### ACKNOWLEDGEMENTS

First and foremost, I would like to express my deep gratitude to my supervisor, Professor Martin Taylor, for his support, encouragement, and guidance for my research work. His invaluable advice and ideas really help me to gain deeper understanding in the overall process of research and communication. He is the best adviser, the best teacher, and a role model for me.

Special thanks go to Dr. Eifion Patchett for all the helpful discussions and assisting me during my research work. I also owe thanks to Bruno Rostirolla who was my main point of contact when technical issues arose. Sincere thanks are given to Dr. Colin Watson, Dr. Paul Sayers, Dinesh, Vasil, Amjad and Fahad who have willingly helped me with their knowledge and contributed to a pleasant working atmosphere in the group. Many thanks go to Dr. Yanhua Hong and Ben Assinder for their assistance with AFM work.

I would like to show my deepest gratitude to my friends and family especially my parents, Za'aba Mahat and Najibah Shamsudin, for their continuous support and endless love throughout all my life. I also owe my deep thanks to my friend, Mazlina, who has been giving me invaluable support. Finally, my special thanks to my husband, Muhzill. This thesis would not have been possible without the wholehearted support and encouragement from my husband. This thesis is dedicated to all of them.

#### **1** Introduction

#### 1.1 Introduction

There has been significant advancement towards realizing high performance organic electronic circuits. Recently, Watson et. al [1] and Ogier et al [2] successfully fabricated, 5-stage ring oscillators operating at frequencies in the MHz range. Considerable research efforts are also being made in the development of functioning circuits that are compatible with roll-to-roll (R2R) processing [3, 4]. It is known that pentacene is among the most widely studied p-type semiconductor in organic thin film transistors (OTFTs). However, pentacene suffers from the disadvantage of oxidation when exposed to the atmosphere. Unlike pentacene, OTFTs based on dinaphtho[2,3-b:2',3'-f]thieno[3,2-b]thiophene (DNTT) are more resistant to oxidation by atmospheric oxygen owing to the larger ionization potential. Moreover, the carrier mobility,  $\mu$ , which is typically ~ 1 cm<sup>2</sup>/Vs is comparable to amorphous silicon and higher than that of pentacene [3, 5]. There is also considerable research effort in the development of functioning circuits based on DNTT [6-8]. Recent reports have shown that OTFTs based on DNTT meet performance requirements for application in electronic circuits [3, 5, 7, 9-12].

Taking these factors together, a DNTT-based OTFT is a potential candidate for the realization of organic electronic circuits that are compatible with vacuum R2R processing. In 2011, Abbas *et al.* [13] introduced a fully vacuum-processed method suitable for R2R OTFT production. The method relied on the preparation of a polymerized dielectric material, tripropyleneglycol diacrylate (TPGDA) [14]. In 2013, Patchett *et al.* [3] fabricated 90 transistor arrays, inverters and ring oscillators with TPGDA as the dielectric layer. This report showed that, with TPGDA as a dielectric layer and polystyrene (PS) as a buffer layer, it was possible to achieve an average saturation mobility of  $1.51 \text{ cm}^2/\text{Vs}$  with a yield of ~ 90% [3]. Working 5- and 7-stage ring oscillators operating in the range from 120 Hz to > 2 kHz with rail voltages,  $V_{DD}$  increasing from -15 V to -90 V were also reported [3]. PS is favorable as the dielectric material in OTFT because it is very stable in air and easy to form a uniform thin film by spin coating. It is also well suited for printing technique such as inkjet. Moreover, PS can also be layered using R2R compatible doctor blading and slot dye techniques. Taylor *et al.* [15] demonstrated considerable progress by fabricating circuits based on inverters, NOR and NAND logic gates, and more complicated circuits such as a modified Wilson mirror circuit and a simple memory element (SR latch). The logic gates were reported to operate at frequencies in excess of 1 kHz while the current mirror circuit produced currents up to  $18 \,\mu\text{A}$  [3].

Despite the significant progress represented by the above reports, understanding the stability issues in OTFTs is still necessary to realize high performance circuits. The performance of circuits over long periods of time depends on the stability of individual transistors. Therefore, it is important to achieve long-term stability in the ambient environment at the individual transistor level to ensure high performance. Environmental and electrical stability are very critical issues that must be investigated. Exposure of OTFT to the ambient environment is known to induce degradation of electrical performance. The degradation has been typically attributed to the presence of moisture and oxygen. Although OTFT will be encapsulated, long-term O<sub>2</sub> and H<sub>2</sub>O will diffuse through encapsulating films. Moreover, other aspects such as light and temperature are also known to affect the electrical performance of OTFTs. The bias-stress effect is known to change OTFT characteristics as a result of a prolonged application of gate voltage.

However, only a few papers reported on the environmental and bias stress stability of OTFTs based on DNTT and most of these studies only focused on achieving the best stability [5, 16]. Furthermore, there are no reports on OTFTs based on DNTT as the semiconductor and PS as the dielectric. Therefore this thesis aims to investigate the electrical and environmental stability of OTFT based on PS-DNTT as outlined in the next section.

#### **1.2** Thesis Outline

The theoretical background of the work is presented in Chapter 2. Firstly the basic properties of organic semiconductors is discussed followed by a brief review of their charge transport and charge trapping properties. Then, the OTFT operation and the electrical characteristics, as well as the density of states, are explained. Finally, the environmental and the electrical stability of OTFTs are discussed.

The experimental methods are given in detail in Chapter 3, together with a list of the fabrication materials that are used – aluminium, gold, PS and DNTT. Then follows a description of the characterization procedures used for the bias stress and phototransistor measurements.

The effects of moisture and elevated temperatures on the PS-DNTT OTFTs are presented in Chapter 4. Here the density of states in DNTT is analyzed after exposure to a relative humidity (RH) that was gradually increased from 20% to 80% and temperatures from 20 °C to 90 °C.

In Chapter 5, the effects of bias stress are investigated over a range of temperature and relative humidity. Here the variation of the threshold voltage is monitored over time, after applying to the device a constant negative voltage on the gate and drain contacts. It also contains a study of the effect of positive bias stress on the operational stability of OTFTs.

In Chapter 6, the effect of illumination on PS-DNTT OTFTs is investigated and discussed. The response to different wavelengths is described first. The influence of electron and hole trapping was identified by monitoring changes in the transfer characteristics during and after illumination. The effect of intensity on the electrical performance was also investigated. Lastly, the dynamic responses to positive and negative bias stresses are discussed in detail.

In chapter 7, results are presented and discussed for the combined effect of bias and illumination on the DNTT OTFTs. In particular, the additional effect of bias stress on the electrical characteristics with a different wavelength, intensity and time are analyzed. Photoresponsivity and photosensitivity of the DNTT OTFTs to different wavelengths and intensity, when subjected to simultaneous bias, are also discussed.

Finally, in Chapter 8, the conclusions derived from various measurements are presented. Future work related to stability and development of n-type and complementary circuit, with DNTT as the p-type semiconductor that is compatible to vacuum roll to roll (R2R) of are also proposed.

#### **2** Background Theory and Literature Review

#### 2.1 Introduction

This chapter presents background theory of organic semiconductor devices. Firstly, the basic properties of the organic semiconductors are reviewed and is followed by discussion of their charge transport and charge trapping properties. Then, the OTFT operation, the electrical characteristics and the density of states are explained. Finally, the environmental and electrical stability of OTFTs are discussed.

#### 2.2 Basic Properties of Organic Semiconductor

Most organic semiconducting materials consist of  $sp^2$  hybridized carbon atoms. The electronic configuration of a carbon atom is  $1s^22s^22p^2$ . In the ground state, each 1s and 2s orbital are filled with a pair of electrons. In 2p orbitals, only a single electron occupies the  $2p_x$  and  $2p_y$  while the  $2p_z$  orbital is empty as shown in Figure 2.1. In the excited state, one of the electrons from the 2s orbital is promoted to the  $2p_z$  orbital resulting in three  $sp^2$  hybridisation.

**Figure 2.1** Electronic configuration of a carbon atom in the ground and excited states and after hybridisation.

A simple example of hybridization can be demonstrated by the ethylene (C<sub>2</sub>H<sub>4</sub>) molecule as shown in Figure 2.2(a). It can be seen that  $\sigma$  bonds are form from the overlap between sp<sup>2</sup> orbitals of carbon atoms with s orbitals of hydrogen atoms, ( $\sigma(sp^2- s)$ ). Another  $\sigma$  bond is form between two adjacent carbon atoms ( $\sigma(sp^2- sp^2)$ ). On the other hand, the un-hybridised 2p<sub>z</sub> orbitals of the carbon atoms form weak  $\pi$  bonds. In benzene, the formation of three double bonds ( $\sigma$  and  $\pi$  bonds) alternating with three single bonds (only  $\sigma$  bonds) between carbon atoms is known as conjugation. The electrons of the double bond are delocalised and move around the molecule as shown in Figure 2.2(b) and (c). The resulting  $\pi$ -bonds are filled with a pair of electrons and unoccupied anti-bonding,  $\pi$ \*, orbitals that are separated by an energy gap,  $E_g$ , the energy difference between the highest occupied molecular orbital, HOMO and the lowest unoccupied molecular orbital, LUMO as shown in Figure 2.2(d).

**Figure 2.2** (a) Hybridisation of the ethylene molecule structure, (b) electron delocalization in benzene to form the structures seen in (c), and (d) schematic of energy level splitting between HOMO and LUMO.

#### 2.3 Organic Semiconductors

Organic semiconductors can be generally classified as either polymers or small molecules. Most polymeric semiconductor materials are known to have excellent solubility which make them applicable for large area printing processes. On the other hand, the majority of small molecule semiconductor materials are insoluble and often deposited via a vacuum process. One of the most popular small molecule organic semiconductors is pentacene (Figure 2.3(a)). However it suffers instability towards oxidation which in turn causes the carrier mobility to decrease over time when exposed to oxygen and/or humidity [5]. In order to improve the air stability and mobility, Yamamoto and Takimiya [17] synthesized dinaphto-[2,3-b:2`,3`-f]thieno[3,2-b]thiophene (DNTT) (Figure 2.3(b)) with a larger ionization potential of 5.4 eV compared to that of pentacene of 5.0 eV. Owing to its larger ionization potential, the air stability was greatly enhanced. Additionally, DNTT was shown to have a mobility as high as 2.9 cm<sup>2</sup>/V.s [17] in evaporated films.

Figure 2.3 Molecular structures of (a) pentacene and (b) DNTT.

Unlike inorganic semiconductors, small molecule organic semiconductors are usually undoped (intrinsic semiconductors). Thus the notion of p-type or n-type organic semiconductors depend on the HOMO and LUMO levels rather than the possibility of doping. As for p-type semiconductors, holes are more easily injected than electrons while ntype it is vice versa. Generally, holes have higher mobility than electrons in organic semiconductor and is used to defining property of p-type organic semiconductor.

#### 2.4 Charge Transport in Organic Semiconductor

The interaction of the delocalized  $\pi$ -electrons discussed in section 2.2 is the key to charge transport in organic semiconductors. Several models have been developed to describe the

charge transport properties. However this section only focuses on the most common transport mechanisms i.e. multiple trapping and release (MTR) and hopping transport.

#### 2.4.1 Multiple Trapping and Release Transport (MTR)

The multiple trapping and release (MTR) model invoked the mobility edge assumption. The mobility edge separates extended states (delocalized states) from a high concentration of charge traps in the localized states (zero mobility). Charge carriers can only be transported via extended states above mobility edge but their movement will be interrupted by trapping in localized states [18]. Then the charge carriers are released back thermally to the extended states and contribute to the transport of charge under influence of an electric field. The MTR transport model predicts an Arrhenius-like temperature dependence. The thermally activated mobility,  $\mu$ , is usually expressed as [19, 20]:

$$\mu = \mu_0 exp\left(\frac{-E_a}{kT}\right) \tag{2.1}$$

where  $E_a$  is the activation energy, with q the electronic charge, k Boltzmann's constant and T the absolute temperature

#### 2.4.2 Hopping Transport

Charge transport through extended states may only occur in a highly ordered system. In a very disordered system, the charge carriers are strongly localized in the band gap. Thus the charge carrier is unlikely to move from localized states to delocalized states. Instead, charge transport is governed by hopping which takes place by thermal activation and tunneling between localized states within the band gap. Since the hopping transport involves some thermal activation, the charge mobility is expected to be temperature dependent following Mott's law [21, 22] described by:

$$\mu = \mu_0 exp \left[ -(T_0/T)^{1/1+D} \right]$$

(2.2)

where *T* is temperature,  $T_0$  is the characteristic temperature,  $\mu_0$  is the characteristic mobility and and *D* is the hopping space dimensionality. Transport of charge carriers through the accumulation layer at the semiconductor-insulator interface of organic thin film transistors (OTFTs) can be described by a two-dimensional (2-D) system [23-26], thus equation (2.1) can be expressed as:

$$\mu = \mu_0 exp[-(T_0/T)^{1/3}]$$

(2.3)

#### 2.5 Trap Density of States (DoS) in Organic Semiconductor

Organic semiconductors generally exhibit a disordered structure that leads to a distribution of localized states which can act as traps for charge carriers which in turn, could limit the charge transport and device performance. As shown in Figure 2.4, these localized states (trap density of states) are located in the band gap of the semiconductor between HOMO and LUMO. Shallow states usually located within a few kT of HOMO/LUMO while the deep states are located further away. Also, below the HOMO and above the LUMO are delocalized states in which carriers are mobile.

Figure 2.4 Schematic of density of states in an organic semiconductor adapted from [27].

Trap states in the semiconductor could originate from grain boundaries [28], chemical impurities [29] or from the gate insulator [30]. Several methods have been developed to quantify the trap density of states (DoS) of OTFTs which have been comprehensively

reviewed by Kalb and Batlogg [31]. One of the simpler analytical methods for DoS extraction was introduced by Grünewald et al [32]. It is simple because, the trap DoS relative to the Fermi level can be extracted from a single transfer characteristic. This model has been applied to describe the DoS in both inorganic [33, 34] and organic [31, 35-37] semiconductors. Basically, the Grünewald model is based on the gate-induced incremental increases in device current and the band-bending resulting from the accumulation of charge carriers at the semiconductor/insulator interface [37]. Derivation of this method is presented in section 2.6.4.

#### 2.6 OTFT Operation and Characteristics

#### 2.6.1 OTFT Device Architecture

Figure 2.5 shows four possible cross-sections of OTFT structures. The device structural configuration is based on the position of the electrodes (drain, source and gate) relative to the organic semiconductor. In a staggered structure, the source, and drain electrodes are located away from the semiconductor/insulator interface (Figure 2.5(a) and (c)) whereas in the coplanar structure, the source, and drain electrodes are in the plane of the interface as shown in (Figure 2.5(b) and (d)). Both staggered and coplanar structures are further categorized based on the position of the gate contact e.g. top-contact-bottom-gate and top-gate-bottom-contact.

**Figure 2.5** Cross-sections of simplified OTFT device configurations: (a) top-contact-bottomgate (staggered), (b) bottom-contact-bottom-gate (coplanar), (c) top-gate-bottom-contact (staggered) and (d) top-gate-top-contact (coplanar).

#### 2.6.2 OTFT Operation Principle

In order to explain the operation of an OTFT, it is important to understand the energy band diagram of the metal-insulator-semiconductor (MIS) structure. Figure 2.6 shows the MIS energy band diagrams based on a doped p-type inorganic semiconductor. In an ideal MIS structure, under a flatband condition,  $V_G = 0$ V the work function difference between metal,  $q\phi_m$ , and semiconductor,  $q\phi_s$ , is zero. The Fermi level,  $E_{FM}$  of the metal is aligned with the Fermi level,  $E_{FS}$  of the semiconductor as shown in Figure 2.6(a). Electron affinities for the insulator and semiconductor are denoted as  $\chi_i$  and  $\chi$  respectively. All bands remain flat and carriers are in thermal equilibrium. Here, the conduction band edge,  $E_C$  is analogues to the LUMO level in organic semiconductors whereas the valence band edge,  $E_V$  corresponds to the HOMO level. The energy gap between  $E_V$  and  $E_C$  is denoted as  $E_G$  while the potential energy difference between  $E_{FS}$  and the intrinsic Fermi level,  $E_{Fi}$  in the bulk is defined as  $q\phi_b$ .

When a negative gate voltage,  $V_G$  is applied across the semiconductor, majority holes drift to, and accumulate near the insulator-semiconductor interface. As a result,  $E_V$  bends upwards and moves closer to  $E_{FS}$  at the insulator-semiconductor interface as shown in Figure 2.6(b). The difference between  $E_{FM}$  and  $E_{FS}$ , is equal  $qV_G$ . The potential energy drop across the insulator is defined as  $qV_0$  and the amount of band bending from the interface into the bulk semiconductor is represented by  $qV_s$ . For a larger negative  $V_G$ , the amount of band bending is greater. When a small positive  $V_G$  is applied, majority holes move away from the interface thus exposing the immobile negative charges of the ionized acceptors as seen in Figure 2.6(c). As a result, a depletion region of immobilized charged acceptor ions is formed and the bands bend downwards. When a larger positive  $V_G$  is applied, the electric field is strong enough to cause electrons to accumulate at the interface. At this point, the band bending increases beyond  $E_{Fi}$  and causes inversion.

In contrast to a doped semiconductor, organic semiconductors are often undoped (intrinsic) and do not operate in the inversion mode but in the accumulation mode. In intrinsic case, the depletion mode is the same as flatband (no injected hole in the device) and accumulation. In intrinsic, the density of holes and electrons are always equal. At absolute zero temperature the valence band is completely filled and the conduction band is completely empty. At high temperature, electrons from valence band get enough thermal energy and left behind equal

number of holes in valence band. However, in organic semiconductor,  $E_{FS}$  generally is closer to the HOMO being held there by trap states. The band gap is too large to generate electron/hole pair thermally. For voltages more positive than flatband voltage, part of the applied voltage appears across semiconductor and the electrons in conduction band were attracted to the surface and the holes were pushed away from the interface shown in Figure 2.6(d). For voltages more negative than flatband voltage, holes were attracted to the semiconductor surface which is similar to the case of an extrinsic semiconductor in accumulation as shown in Figure 2.6(b).

**Figure 2.6** Band diagram of and ideal metal-insulator-semiconductor (p-type) structure showing (a) flatband conditions,  $V_G = 0$  V (b) accumulation, negative  $V_G$  and (c) depletion positive gate  $V_G$ . Band diagram of intrinsic semiconductor with (d) positive gate voltage.

In general OTFTs operate in the accumulation regime. The operating principle of a p-type organic transistor is illustrated in Figure 2.7. When  $V_G < 0$  V, and  $V_D = 0$  V is applied between gate and source electrodes, holes are induced by the electric field across the insulator and accumulate at the semiconductor/insulator interface as shown in Figure 2.7(a). This accumulation of holes will form a conducting channel in the semiconductor between the source and drain electrodes. When a small drain voltage is applied ( $V_D < 0$  V), the charge carriers flow from the source to the drain electrodes and generate a large drain current,  $I_D$  as shown in Figure 2.7(b). At this point,  $I_D$  increases linearly with the field induced charge density and is known as linear regime.

**Figure 2.7** Operating stages of an OTFT, (a)  $-V_G$ ,  $V_D = 0V$ , (b)  $-V_G$ ,  $-V_D$  (slow), (c)  $-V_G$ ,  $-V_D$  (medium) and (d)  $-V_G$ ,  $-V_D$  (high).

As the drain voltage,  $V_D$  increases towards more negative values ( $|V_D| < |V_G|$ ), for a given  $V_G$ , the charge density at the drain electrode starts to decrease but at the source electrode, they remain the same[38] as shown in Figure 2.7(c). Consequently, drain current  $I_D$  increases

at a slower rate and there is no longer a linear correlation. When  $V_D$  increases until a point where  $|V_D| > |V_G|$ , the channel at the drain electrode starts to pinch-off (Figure 2.7(d)) after which  $I_D$  saturates and become independent of  $V_D$ .

#### 2.6.3 OTFT Characteristics and Parameter Extraction

The current-voltage characteristics of an OTFT were derived based on the gradual channel approximation with the x direction is defined as perpendicular to the channel and y parallel to the channel as shown in Figure 2.8. The edge of the source is at y=0 and the edge of the drain at y=L. It is assume that the mobility along the channel is constant. However, this is not always fulfilled in some organic semiconductor system. Then it is assume that the electric field,  $E_x$  through the insulator is much higher compared to the electric field,  $E_y$  along the channel. This is known as gradual channel approximation.

**Figure 2.8** Cross-sectional view of the channel region of TFT used to derive the gradual channel approximation with x direction is perpendicular to the channel and y is parallel to the channel.

By applying a negative voltage  $V_D$  at the drain, the charge density Q(y) that is induced by  $V_G$  along the channel is given by:

$$Q(y) = C_i[(V_G - V_T) - V(y)]$$

(2.4)

where *Ci* is the capacitance per unit area of the insulator,  $V_T$  is the threshold voltage and V(y) is the channel voltage. The charge density that flows from source to drain generates a current  $I_D(y)$  given by:

$$I_D = -WC_i [(V_G - V_T) - V(y)] (\mu E_y)$$

(2.5)

where *W* is the width of the channel and  $\mu$  is the charge mobility. Substituting  $E_y = -dV/dy$  into equation (2.5) gives

$$I_D = \mu W C_i [(V_G - V_T) - V(y)] \left(\frac{dV}{dy}\right).$$

(2.6)

Integration of equation (2.6) along the channel from y = 0 to y = L and V(y) = 0 to  $V(y) = V_D$  leads to:

$$\int_{0}^{L} I_{D} dy = \mu W C_{i} \int_{0}^{V_{D}} [(V_{G} - V_{T}) - V(y)] dV$$

(2.8)

which eventually yields,

$$I_D = \frac{\mu W C_i}{L} \left[ (V_G - V_T) V_D - \frac{V_D^2}{2} \right].$$

(2.9)

For  $V_D \ll V_G$  the quadratic term in equation (2.9) can be neglected. This defines the linear regime of the OTFT and the drain current can be described by:

$$I_{D} = \frac{\mu_{lin} W C_{i}}{L} [(V_{G} - V_{T}) V_{D}]$$

(2.10)

where  $\mu_{lin}$  is the field effect mobility in the linear regime and can be extracted from the transconductance,  $\frac{\partial I_D}{\partial V_G}$  that is:

$$\mu_{lin} = \frac{L}{WC_{ins}V_D} \frac{\partial I_D}{\partial V_G}.$$

(2.11)

For  $V_D \ge (V_G - V_T)$ , the channel is in pinch-off, so  $I_D$  become independent of  $V_D$  and saturates. This is known as the saturation regime of the OTFT. Substituting  $V_D = (V_G - V_T)$  into equation (2.9), the expression for the drain current in the saturation regime becomes:

$$I_D = \frac{\mu_{sat} W C_i}{2L} (V_G - V_T)^2$$

(2.12)

where the field effect mobility in the saturation regime ,  $\mu_{sat}$  is given by:

$$\mu_{sat} = \frac{2L}{WC_{ins}} \left(\frac{\sqrt{\partial I_D}}{\partial V_G}\right)^2.$$

(2.13)

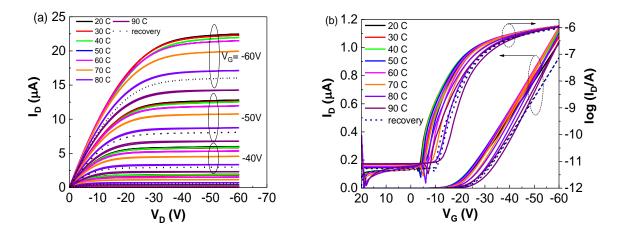

The current-voltage characteristics of an OTFT can be described by output characteristics ( $I_D$  versus  $V_D$ ) and transfer characteristics ( $I_D$  versus  $V_G$ ). Figure 2.9(a) shows typical output characteristics obtained in the study for an OTFT based on DNTT with polystyrene as the gate insulator. It shows a clear linear and saturation region. The transfer characteristic in the linear regime plotted on linear and semilog axes is shown in Figure 2.9(b). The threshold voltage,  $V_T$  is defined as the gate voltage,  $V_G$ , intercept (i.e.,  $I_D = 0$ ) of the linear extrapolation of the  $I_D - V_G$  plot. The linear mobility,  $\mu_{lin}$  can be estimated from the slope of a linear fit to the  $I_D-V_G$  plot using equations (2.11). In the case of the saturation regime, the transfer characteristic is plotted as  $I_D^{1/2}-V_G$  and the saturation mobility,  $\mu_{sat}$  can be determined from the slope of the linear fit the  $I_D-V_G$  plot using equations (2.13).

The onset voltage  $V_{ON}$  can be estimated from the semi-log plot of the transfer characteristics. It should correspond to the voltage above which  $I_D$  rises above its off value, i.e. the current flowing through the bulk semiconductor from source to drain in the absence of an accumulation channel. However in the present case, it was defined as the value of  $V_G$  when the magnitude of  $I_D$  increased above the displacement current, induced by the  $V_G$  sweep.  $I_{on}/I_{off}$ , is the ratio of the drain current in the on-state at a certain gate voltage to the drain current in the off-state. It is desirable to have this ratio as large as possible. The subthreshold slope, *SS* is extracted from the steepest slope of the semilog plot using the relation:

$$SS = \frac{\partial V_G}{\partial (logI_D)} \cdot$$

(2.14)

For an intrinsic semiconductor,  $V_{ON}$ , should occur at flatband,  $V_G = 0V$ . Departures from this can be caused by the work function difference between the source-drain metal contacts

(usually gold) and the gate electrode (often aluminium). A more important effect is the flatband voltage shift caused by interface trapped charges,  $N_{it}$  which can be estimated from:

$$\Delta N_{it} \approx \frac{1}{q} C_{ins} \Delta V_{FB} \, \cdot \tag{2.15}$$

Figure 2.9 (a) Output characteristics and (b) The transfer characteristic of a PS-DNTT TFT measured in the dark at a drain voltage,  $V_D = -1V$  plotted in linear and semilog scale.

#### 2.6.4 Extraction of the Density of Trap State Using the Grünewald Model

#### i. Grünewald Model

The extraction of DoS, from the transfer characteristic of a thin film transistor was performed using the Grünewald et al model [18]. This was accomplished by first developing the relationship between the gate-dependent insulator/semiconductor interface potential,  $V_0$ , and the effective forward voltage,  $V_F = (V_G - V_{ON})$ . This is achieved by numerically solving the equation

$$\exp(\beta V_0) + \beta V_0 - 1 = \beta \frac{C_i l}{\varepsilon_s \varepsilon_0 I_0} \left[ V_F I(V_F) - \int_0^{V_F} I(\tilde{V_F}) d\tilde{V_F} \right]$$

(2.16)

where *l* is the thickness of the semiconductor,  $\beta = q/kT$ ,  $\varepsilon_S$  the relative permittivity of the semiconductor and  $\varepsilon_0$  the permittivity of free space. *I*<sub>0</sub> is the off-current at *V*<sub>ON</sub>. Following

further manipulation, the total hole density  $p(V_0)$  and the density of states N(E) may be obtained from

$$p(V_0) = \frac{C_i^2}{\varepsilon_s \varepsilon_0 q^2} V_F \left(\frac{dV_0}{dV_F}\right)^{-1}$$

(2.17)

and finally, the density of states, N(E) from,

$$N(E) \approx \frac{dp(V_0)}{dV_0}.$$

(2.18)

The extraction method is described more fully in appendices A, B and C.

#### ii. Subthreshold Slope

Kalb and Batlogg [31] suggest that the derivation of subthreshold slope, *SS* could give a rough estimation of the DoS. Assuming that the DoS is independent of energy, *SS* can be described by [39]

$$SS = \frac{kTln10}{q} \left[ 1 + \frac{q}{C_i} \left( \sqrt{\varepsilon_s N_b} + q N_{it} \right) \right]$$

(2.19)

Here  $N_b$  (in cm<sup>-3</sup>eV<sup>-1</sup>) is the density of deep bulk traps and  $N_{it}$  (in cm<sup>-2</sup>eV<sup>-1</sup>) is the density of interface traps. Assuming that there is no contribution from the bulk, equation (2.19) may written as:

$$SS = \frac{kTln10}{q} \left[ 1 + \frac{q^2}{C_i} N_{it} \right]$$

and may be used to estimate the density of interface states.

#### 2.7 Environmental and Electrical Stability in OTFT

#### 1.2.1 Effect of RH and Temperature

OTFTs that are environmentally stable are of great importance for the development of functioning circuits. Exposure of an OTFT to ambient atmosphere leads to degradation in the device performance. In general, device degradation is manifest as a shift in  $V_{ON}$  and  $V_T$ , reduction in  $\mu$ , increases in  $I_{off}$  and SS and the appearance of hysteresis in device characteristics. Risteska et al [40] showed that in a pentacene-based device, the presence of oxygen, O<sub>2</sub>, during bias stress induce shifts in  $V_{ON}$  due to formation of acceptor-like states. Chabinyc et al [41] found that ozone, O<sub>3</sub>, caused a shift in  $V_{ON}$  for OTFTs based on P3HT. However, this is not the case for DNTT. Patchett et al [3] showed that exposure to ambient air for 48 hours stabilized and improved the device performance.

Several reports investigated the effect of moisture on TFT performance. Hoshino et al [42] found that moisture increased  $I_{off}$  while Chabinyc et al [43] showed that moisture reduced  $\mu$ . Noh et al [44] showed the presence of hysteresis in pentacene OTFTs based on polar insulators such as polyvinylpyrrolidone (PVP) and poly(methyl methacrylate) (PMMA) upon exposure to moisture suggesting that moisture induces a polarization in the bulk insulator. However, Hong et al [45] observed hysteresis in pentacene OTFTs with a non-polar insulator such as polystyrene. Ding et al [46] observed that moisture shifts  $V_T$  and increases  $I_{off}$  in DNTT OTFTs but  $\mu$  remain unchanged. This suggests that the presence of moisture may induce charge trapping either at the insulator/semiconductor interface, in the insulator or in semiconductor causing changes in the flatband voltage. Goldmann et al [47] observed a step-like feature in the transfer characteristics of single crystal pentacene with SiO<sub>2</sub> as the insulator which was attributed to a water-related trap state in the semiconductor.

Generally, the effect of temperature on OTFTs is investigated for understanding the transport properties in the materials. However, thermal stability is also important for providing insight into degradation mechanisms for practical application. Previous reports showed that DNTT is thermally stable up to 250 °C [48]. Further investigation was carried out by Kuribara et al [49] on DNTT to demonstrate sterilization processes for medical application. However these papers only focused on applications and the detailed correlation between temperature and the device properties was not fully understood.

## 2.7.1 Effect of Bias Stress

Application of prolonged gate bias in OTFTs causes a shift,  $\Delta V_T$  of the threshold voltage with time which is known as the bias stress effect. These instabilities are explained by trapping of the mobile carriers either within the semiconductor, semiconductor/insulator interface or in the insulator. If the charges are trapped at the interface, they no longer contribute to the current and cause the interface to become more repulsive to the remaining mobile charges. Thus a higher negative (positive) gate voltage is needed to maintain the drain current. Typically, threshold voltage shifts towards the applied gate voltage. In a p-type semiconductor, a negative gate bias causes holes to be trapped which leads to the shift in the threshold voltage towards more negative voltage. Meanwhile a positive gate bias, leads to positive shifts in the threshold voltage. If hole/electron trapping occurs in the deep traps (slow states) at the interface of the semiconductor/insulator or in the insulator, the shape of the transfer characteristics and hence the carrier mobility will not change. On the other hand, if hole/electron trapping occurs within the semiconductor or in fast interface states, the shape of the transfer characteristics will be affected with deleterious effect on mobility.

The bias stress effect has been extensively studied in p-type semiconductors and much progress has been made to demonstrate that it can be as stable as  $\alpha$ -Si TFT. In the case of negative bias stress, for a pentacene/polyimide based OTFT which was annealed at 140 °C for 12 hours, Sekitani et al [50] showed good stability with  $\Delta V_T < 0.4$  V after stressing for 11 h. Zschieschang et al [9] investigated the stability of DNTT based OTFTs and observed  $\Delta V_T = 70$  mV after stressing for 66 hours. As reviewed by Sirringhaus [51], moisture is one of the important factors that cause the bias stress effect in OTFTs [47, 52]. Several techniques were used to prevent the ingress of moisture including using self-assembled monolayers [53-55] or hydrophobic dielectrics such as low-*k* Cytop<sup>TM</sup> [56, 57] to passivate the interface. Several reports had showed that, application of positive bias stress leads to a positive voltage shift [58-60]. This effect is believed to be due to electron trapping and injection at the interface or in the insulator [51]. Under illumination within the band gap of the semiconductor, this effect is significantly enhanced [46, 61-65].

It is also worth noting that in many cases, bias stress had minimal effect on the carrier mobility [66-69]. However, there are some cases reported of mobility degradation [70, 71]. This is believed to be due to trapping of electrons in states at the interface [72]. Goldmann et al [47] observed degradation in the subthreshold slope, *SS* which is reflected in a step-like feature in the transfer characteristics of single crystal pentacene with SiO<sub>2</sub> insulator. This feature was attributed to the water related trap state in the semiconductor [47, 73]. It is also known that the bias-stress effect is reversible. It can be recovered over time in the dark by grounding the source, drain and gate electrodes, or more rapidly under illumination to remove the effect of hole trapping under negative bias stress [69, 74, 75].

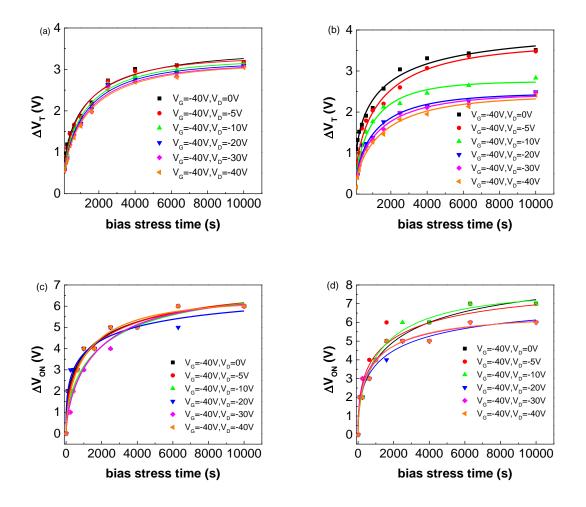

The dependence of  $\Delta V_T$  on time was quantitatively described the using stretched exponential function. Originally this model was developed to described the threshold instability in  $\alpha$ -Si:H TFTs [76]. However many researchers have used this approach for describing the threshold instability in OTFTs [68, 77-80] which is given by:

$$\Delta V_T(t) = |V_T(\infty) - V_T(0)| \left[ 1 - e^{-\left(\frac{t}{\tau}\right)^{\beta}} \right]$$

(2.10)

where  $V_T(\infty)$  is the threshold voltage after a long stress time,  $V_T(0)$  is the threshold voltage before bias stress,  $\tau$  is the characteristic trapping time for filling the trap states, while  $\beta$  is the stretched-exponential factor related to the distribution in characteristic trapping time,  $\tau$ . Mathjissen et al [80] described the time-dependence of  $\Delta V_T$  in bottom-contact OTFTs with different semiconductors including polytriarylamine (PTAA), poly(3-hexylthiophene) (P3HT) and poly(9,9'-dioctyl-fluorene-co-bithiophene (F8T2). Choi et al [81] used the stretched exponential equation to compare the performances of OTFTs based on pentacene with different molecular weight of polystyrene. This work also showed that  $\tau$  increases with molecular weight suggesting the presence of a higher trap density in low molecular weight PS. Zschieschang et al [75] investigated the effect of drain bias on the  $V_T$  stability and found that  $\Delta V_T(t)$  is well described by the stretched exponential function. The work also showed that both  $V_T(\infty)$  and  $\tau$  increase as  $V_D$  is decreases suggesting that the number of charge carriers available for trapping are greater when stressing at low  $V_D$  [82, 83]. Other than the stretched exponential function, Gomes et al [52] described the dependence of  $\Delta V_T$  on time by a stretched-hyberbola [52]. In some cases the time-dependence of  $\Delta V_T$  can be simplified to a power-law [54] or extended to a double stretched-exponential [84, 85].

The stretched-exponential function can be extended with the measurement of drain current decay with time. Most authors presumes that  $V_T(\infty) = V_G$  such that  $(V_G - V_T(\infty)) = 0$ , i.e. when the gate field becomes insufficient to sustain an accumulation channel of free holes.[19, 86-88]. Based on this assumption Zhang et al [86] developed the extended model of the stretched exponential function based on drain current in the form of:

$$I_D(t)/I_D(0) = exp\left(-\frac{t}{\tau}\right)^{\beta}.$$

(2.11)

The model was based on measuring current in the saturation regime, but the square term seems to be missing from the entire equation (see section 2.6.3) which may be an editorial error. To date only a few reports have appeared on the bias stress effect in DNTT devices. Zschieschang et al found that *SS* does not return to its original value after stressing for 24 hours [5]. Hannah et al [16] showed the stability of the device improving with longer chain length in series of alkylphosphonic acids ( $C_nPA$ ). However these papers only focused on achieving the best stability. Further studies of the bias stress effect in DNTT is essential and needs to be understood since DNTT shows excellent performance for electronic applications.

## 2.7.2 Effect of Illumination

The effect of illumination on the electrical performance as well the underlying physics of these effects are important for the development of several applications such as the backplane for display technology and photosensors. It is known that, when a device is illuminated with photons of energy equal to or higher than the band gap of the organic semiconductor a large number of excitons are generated. A fraction of these excitons will dissociate into holes and electrons. When a negative gate bias,  $V_G < 0$  V and drain bias,  $V_D < 0$  V is applied, these photogenerated holes will flow to the drain electrode, leading to an increase in the photocurrent while photogenerated electrons move away from the drain electrode and may

become trapped in localized states within the semiconductor, at the interface of the semiconductor/insulator or in the insulator.

Two mechanisms that are responsible for the change in transfer characteristics during illumination are known as the photoconduction and photovoltaic effects [89-91]. Noh et al [92] distinguished fast and slow responses in OTFTs based on pentacene and sexithiophene (6-T). The fast response was attributed to the photo-generation of holes and electrons that leads to an increase in the current through the bulk semiconductor between source and drain, also known as the photoconduction effect. The photocurrent usually dominates in the off-state of the device although some reports argue that the channel current itself is also enhanced [92-95]. The slow response was attributed to a light-induced shift in threshold voltage and leads to an increase in the channel current in the subthreshold region. This is known as the photovoltaic effect.

It has been discussed previously that the effect of hole trapping under negative bias stress could be removed by exposing the device to illumination [69, 74, 75]. Debucquoy et al [96] showed that illumination accelerates  $\Delta V_T$  under positive bias stress. A similar effect was also observed by Taylor et al [65] using a MIS capacitor structure. Recently, phototransistors based on DNTT have been reported by Milvich et al [97], Yu et al [98] and Chu et al [99]. However these papers only focused on photosensor applications. The detailed correlation between light parameters and the device performance is not fully understood. Although the effect of light on organic semiconductors has been reported by many authors [54, 91, 94], there are no reports specifically describing electro-optical effects in DNTT devices.

## 2.8 Summary

This chapter presented the fundamental properties of organic semiconductors and the basic operation of OTFT. A procedure for the extraction of OTFT device parameters including density of state was also explained. Environmental and bias stress stability of OTFT were reviewed. Lastly the effect of illumination on OTFTs were also discussed. From the foregoing, DNTT is an excellent candidate for organic circuit applications. However, more needs to be understood about the stability of OTFTs based on DNTT. Accordingly, the

following chapters report a detailed study on environmental, bias stress and optical stability of OTFTs based on DNTT as the semiconductor and polystyrene as the gate insulator.

# **3** Experimental Details

#### 3.1 Introduction

This chapter presents details of the materials and methods used in this work. The semiconductor and the insulator materials are introduced first and followed by a description of the processes used to fabricate the transistor test devices. Finally, the characterization procedures followed in the bias stress and phototransistor measurements are described.

## 3.2 Materials

In this work, dinaphtho[2,3-b:2',3'-f]thieno[3,2-b]thiophene (DNTT) was used as the semiconductor material while polystyrene (PS) was used as the gate insulator. Figures 3.1(a) and (b) show the molecular structures of DNTT and PS. DNTT was synthesized by Dr. J. Morrison at Manchester University following the same route as published by Yamamoto and Takimiya [17]. PS with an average molecular weight,  $M_W$  of ~ 350,000 was purchased from Sigma Aldrich. Flexible polyethylene naphthalate (PEN) substrates were purchased from DuPont Tenjin.

Figure 3.1 Molecular structures of (a) DNTT and (b) PS.

#### 3.2.1 Preparation of the PS Solution

A 9% wt/wt solution of PS in toluene was prepared in the clean room at room temperature. PS pellets were dissolved into the toluene in a pre-cleaned glass vial. Vials were cleaned following the same methods as described above for the substrates. The resulting solution was sonicated until the PS was fully dissolved. Finally, the solution was filtered with a  $0.2 \,\mu m$  PTFE syringe filter and stored inside a fridge in the cleanroom when not in use.

#### 3.2.2 Substrate Cleaning Procedure

The PEN substrates were cut into 6.5 cm x 6.5 cm squares to fit with the shadow masks. They were then placed in a beaker filled with Decon 90 /deionized water and sonicated in an ultrasonic bath for 10 minutes. After rinsing with deionized water the substrates were dried in a stream of nitrogen gas. The substrates were then given final rinses in deionized water, acetone, methanol and 2-propanol and again dried with nitrogen gas.

## **3.3** Device Fabrication

The device structure of bottom-gate top-contact PS-DNTT OTFTs used in this work is shown in Figure 3.2. Devices were fabricated using the same mask set as described by Patchett et al [3, 100]. The mask comprised of 18 x 5 array of 90 transistors as shown in Figure 3.3. Two blocks of 9 OTFTs were arranged in 5 rows. In each row the channel length, *L* increased in step from 50  $\mu$ m to 200  $\mu$ m. The block in the left-hand side has a width, *W* of 2 mm with aspect ratio, *W/L* ranging from 40 to 10. The right-hand side block had a constant *W/L* ratio of 20, yielding a width ranging from 1 mm in the first row to 4 mm in the fifth row. Five circular capacitors with a diameter of 2 mm were arranged diagonally across the substrate in order to extract the capacitance per unit area of the gate dielectric.

**Figure 3.2** Structure of bottom-gate top-contact of PS-DNTT OTFT fabricated on PEN substrate where *L* and *W* are the channel length and width respectively.

Only OTFTs with  $L=150 \,\mu\text{m}$  or 200  $\mu\text{m}$  and W=2mm were used in this work. The fabrication of bottom-gate top-contact PS-DNTT OTFTs was undertaken in a nitrogen glovebox (Glovebox Technology Ltd) with an integrated, computer-controlled, multisource evaporator (Kurt Lesker Ltd) with pre-programmed evaporation rates and quartz crystal thickness monitors. Firstly, a 70-nm thick aluminium film was deposited onto the PEN substrate by thermal evaporation through the gate shadow mask to define the gate electrodes. PS was spincoated onto the metallized substrate from the toluene solution at 1000 rpm for 60 s. The substrate was then placed on a hot-plate for 10 minutes at 100 °C to dry off any remaining solvent. The resulting film was ~1  $\mu$ m thick as determined by AFM measurement with a measured dielectric constant ~2.6. A 70-nm thick DNTT film as measured from the quartz crystal in the deposition chamber was then deposited onto the PS by thermal evaporation through a shadow mask to define the area of the semiconductor. Finally, 60-nm thick gold was deposited by thermal evaporation through the source-drain shadow mask to complete the devices. A photograph of the actual device is shown in Figure 3.4(a).

**Figure 3.3** Mask features 18 x5 arrays of 90 transistors with 5 circular capacitors of 2mm diameter arranged diagonally across the substrate. Source and drain contacts are depicted in red, gate contacts in blue and semiconductor in green (adapted from [100]).

## 3.4 Transistor Characterization

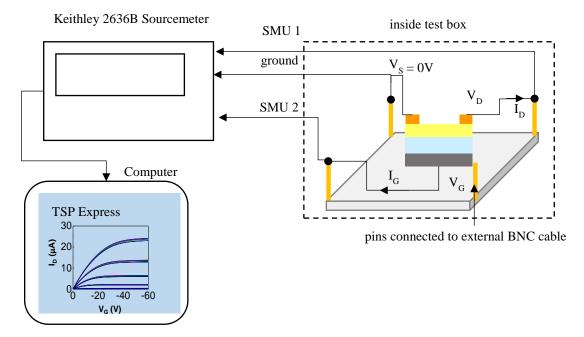

Transistor characterization was performed using a source/measure unit (Keithley model 2636B). All measurements and data acquisition were automated using TSP<sup>TM</sup> Express software through a LAN connection. Transistor characterization was undertaken with two different arrangements. In Chapters 4 and 5, the test device was placed in an aluminium test box while in Chapters 6 and 7 devices were placed in a cryostat. Details of the transistor characterization setup for Chapter 6 and 7 will be described in section 3.6. For environmental and bias stress measurements (Chapter 4 and 5), the transistor was placed inside a grounded metal test box (Figure 3.4(b)) with dimensions of 11.7 cm x 9.2 cm x 2.8 cm. The OTFTs were mounted on a PTFE block fixed to the base of the box and connections made with gold wire and silver paste from the gate, source and drain electrodes to gold pins fixed into the block. Connections were made from the pins to BNC connectors and thence via tri-axial cables to the source-measure unit.

Figure 3.4 Photograph of the (a) actual PS-DNTT OTFTs and (b) aluminium test box.

The schematic diagram of the transistor characterization setup shown in Figure 3.5 is relevant to Chapter 4 and 5. For environmental testing, measurements were conducted in the dark inside an artificial climate chamber (CLIMACELL) to control the humidities ( $20\% \ge RH \le 80\%$ ) and temperatures ( $10 \ ^{\circ}C \ge T \le 90 \ ^{\circ}C$ ). The test device was placed inside the box without a lid and was held at the set conditions for 30 min to allow the device to come into equilibrium

with the test environment. For the bias stress tests under controlled conditions (humidity and temperature), measurements were conducted inside the CLIMACELL while others were conducted at room temperature in ambient air. Both measurements were conducted in the dark. Thus for the ambient environment, the tested device was placed inside the box with a lid.

**Figure 3.5** Schematic diagram of the transistor characterization setup. Test pins were connected to BNC connector to allow connection to the SMU unit

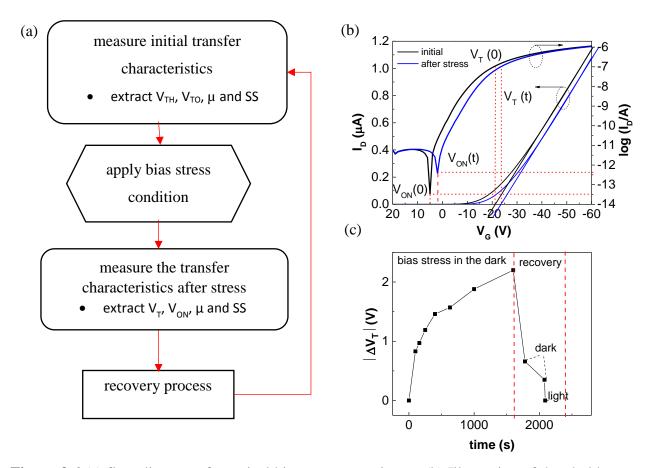

## 3.5 Bias Stress Characterization

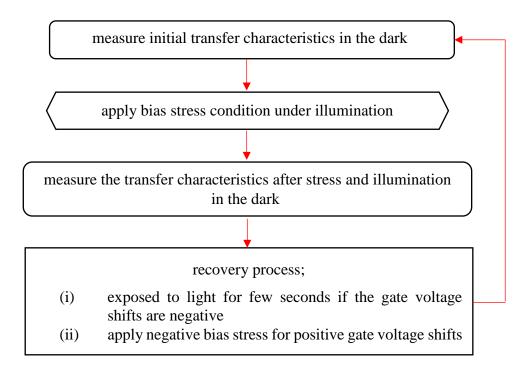

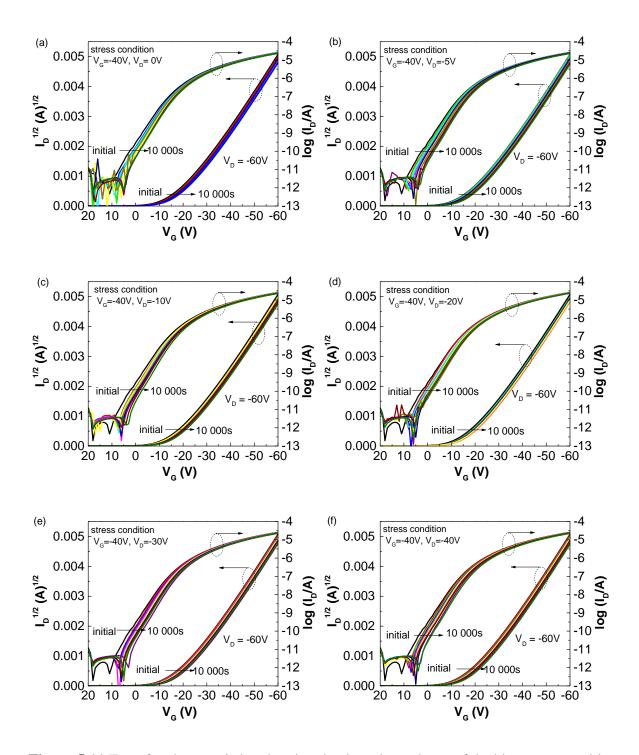

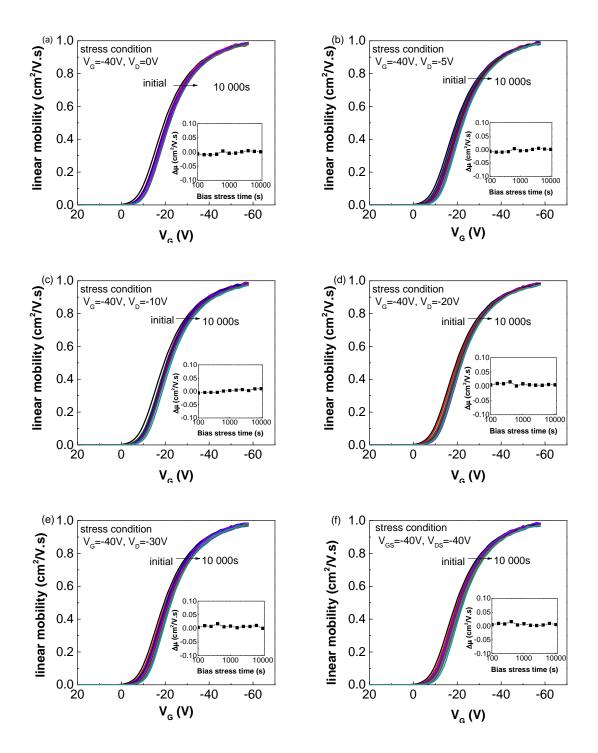

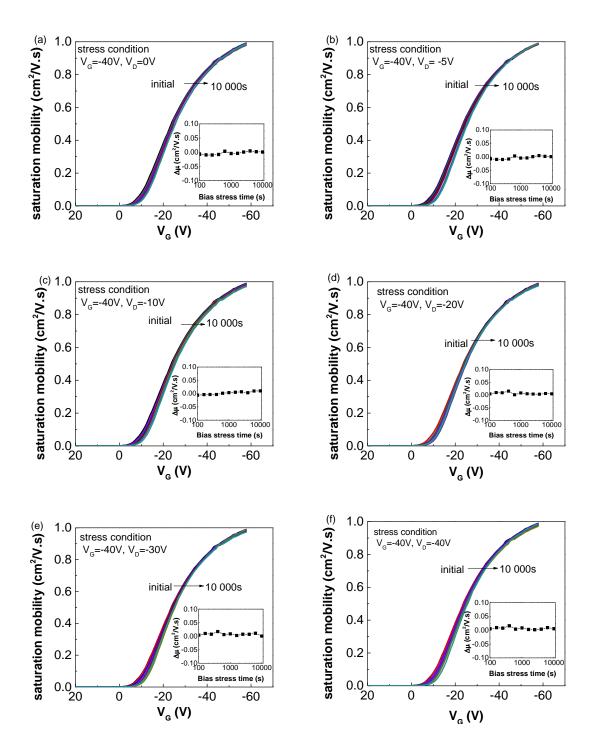

The bias stress characterization procedure described here is relevant for the studies in Chapter 5. A typical flow diagram for the bias stress experiments is shown in Figure 3.6(a). First, the initial transfer characteristic was measured. Then the device was subjected to various bias stress conditions and stress times. The bias stress was frequently interrupted to measure the output characteristics and transfer characteristics in the linear ( $V_D = -1$  V) and saturation ( $V_D = -60$  V) regimes from which the electrical parameters were extracted. Figure 3.6(b) indicates a typical transfer curve, plotted on linear and semilog scales, both in the initial state and after bias stress. The shift of threshold voltage,  $\Delta V_T$ , and turn-on voltage,  $\Delta V_{ON}$ , were determined

as  $[V_T(t) - V_T(0)]$  and  $[V_{ON}(t) - V_{ON}(0)]$  respectively, where *t*=0 corresponds to pre-stress values.